Изобретение относится к области цифровой вычислительной технике и предназначается для использования в составе цифровой вычислительной машины (ЦВМ).

Известны арифметические устройства (АУ) параллельного действия, содержащие регистры множителя (частного), множимого (делителя), накапливающий регистр и схемы полусумматоров.

В известных устройствах регистры множителя (частного) и накапливающий регистр выполняют следующие основные пересылочные элементарные операции (ЭО): прием и хранение кода; выдачу кода в другие регистры; сдвиг кода в сторону младших и старших разрядов.

Выполнение п-го числа 30 иад кодом, хранящимся в регистре, можно осуществить с помощью двух вентилей и схемы нарафазного управления этими вентилями. Схема нарафазного управления или схема парафазного приема кода состоит из логических элементов типа «И по числу выполняемых элементарных операций, схемы сборки «ИЛИ и инвертора. Выходы схемы сборки и инвертора управляют потенциальными входами нулевого и единичного вентилей триггера регистра. На импульсные входы этих вентилей одновременно поступают исполнительные импульсы.

Недостатком такого устройства является большой объем оборудования.

Цель изобретения - сокращение оборудования и повышение надежности работы устройства.

Для достижения этой цели в предлагаемом арифметическом устройстве входы установки нуля триггеров t-ro разряда каждого регистра через вентили соединены с выходом логического элемента «ИЛИ схемы парафазного приема кода г-го разряда; входы установки единицы триггеров г-го разряда каждого регистра через вентили соединены с выходом логического элемента «НЕ схемы парафазного приема кода г-го разряда; выход триггера t-ro разряда накапливающего регистра соединен со входами первого элемента «И (i-1)-го разряда и четвертого эле Мента «И )-го разряда схемы парафазного приема кода; вьь

ход триггера г-го разряда регистра множителя соединен со входами второго элемента «И (г-1)-го разряда и третьего элемента «И (/-|-1)-го разряда схемы парафазного приема кода.

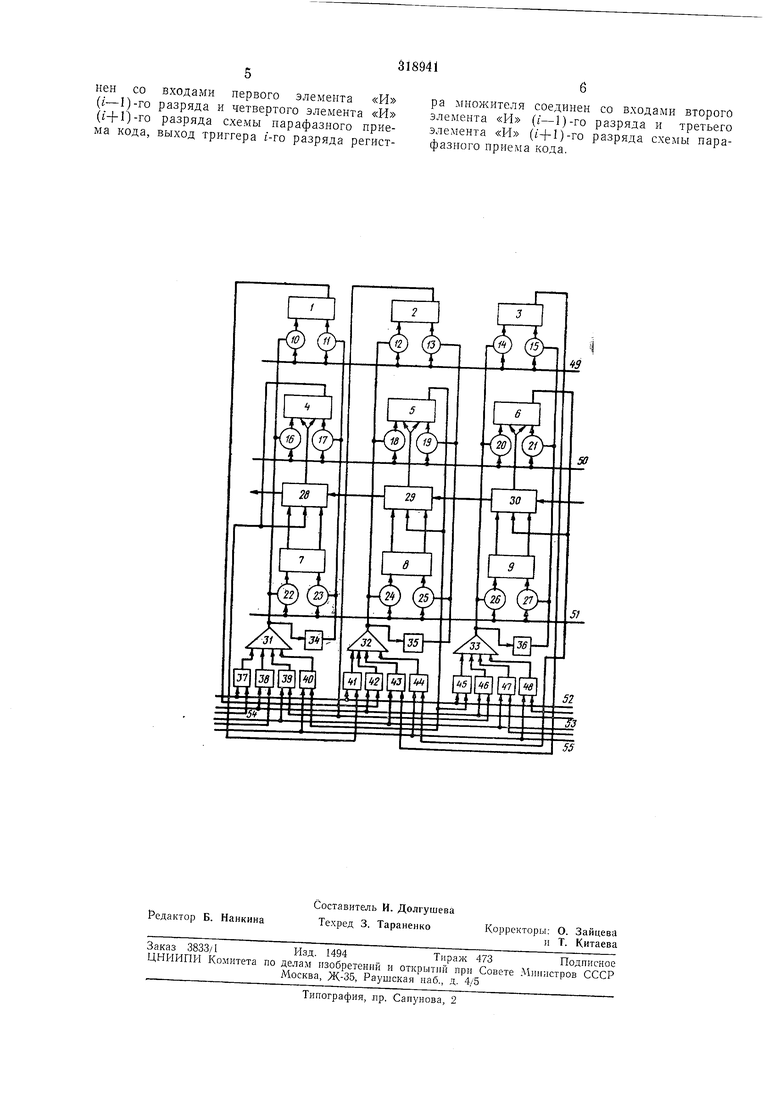

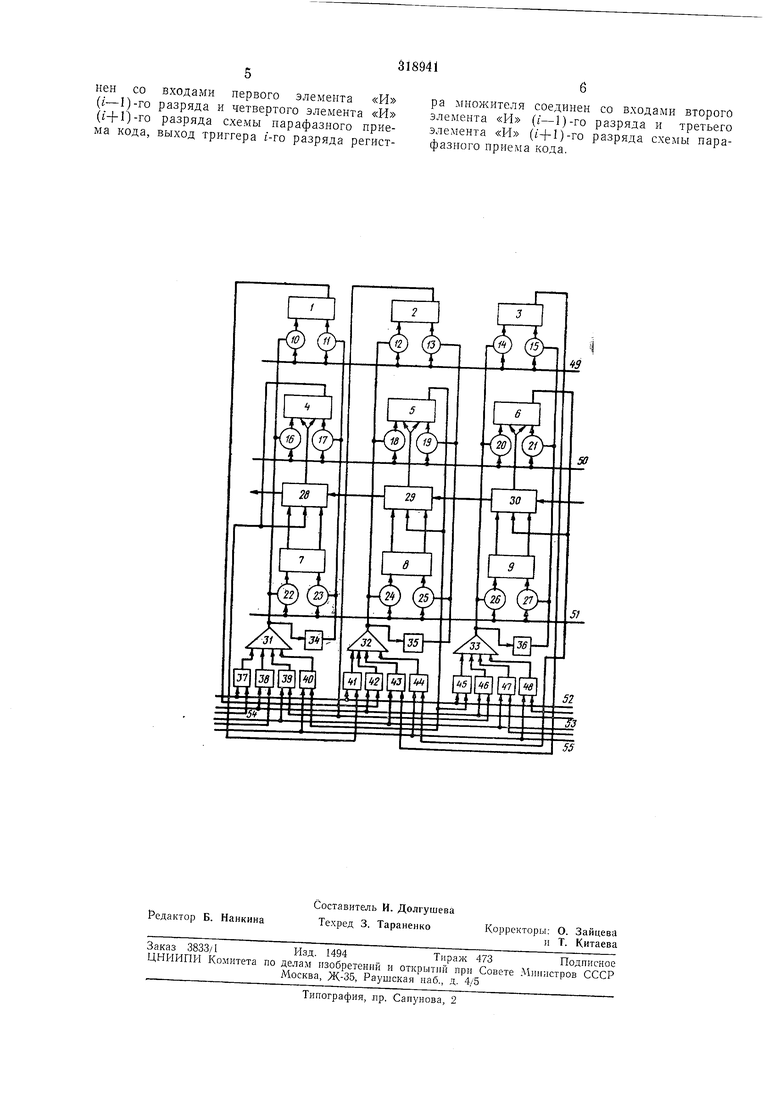

На чертеже приведена функциональная схема трех разрядов арифметического устройства, на которой изображены:

34-36 - инверторы («НЕ); 37-48 - схемы совпадения («И); 49 - шина приема информации в регистр множителя; 50 - шина приема информации в накапливающий регистр; 51 - шина приема информации в регистр множимого; 52 - шина разрешения сдвига кода накапливаюш,его регистра вправо; 53 - шина разрешения сдвига кода регистра множителя вправо; 54 - шина разрешения сдвига кода регистра множителя влево; 55 - шина разрешения сдвига кода накапливающего регистра влево.

Рассмотрим связи между отдельными узлами и схемами арифметического устройства на примере i-ro разряда арифметического устройства.

Как видно из чертежа, потенциальные входы вентилей 12, 18, 24 подключены к выходу схемы сборки 32. Потенциальные входы вентилей 3, 19, 25 подключены к выходу инвертора 55. Схемы совпадения 41-44 предназначены для разрешения выполнения элементарных операций в арифметическом устройстве. Входы этих схем совпадения подключены к шинам 52-55. Вторые входы этих схем соедипены с выходами триггеров 4, 1, 3 6 соответственно.

Выходы схем совпадения 41, 42, 43, 44 подключены к схеме сборки 32. Выход схемы сборки 32 подключен ко входу инвертора 35.

Импульсные входы вентилей 10-15 подключены к шине 49, по которой поступает исполнительный импульс.

Вентили 16-21 и 22-27 подключены к шинам 50 и 51 соответственно.

Выходы схем полусумматоров 28-30 подключены к счетным входам триггеров 4, 5, 6 регистра сумматора. Кроме того, выход схемы полусумматора 30 подключен ко входу полусумматора 29 и т. д.

Рассмотрим; работу устройства на примере зынолнения операции умножения, так как эта операция содержит большое число ЭО, выполняемых арифметическим устройством.

Перед выполнением непосредственно умножения код числа, хранящегося в накапливающем регистре, пересылается в регистр множителя. Для пересылки кода по шипе 52 подается разрешающий потенциал, на вентили 10-15 поступает исполнительный импульс. Если в триггере 5 хранился код «единицы, то с выхода схемы совпадения 45 на схему сборки 33 поступит потенциал, который запретит прохождение исполнительного импульса через вентиль 14. Вентиль 15 (единичный вход триггера 5) будет открыт, так как потенциал со схемы сборки поступает на вход инвертора 36 и открывает этот вентиль. Исполнительный импульс, поданный на шину 49, занесет код накапливающего регистра в регистр множителя со сдвигом на один разряд вправо. После пересылки кода выполняется установка накапливающего регистра в нулевое состояние. Для этого на шину 50 подается импульс. Так как вентили 17, 19 и 21

закрыты, а вентили 16, 18 и 20 открыты, то иснолнительным импульсом триггеры 4, 5, 6 будут установлены в нулевое состояние.

Множитель принимается в регистр множителя с числовых шин. Для упрощения чертежа логические элементы «И, обеспечивающие прием кода с числовых щин, не приводятся. Прием кода с числовых шин выполняется аналогично нересылке кода из одного регистра в другой.

После приема кодов множителя и множимого выполняется непосредственно умножение. Первым тактом производится анализ состояпия триггера младшего разряда регистра множителя. Если этот триггер находится в состоянии «единица, то выполняется суммирование и сдвиг регистра множителя вправо. Если триггер паходится в пулевом состоянии, то выполняется только сдвиг регистра множителя, а суммирование не производится. Вторым тактом осуществляется сдвиг кода накапливающего регистра вправо. Для выполнения этой микрооперации па шину 52 подается разрешающий потенциал, а па импульсные входы вентилей 16-21 - исполнительный импульс. Если в триггере 4 хранится код единицы, то с выхода схемы совпадения 41 на схему сборки 32 поступит потенциал. Этот нотенциал «закроет вентили 12, 18, 24, и «откроет вентили 13, 19, 25. Исполнительный импульс, поступивщий на шину 50, сдвинет код накапливающего регистра на один разряд вправо. Далее цикл работы повторяется. Аналогично выполняется и операция деления, но сдвиги в регистре множителя и регистре сумматора производятся влево. Кроме того, код регистра делителя предварительно инвертируется или выдается в схему полусумматора обратпым кодом.

Предлагаемое устройство дает экономию логических элементов в цепях управления триггерами почти в два раза по сравнению с рассмотренными вариантами для арифметического устройства, содержащего три регистра п выполняющего 10-12 элементарных операций.

Предмет изобретения

Арифметическое устройство параллельного действия, содержащее регистр множителя, накапливающий регистр, сумматор и регистр множимого со схемой парафазного приема кода, содержащей логические элементы «И, «ИЛИ, «НЕ, отличающееся тем, что, с целью сокращеиия оборудования и повышения надежности работы, в нем входы установки нуля триггеров 1-го разряда каждого регистра через вентили соединены с выходом логического элемента «ИЛИ схемы нарафазного приема кода i-ro разряда, входы установки единицы триггеров i-ro разряда каждого регистра через вентили соединены с выходом логического элемента «НЕ схемы парафазного приема кода /-го разряда, выход триггера i-ro разряда накапливающего регистра соединен совходами первого элемента «И (/-1)-горазряда и четвертого элемента «И (/+Г)-горазряда схемы парафазного приема кода,выход триггера f-ro разряда регистра множителя соединен со входами второго элемента «И (г-1)-го разряда и третьего элемента «И (i- -lJ-ro разряда схемы парафазного приема кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| УЗЕЛ СДВИГА АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 1970 |

|

SU279170A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1969 |

|

SU248778A1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Устройство для умножения | 1982 |

|

SU1123031A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

Даты

1971-01-01—Публикация