Изобретение отиосится к области вычислительной те.хиики, в частности к запоминающим устройствам цифровых вычислительны.х машин.

Известен запоминающий эле.мент, выполненный на транзистора.х со структурой металл - окисел - полупроводник (МЬП-траизисторах), содержащий триггер, нагрузочные транзисторы и транзистор считывания. Недостатком известного элемента является большое число транзисторов на единицу информации.

С целью уменьшения числа транзисторов в предложенном элементе затворы нагрузочных транзисторов соединены со стоком транзистора считывания и шинами восстановления информации и адреса, а стоки нагрузочных транзисторов подключены к разрядным шинам записи «О и «1 соответственно.

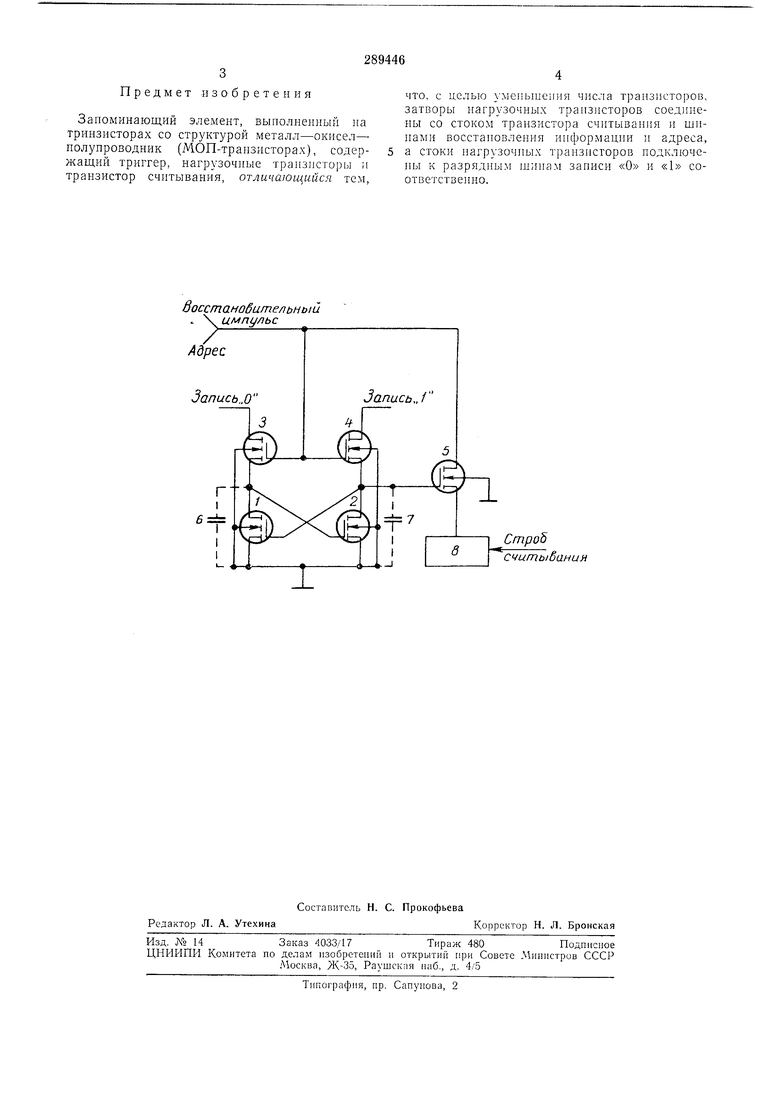

На чертеже представлена схема запоминающего элемента.

Элемент состоит из триггера, выполненного на транзисторах / и 2, нагрузочных транзисторов 3 11 4 н транзистора считывания 5.

Схема работает следующим образом.

В исходном состоянии на стоки транзисторов 3 и 4 иодается отрицательный иотенциал соответственио по цепям записи и «1. При этом ппформация хра 1нтся на е.мкостях

6 и 7, являющихся паразитными внутренннми распределеннымн емкостями схемы. Восстанавливающие нмпульсы поступают от генератора импульсов по цени восстановления инфор.мацин на адресную шину, транзисторы 3 и 4 открываются, н нотенциал на емкости, храпящей код «I, возрастает до макснмального значения, транзистор, затвор которого соединен с точкой хранения информации, открывается еще сильнее, чем обеспечивает более благоприятные условия для разряда емкости, хранящей код «О.

Считывание информации можно нроизводнть ири подаче и.мпульса напряжения на адресную щииу, стробнруя схе.му считывания 8. Запись нропсходнт путем подачи на сток одного из нагрузочных транзисторов потенциала «О. На стоке второго транзистора нрисутствует прп этом отрицательный потенциал. Таким образом, через транзистор, на стоке которого присутствует потенциал «О, емкость разряжается, а через транзистор, на стоке которого присутствует отр1щательный потенцнал, емкость заряжается, т. е. заппсь происходит парафазпо. Так как счнтываппе пропсходпт через затвор считывающего транзистора; нмеющего очень высокий входной имнеданс, информация практически не разрушается до

Предмет изобретения

Запоминающий элемент, выполненный на тринзисторах со структурой металл-окисел- полупроводник (МОП-транзисторах), содержащий триггер, нагрузочные транзисторы и транзистор считывания, отличающийся тем,

что, с целью уменьшения числа транзисторов, затворы нагрузочных транзисторов соединены со стоком транзистора считывания и шииами восстановления информаннн и адреса, а стоки нагрузочных транзнсгоров подключены к разрядным шинам записи «О и «1 соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Постоянное запоминающее устройство | 1989 |

|

SU1635219A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Запоминающее устройство | 1980 |

|

SU903981A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

босстанобительный . импульс

Адрес

Запись..О

Стро5

счить/бания

Авторы

Даты

1971-01-01—Публикация