Известно запоминающее устройство (ЗУ), содержащее адреспый накопитель, нодключенный через дешифратор « регистру адреса, ассоциативный накопитель, соединенный с шифратором, входной регистр, .подключенный « блоку управления.

В известном ЗУ .возможна пормальпая работа адресного накопителя ери отказе некоторого числа его ячеек. Это достигается благодаря резервным ячейкам ассоциативного наколителя, которые не используются при отсутствии отказов, что приводит к уменьшению фактической емкости ЗУ.

Предлагаемое ЗУ отличается от известного тем, что оно содержит сумматор, первые входы которого соединены с входным регистром, вторые входы - с шифратором, а выходы подключены к регистру адреса, и блок сравне ния кодов, первые входы которого соединены с выходами сумматора, вторые -входы -с выходами регистра адреса, а выход подключен к блОКу управления. Это позволяет увеличить емкость ЗУ.

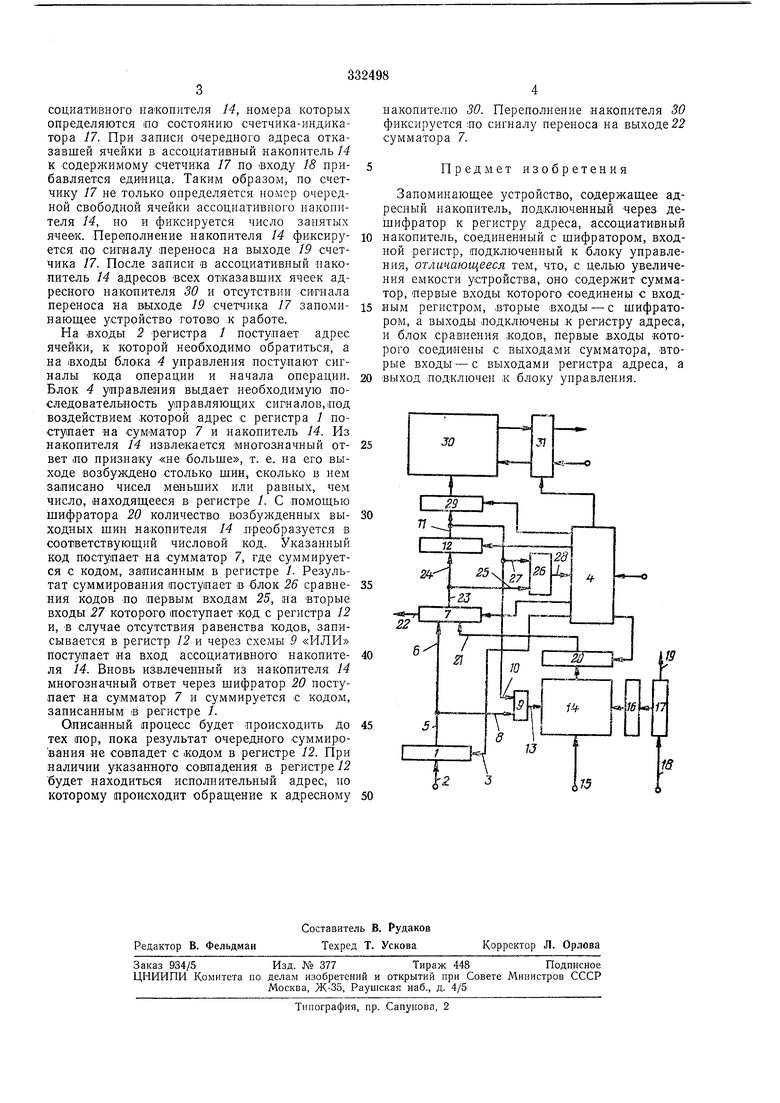

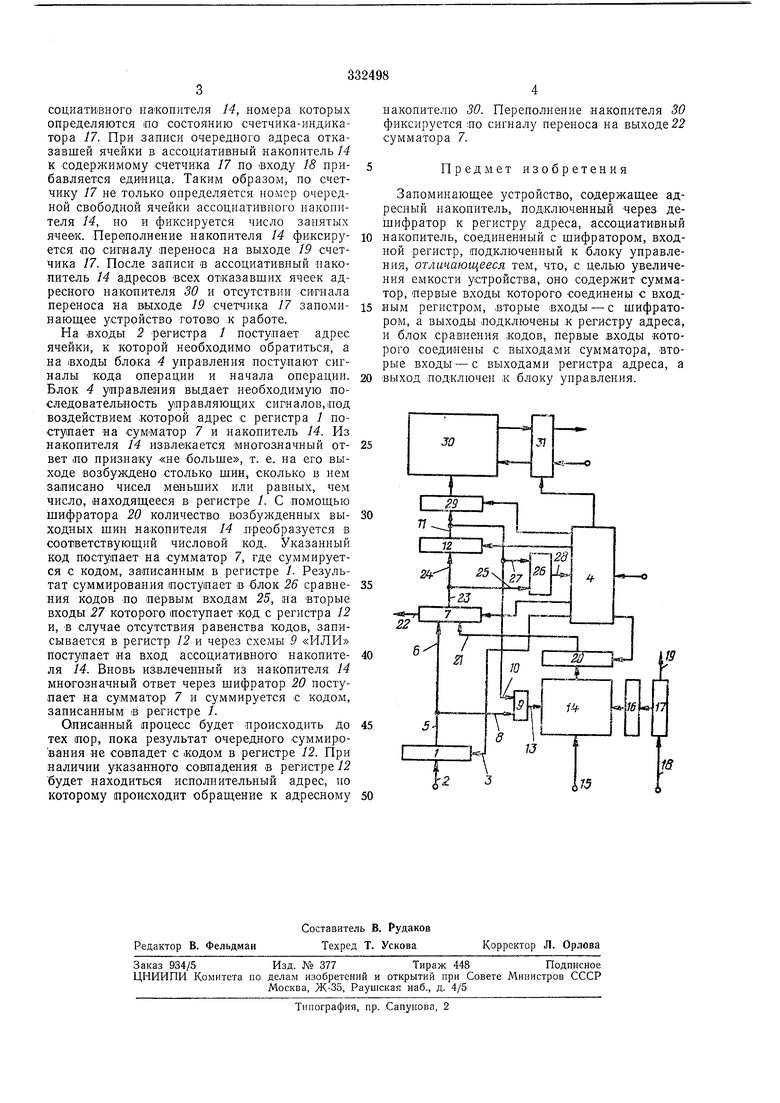

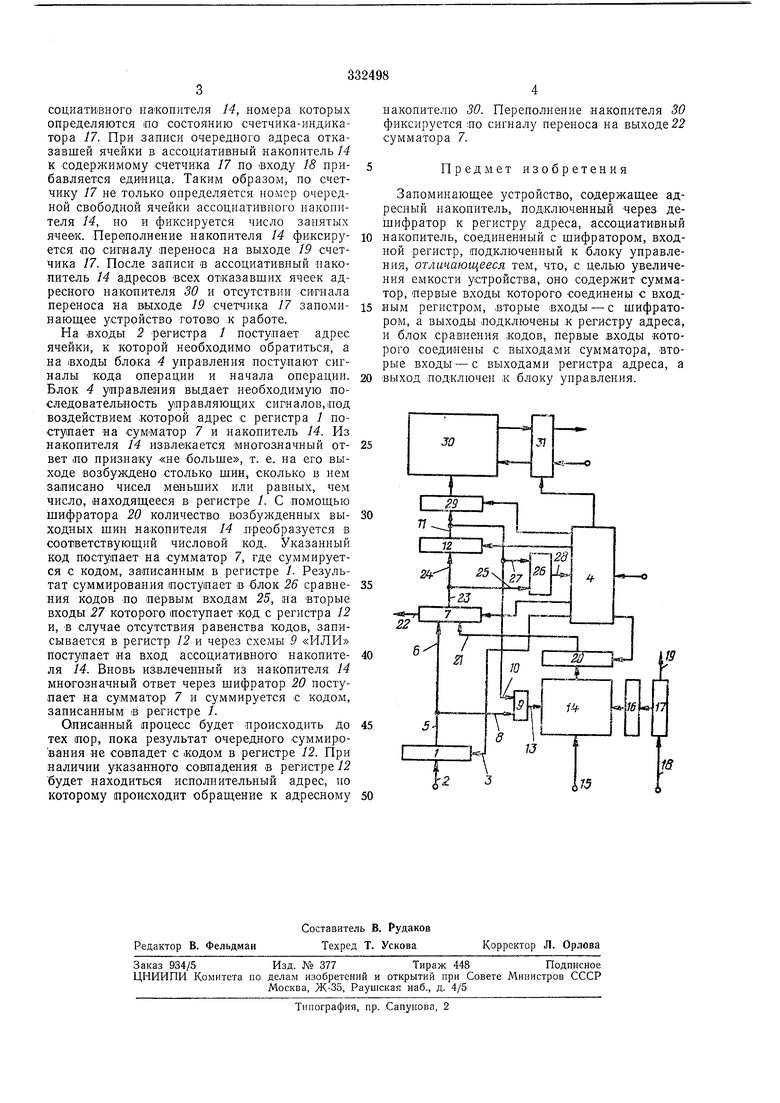

Сущность изобретения ноясняется чертежом, на котором изображена блок-схема -предложенного ЗУ.

выми входами 6 сумматора 7 и первыми входами 8 схем «ИЛИ Я вторые входы 10 которых связаны с Выходами 11 регистра 12 адреса. Выходы 13 схем «ИЛИ 9 соединены с ассоциативным накопителем 14, имеющим входы 15 записи. Ассоциативный накопитель 14 через дешифратор 16 подключен к счетчикуиндикатору 17, который содержит счетный вход 18 и выход 19 переносов со старшего разряда.

Ассоциативный накопитель 14 через шифратор 20 соединен со вторыми входами 21 сумматора 7, имеющего выход 22 переноса со старшего разряда. Вы.ходы 23 сумматора 7 соединены с информационными входами 24 регистра 12 адреса и первым) входами 25 блока 26 сравнения кодов, вторые входы 27 которого подключены к выходам регистра 12 адреса, а выход 28 - ко входу и блока 4 управления. Кроме того, выходы регистра 12 через дешифратор 29 адреса соединены с адресным накопителем 30, связанным с регистром 31 слова.

Запоминающее устройство работает следующим образом. С помощью контролирующих программ (тестов) или корректирующих кодов, или каким-либо другим способом определяются адреса отказавших ячеек адресного накопителя 30. Указанные адреса последовасоциатввного накопителя 14, номера которых определяются ос состоянию счетчика-индикатора 17. При записи очередного адреса отказавшей ячейки в ассоциативный накопитель 14 к содержимому счетчика 17 ло входу 18 прибавляется единица. Таким образом, по счетчику 17 не только определяется номер очередной свободной ячейки ассоциативного накопителя 14, но и фиксируется число занятых Ячеек. Переполнение накопителя 14 фнксируется по сигналу переноса на выходе 19 счетчика 17. После записи в ассоциативный иакопитель 14 адресов всех отказавших ячеек адресного накопителя 30 и отсутствии сигнала переноса на выходе 19 счетчика 17 запоминаюшее устройство готово к работе. На входы 2 регистра 1 поступает адрес ячейки, к которой необходимо обратиться, а на входы блока 4 управления поступают сигналы кода операции и начала операции. Блок 4 управления выдает необходимую последовательность управляюших сигналов,под воздействием которой адрес с регистра 1 поступает на сумматор 7 и наконитель 14. Из накопителя 14 извлекается многозначный ответ по признаку «не больше, т. е. на его выходе возбуждено столько шин, сколько в нем записано чисел меньших или равных, чем число, находящееся в регистре /. С помощью шифратора 20 количество возбужденных выходных шин накопителя 14 преобразуется в соответствующий числовой код. Указанный код ноступает на сумматор 7, где суммируется с кодом, записанным в регистре /. Результат суммирования поступает с блок 26 сравнения кодов по первым входам 25, на вторые входы 27 которого поступает код с регистра 12 и, в случае отсутствия равенства кодов, записывается в регистр 12 и через схемы 9 «ИЛИ поступает на вход ассоциативното накопителя 14. Вновь извлеченный из накопителя 14 многозначный ответ через шифратор 20 поступает на сумматор 7 и суммируется с кодом, записанным s регистре /. Описанный процесс будет происходить до тех пор, пока результат очередного суммирования не совпадет с кодом в регистре 12. При наличии указанного совпадения в регистре ./2 будет находиться исполнительный адрес, по которому (Происходит обращение к адресному накопителю 30. Перенолнение накопителя 30 фиксируется :по сигналу переноса на выходе22 сумматора 7. Предмет изобретения Запоминающее устройство, содержащее адресный накопитель, подключенный -через дешифратор к регистру адреса, ассоциативный накопитель, соединенный с шифратором, входной регистр, оодключенный к .блоку управления, отличающееся тем, что, с целью увеличения емкости устройства, оно содержит сумматор, первые входы которого соединены с входным регистром, вторые входы -с шифратором, а выходы подключены к регистру адреса, и блок сравнения кодов, первые входы которого соединены с выходами сумматора, вторые входы -с выходами регистра адреса, а выход подключен к блоку управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU926717A1 |

| Запоминающее устройство | 1972 |

|

SU437127A1 |

| Запоминающее устройство с самоконтролем | 1977 |

|

SU720516A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

Даты

1972-01-01—Публикация