(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании и создании блоков памяти ЭВМ, выполненных на функциональных узлах с большой степенью интеграции.

Известно запоминающее устройство с автономным контролем, содержащее адресный накопитель, ассоциативный и дополнительный накопители с адресными и разрядными цепями. В этом ЗУ отказавшая ячейка адресного накопителя подменяется ячейкой дополнительного накопителя, а адрес такой ячейки хранится в ассоциативном накопителе 1.

Недостатком известного такого ЗУ является то, что .уже при единственном отказе в ячейке адресного накопителя необходима другая ячейка дополнительного накопителя.

Наиболее близким по техническому рей1ению к предложенному является запоминающе,е устройство с автономным контролем, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один из входов которого соединен с первым входом адресного блока памяти, блок управления, выходы которого подключены к управляющим входам ассоциативных блоков памяти, первый и второй коммутаторы и дешифратор, причем входы первого коммутатора подключены соответственно к первому

выходу дешифратора и к выходу адресного блока памяти, а выход - к другому входу второго ассоциативного блока памяти, выходы которого соединены с входом дешифратора и одним из входов второго коммутатора, другой вход которого подключен к второму входу дешифратора, а выход - к второму входу адресного блока памяти 2. В этом устройстве при обнаружении отказа в какой-либо ячейке блок управления определяет кратность ошибки и .в зависимости от характера отказа адрес неработоспособной ячейки и номера отказавших разрядов фиксируются во втором ассоциативном блоке памяти или адрес неработоспособной ячейки записывается в аргументной

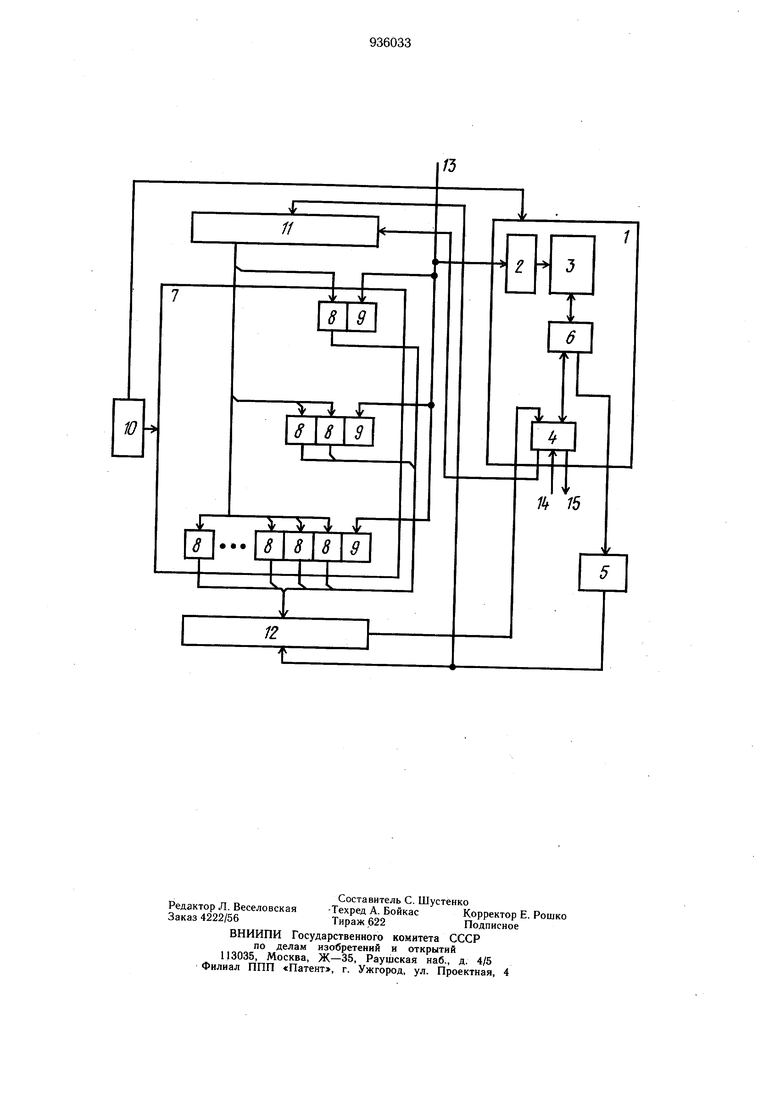

20 части первого ассоциативного блока памяти. Недостатком известного устройства является его сложность для .реализации двух ассоциативных блоков памяти, а таКже большое число дополнительных разрядов во втором ассоциативном блоке памяти для хранения номеров отказавших разрядов. Кроме того, в первом ассоциативном блоке памяти часть разрядов используется для хранения информации работоспособных разрядов адресного блока памяти, так как если количество неработоспособных разрядов ячейки основного блока памяти больше т, где m определяют из неравенства ш (1 + 1о§2п), (п - количество разрядов слова), то эта ячейка полностью подменяется ячейкой первого ассоциативного блока памяти. Цель изобретения - упрощение устройПоставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее ассоциативный накопитель, одни информационные входы которого подключены к выходам первого коммутатора, выходы - к одним входам второго коммутатора, а другие информационные входы ассоциативного накопителя подключены к входам адресного блока и являются адресными входами устройства, матричный накопитель, адресные входы которого подключены к выходам адресного блока, а информационные входы-выходы - к одним входам-выходам усилителей записи-считывания, первый регистр слова, входы-выходы которого подключены к другим входам-выходам усилителей записи-считывания, одни выходы второго коммутатора подключены к одним входам первого регистра слова, другие входы которого являются информационными входами устройства, одни входы первого коммутатора подключены к одним выходам первого регистра слова, другие выходы которого являются выходами устройства, блок управления, введены второй регистр слова, входы которого подключены к выходам усилителей записи-считывания, а выходы - к другим входам первого и второго коммутаторов. На чертеже изображена блок-схема изобретения. Устройство содержит адресный блок памяти 1, состоящий из адресного блока 2, матричного накопителя 3, первого регистра 4 слова, второй регистр 5 слова, усилители 6 записи-считывания, ассоциативный накопитель 7, который имеет функциональную часть 8 для размещения содержимого отказавщих разрядов и аргументную часть 9 для запоминания отказавших ячеек адресного блока памяти. Выход блока .управления 10 подключен к управляющим входам адресного блока памяти 1 и ассоциативного блока памяти 7, входы первого коммутатора 11 подключены соответственно к выходам регистров 4 и 5, а выход - к входу ассоциативного блока памяти 7. Выход ассоциативного накопителя 7 соединен с входом второго коммутатора 12, другой вход которого подключен к выходу регистра 5 слова, а выход - к входу регистра 4. Кроме того, вход регистра 5 слова соединен с выходом ус.нлителей 6 записи-считывания. Адрес на адресные входы 13 устройства, записьшаемое слово - на информационные входы 14, а считываемое - на информационные входы 15. Устройство работает следуюшим образом. В паузах между внешними обраш,ениями блок 10 управления производит контроль исправности ячеек адресного блока памяти 1. При обнаружении неисправности в какойлибо ячейке блок 10 управления определяет кратность ошибки и записывает адрес неисправности ячейки в аргументную часть 9 ассоциативного накопителя 7, причем кратность ошибки соответствует количеству разрядов функциональной части 8. При обращении к запоминающему устройству по адресу, установленному на входах 13, происходит одновременное обращение как к адресному блоку 1, так и к ассоциативному йакопителю 7. При выполнении записи данные с входов 14 поступают на регистр слова 4, и далее прямой код этого слова через усилители 6 записи-считывания заносится в матричный накопитель 3 по адресу, зафиксированному в адресном блоке 2. Если при ассоциативном поиске накопителя 7 не обнаружен адрес, совпадающий с содержимым блока 2, то в блок 2 поступает новый адрес и осуществляется запись очередного слова. Если же при ассоциативном поиске в накопителе 7 обнаружен адрес обращения, то записываемое слово поступает также на коммутатор 11. Далее происходит считывание из матричного накопителя 3 записанного слова на регистр 5 слова, реализованного на триггерах со счетным входом. Затем происходит запись с регистра 4 слова обратного кода того же числа в матричный накопитель 3 и считывание обратного кода на регистр 5 слова, причем сигналы с усилителей 6 записи-считывания поступают на счетные входы триггеров регистра 5 слова. Таким образом, в каждом разряде регистра 5 слова происходит суммирование по модулю два значения разряда записываемого слова. При отсутствии отказавщих разрядов в ячейке накопителя 3 значения всех разрядов регистра 5 будут равны единице. В разрядах регистра, соответствующих отказавшим разрядам ячейки накопителя 3, будут записаны нули. Сигналы с выходов этих разрядов поступают на вход коммутатора 11, и в функциональную часть 8 накопителя 7 заносятся истинные значения разрядов записываемого слова, соответствующих неисправным разрядам ячейки, а в матричный накопитель/ 3 записывается снова прямой .код слова УС регистра 4 слова.

В режиме чтения по адресу, находящемуся в адресном блоке 2, происходит выборка содержимого ячейки матричного накопителя 3 на регистры 4 и 5 слова через усилители 6. Одновременно происходит ассоциативный поиск аналогичного адреса в накопителе 7. При отсутствии сравнения адресов значение слова на регистре 4 слова считается истинным и поступает на выходы 15.

Если в накопителе 7 есть искомый адрес, то по тому же самому адресу осуществляется запись- обратного кода слова с инверсных выходов регистра 4 и считывание его на регистр 5 слова через усилители 6. Причем при считывании обратного кода сигналы с усилителей 6 записи-считывания поступают на счетные входы регистра 5. Вновь происходит суммирование по модулю два значений поступающих сигналов и значений разрядов регистра 5. Таким образом, значения разрядов регистра, соответствующих отказавшим разрядам ячейки, равны нулю. Сигналы с выходов этих разрядов поступают на коммутатор 12 н управляют выдачей содержимого функциональной части 8 ассоциативного накопителя 7 на соответствующие разряды регистра 4 слова. Истинное значение считанного слова выдается .на выходы 15.

Таким образом, в предлагаемом устройстве не требуется дополнительных разрядов для запоминания номеров отказавщих разрядов, в ассоциативном блоке памяти хранится содержимое только-неисправных разрядов блока памяти. Кроме того, в устройстве отсутствует второй ассоциативный блок памяти и дешифратор.

Формула изобретения Запоминающее устройство с автономным контролем, содержащее ассоциативный накопитель, одни информационные входы которого подключены к выходам первого коммутатора, выходы - к одним входам второго коммутатора, а другие информационные входы ассоциативного накопителя подключены к входам адресного блока и йвляются адресными входами устройства, матричный накопитель, адресные входы которого подключены к выходам адресного блока, а информационные входы-выходы - к одним входа м-выходам усилителей записи-считывания, первый регистр слова, входы-выходы которого подключены к другим входам-вы5 ходам усилителей записи-считывания, одни выходы второго коммутатора подключены к одним входам первого регистра слова, другие входы которого являются информационными входами устройства, одни входы первого коммутато 5гг подключены к одним выходам первого регистра слова, другие выходы которого являются выходами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит второй регистр слова, входы которого подключены

5 к выходам усилителей записи-считывания, а выходы - к другим входам первого и второго коммутаторов.

Источники информации, принятые во внимание при экспертизе

1.Самофалов К. Г. и др. Структурно0 логические методы повышения надежности

ЗУ. М., «Машиностроение, 1976, с. 84.

2.Авторское свидетельство СССР по заявке № .2600719/18-24, кл. G 11 С 29/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Запоминающее устройство с исправлением информации в отказавших разрядах | 1986 |

|

SU1317487A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

Авторы

Даты

1982-06-15—Публикация

1980-05-05—Подача