1

Изобретение относится к электронике, в частности к вьпшслителъной технике, и предназначено для применения в интегральных цифровых схемах

Цель изобретения - повышение быстродействия устройства при обращении за счет уменьшения временных интервалов запись-считьшание и счи- тьшание-считывание и снижения потребляемой мощности,

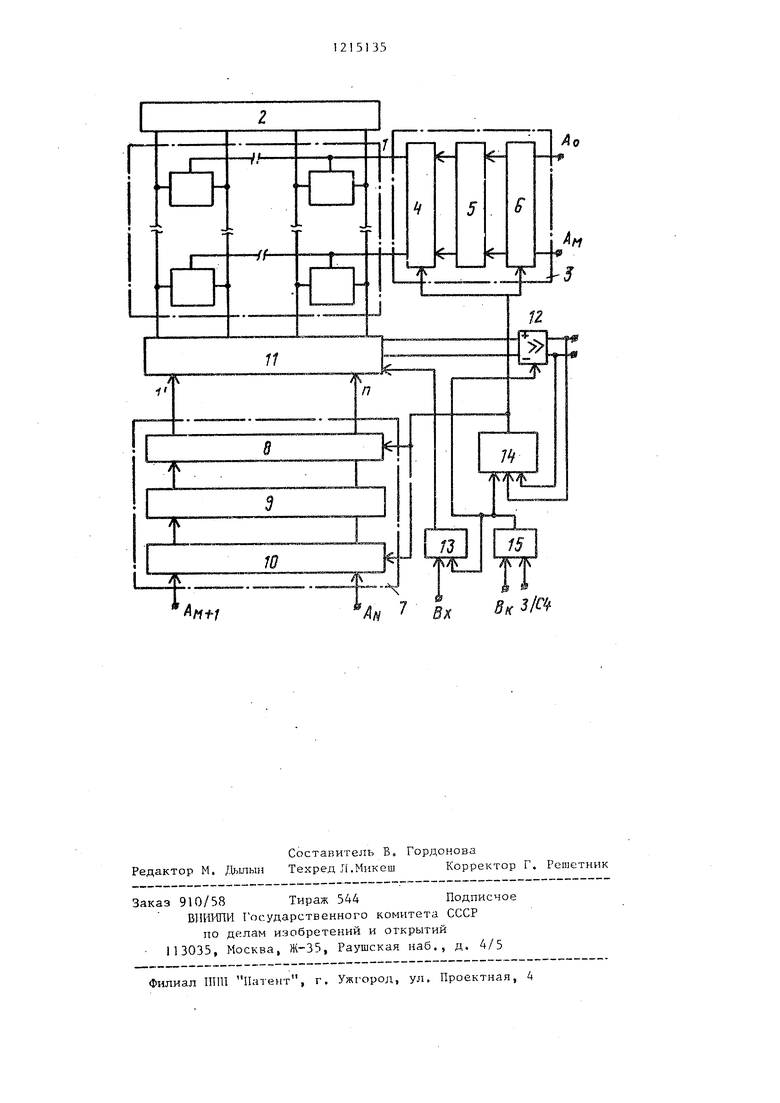

На чертеже изображена блок-схемой предлагаемого устройства.

Схема содержит матричный накопитель 1, блок предзаряда разрядных шин 2, адресный блок выборки строк 3, состоящий из стробируемого формирователя 4, дешифратора строк 5, регистра адреса строки 6, адресный блок выборки столбца 7, в-клгочающий в себя стробируемый формирователь 8 дешифратор столбцов 9, регистр адреса столбца 10, блок коммутации столбцов 11, усилитель считывания, запоминающий считываемую информацию из накопителя в течение времени вра- щения к схеме 12, формирователь входного сигнала 13, блок фиксации считываемого сигнала 14, блок управления 15,

Устройство работает следующим образом.

При уровне сигнала ВК, соответствующем невыбранному состоянию схемы (режим хранения), производится предварительный заряд разрядньпс шин накопителя. При этом принимается адресный код, установленный на внешних входах регистрами 6 и 10.

Изменение уровня на входе ВК переводит схему в режим записи и считывания в зависимости от уровня сигнала на входе Запись - считывание.

Поскольку в современных схемах оперативных ЗУПВ на МОП-транзистора цикл считывания превышает цикл записи, основное внимание в изобретении направлено на уменьшение длительности цикла считывания, В режиме счи- 1ътания сигнал с выхода блока уп- равления 15 подается на вход блока фиксации 14 и усилитель считьгоания 12, переводя последний в рабочее состояние.

Сигнал с выхода блока фиксации 14 переводит регистры 6 и 10 в режи хранения принятого кода адреса и стробирует Формироиатели 4 и 8, ко2I51

,,

5 О

15 20 25

30

г

Q

.,

55

35.2

торые выбирают соответствующую строку и столбец накопителя.

Сигнал выбранной ЯП через блок коммутации столбцов 11 поступает на вход усилителя считывания 12, При изменении уровня на любом из выходов усилителя 12 происходит запоминание считанной информации и изменяется логический уровень на выходе блока фиксации 14, что прекращает обращение к накопителю 1, так как выключаются формирователи 4 и 8 и открываются регистры 6 и 10 для приема нового адреса, одновременно блок предварительного заряда разрядных щин 2 начинает восстанавливать исходные потенциалы на раз- ряднь1х шинах накопителя. Информация хранится в усилителе считывания 12 до .установления уровня ВК, соответствующего невыбранному состоянию схемы ЗУПВ,

Поскольку прием нового кода адреса в блоки приема и хранения инфор- . мации и. восстановление потенциалов На адресных шинах строки разрядных шинах матричного накопителя практически заканчивается в период считывания информации с выхода схемы, то минимальная длительность уровня ВК в период восстановления схемой исходного состояния должна быть достаточной только для выключения усилителя считывания,

.Из указанного выше следует, что

схема обеспечивает асинхронный режим работы, т,е, совмещение по

времени периодов считывания информации, предварительной зарядки адресные и разрядных шин, прием нового адреса, что сокращает цикл обращения к ЗУПВ,

Кроме того, в ОЗУ большой емкости время считывания информации сильно зависит от места положения ЯП в накопителе. Выигрыш в быстродействии при использовании предложенной схемы в системе памяти ЭВМ может составлять до 50%; уровни на разрядных ишнах матричного накопителя 1 при вы- выборке ЯП изменяются сравнительно медленно из-за малых размеров транзисторов ЯП и значительной емкости разрядных шин накопителя, в то же время усилитель считывания 6, реагируя на незначительное изменение уровня на разрядных шинах, обеспечивает быстрое срабатывание схемы фиксации

8 и выключение формирователей дешифраторов 5 и столбц(в 9, выбирающих ячейку памяти. Разрядные шины накопителя при этом не успевают полностью перезарядиться, благодаря чему уменьшается потребляемая мощность при обращении, сокращается время предза- рядки шин накопителя; хранение информации усилитр-лем после считывания ее из ячейки памяти и прекращение обращения к накопителю, а также запоминание кода адреса в блоках приема и хранения информации при обращении к схеме повышает помехоустойчивость, особенно при применении схемы в больших системах операт ив- ных ЗУПВ.

Формула изобретения

Полупроводниковое запоминающее устройство с произвольной выборкой, содержащее матричный накопитель, блок предзаряда разрядных шин, выходы которого соединены с разрядными шинами матричного накопителя, адресный блок выборки строки, состоящий из стробируемого формирователя, выход которого подключен к адресной шине матричного накопителя, дешифратора строк, выходы которого соединены с входами стробируемого формирователя, регистра адреса строки, выходы которого соединены с входами дешифратора строк, а входы являются адресными входами устройства,адресный блок выборки столбца, состоящий из стробируемого формирователя, выходы которого подключены к входам блока коммутации столбцов, дешифратора столб215135А

цов, выходы которого соединены с входами стробируемого формирователя, регистра адреса столбца, выходы которого соединены с входами дешифратора 5 столбцов, а входы являются адресньми входами устройства, причем выходы блока коммутации столбцов соединены с разрядными шинами матричного накопителя, усилитель считывания, входы

10 которого соединены с выходами блок а коммутации столбцов и блока управления, формирователь входного сигнала, выход которого соединен с входом блока коммутации столбцов, один

15 вход является информационным входом устройства, причем один вход блока управления является входом Сигнал выборки кристалла, другой входом Запись-считывание, а выход соединен

20 с входом формирователя входного сигнала и входом усилителя считывания, отличающееся тем, что, с целью повьшгения быстродействия устройства за счет уменьшения времен25 ных интервалов запись - считывание и считывание - считывание и снижения потребляемой мощности при обращении,у оно содержит блок фиксации считыва.е- мого сигнала, парафазные входы кото.JQ рого соединены с выходами усилителя считывания, стробируемый вход соединен с выходом блока управления, а выход соединен с входами стробируемых формирователей адресных блоков выборки строки и столбца и со стробируемы- ми входами регистров адреса строк и столбцов, выходы которых соединены с входами дешифраторов строк и столб- цов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство | 1978 |

|

SU748508A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

Изобретение относится к области электроники, в частности к вычисли.тельной технике, и предназначено для применения в интегральных цифро вых схемах. Целью изобретения является увеличение быстродействия за счет уменьшения временных интервалов запись-считывание и считьшание-считы- вание и снижение потребляемой мощности при обращении. Достигается это путем введения блока фиксации считываемого сигнала и стробируемых регистров.

| Патент США № 3609712, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-02-28—Публикация

1984-03-20—Подача