Устройство может быть использовано для умиожйния многоразрядных чисел в вычислительных устройствах в случаях, когда входвые сигналы представлены дискретными уровнями напряжений иостолиного тока.

Известны матричные устройства умножелия десятичных чисел, представление числа в которых должно быть либо фазоимпульсным, л H6iO п р остр аиств eiHH о - и м ну л ьс« ы. Известен о также быстродействующее устройство умножения двоичных ЧИсел, в котором одноразрядное десятичное чи;сло представлено четырьмя двоичными разрядами.

Однако TaiKoe представление числа требует сложного оборудования и наличия специальных преобразователей, а в случае двоичного представления - большого числа суммирзющих устройств.

Целью изобретения является упрощение схемы умножения двух одноразрядных десятичных чисел, исключение преобразования формы представления чисел и обеспечение возможности работы с мнотоуровнсвьиш сигнала-ми.

В предлагаемОМ множительном устройстве для быстрого перемножения одноразрядных десятичных чисел X и Y эта цель достигается путем представления результата перемножения двумя десятичными разрядами Wi и Wz

в виде дискретных уровней напряжения от О до 100 в с интер1вало,м 100 за счет реализации на операционных усилителях, пассивных сумматорах, пороговых и логических элементах математического описания старшего разряда Wi и реализации на ключевых элементах и операционном усилителе вдладшего разряда W2.

При ЭТОА1 операционные усилители, пассивные сумматоры, ключевые, пороговые и логические элементы могут |быть выполнены на интегральных схемах.

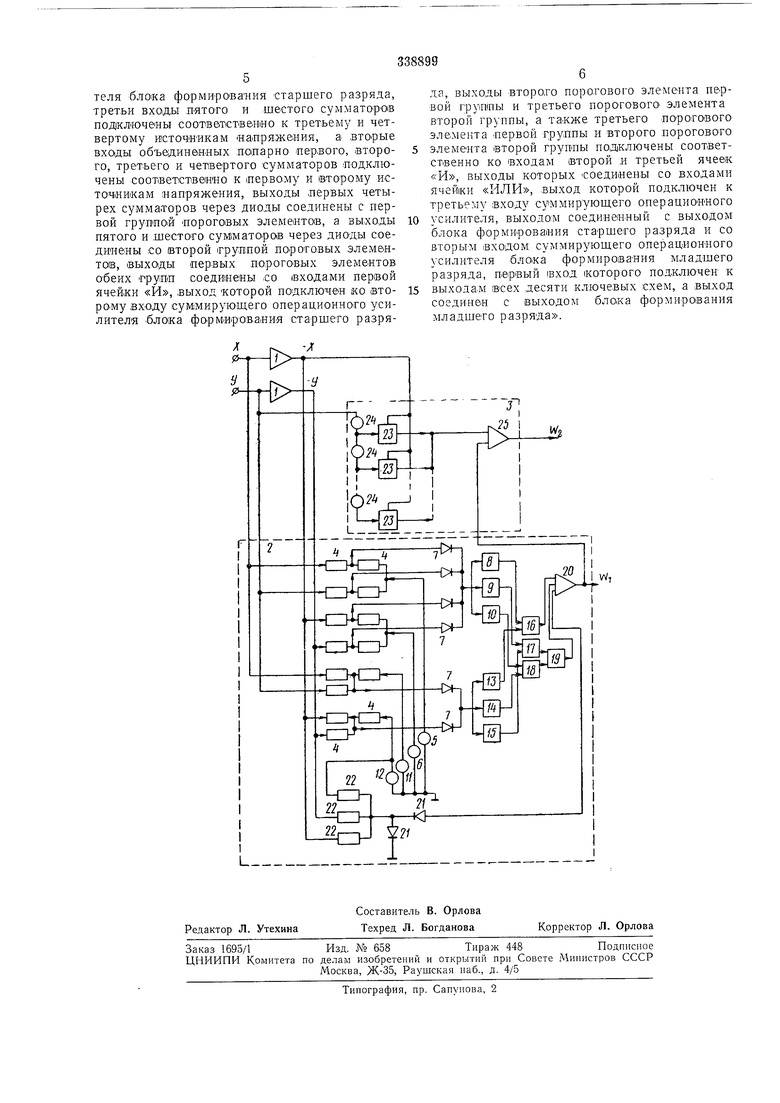

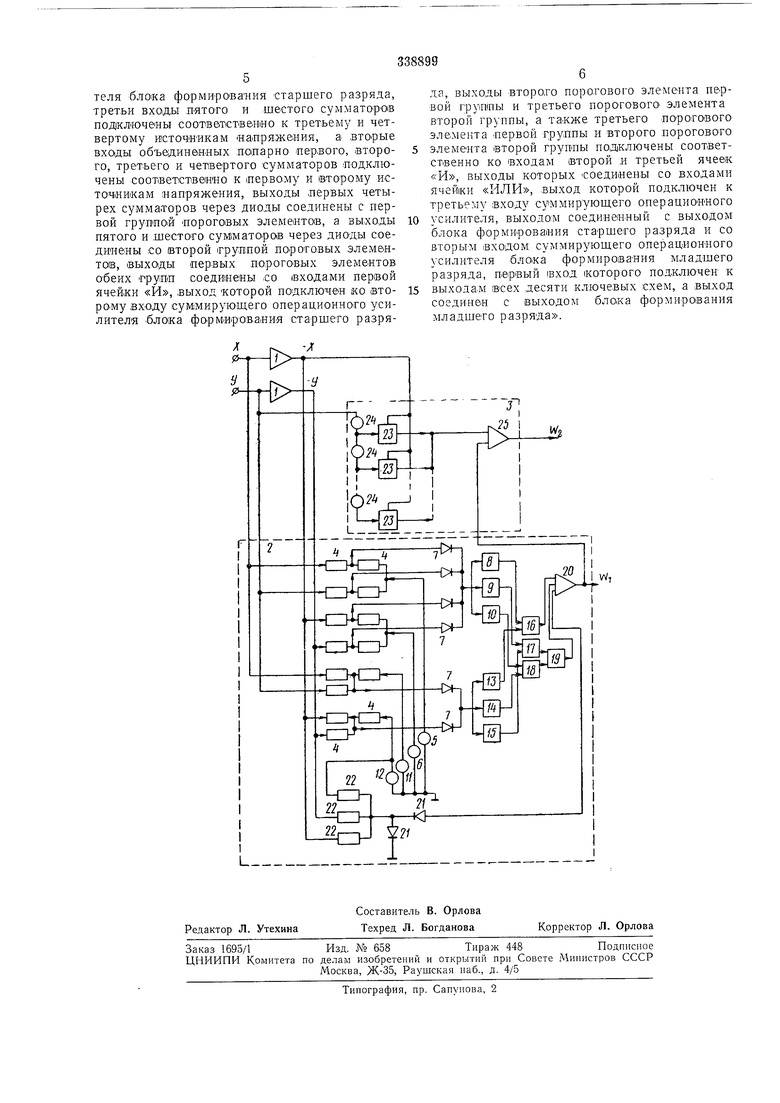

Схема предлагаемого устройства приведена на чертеже.

Каждая входная клемма устройства, подключенная к источникам напряжения, соответствующим сомножителя X и Y, соединена со входом своего инвертирующего операцио1Нного усилителя /.

Множительное устройство содерлсит два основных блока 2 и 5. В блоке 2 реализуется старший разряд Wi произведения XY. Блок 2 состоит из четырех пассивных сумматоров яа двух сопротивлениях 4. Первые два сумматора подсоединены к источнику напряжения 5, соответствующему-«5, вторые два - к источнику напряжения 6, соответствующему «5 дискретным единицам. Другие входы этих сумматоров соединены соответственно с шичерез диоды 7 соединены с группой пороговых элементов 8-W.

Пассивный сумматор на трех сопротивлениях 4 соединен с шинами J, У и с «сточйиком //, соответствующим «10 дискретным единиЦЗМ, другой пассивный сумматор на трех сопротивлениях 4 соединен с шинами -Xi-Y и с HCTOMiHHiKOiM 12, соответ1СТвующИ|М «10 дискретным единицам. Выходы этих двух сумматоров через диоды 7 соединены с группой порого.вых элементое 13-15.

Выходы порого1вых элементов 8, 13 соединены с логической ячейкой «И 16, выходы пороговых элементов 9 и 15 - с лО)ГИ|ческой ячейкой «И 17, а выходы нороговых эле-ментов 10 W. 14 - с логической ячейкой «И 18. Входы логической ячейки 19 «ИЛИ соединены с выходами ячеек 17 и 18.

Вход операционного усилителя 20 соединен с шинами -X, -, источнико м напряжения 12 через диоды 21 и входные согаротивления 22 и с выходами ячеек 16, 19.

В блоке 5 реализуется младший разряд произведения Wz. Шина У соединена со входами десяти ключей 23 через цепочку последовательно включенных источ НИ1Ков напряжения 24. В качестве источников напряжения применены полупроводниковые стабилитроны с напряжением стабилизации t/cTКлючи 23 Соединены с шиной -X, а выходы всех десяти ключей 23 соединены со входами операционного усилителя 25. Кро.ме того, ко входу усилителя 25 подсоединен с коэффицие1нто1М десять сигнал, соответствующий старшему разряду Wz. Сипналы, соответствующие сомножителя1М X и Y, представляют собой дискретные многоуровневые напряжения с интервалом 100 в дианавоне от О до 1000.

Операционные усилители / И нвертируют напряжения, соответствующие сомножителям X и У.

В блоке 2 с четырех пассивных сумматоров на двух сопротивлениях снимаются нанряжения, соответствующие Х-5, Y-5, -Х-{-5, - 7+5. На диодах 7 выделяется напряжение, соответствующее max (X-5), (У-5) } . Оно. поступает на пороговые элементы 8-10, имеющие пороги срабатывания 3,5 единицы, 2,5 единицы, 1,5 единицы соответственно.

С Д|вух пассивных сумматоров на трех icoпротивлениях снимаются напряжения, соответствующие (X + Y-10) и -(Х+У-10). На диодах 7 выделяется напряжение, соответствую;щее (X+Y-10) и поступает на пороговые элементы 13-15, имеющие пороги срабатывания 3,5 единицы, 1,5 единицы и 0,5 единиц соответственно. Если срабатывают пороговые элементы 8 и 13, то ячейка «И 16 выдает сигнал, соответствующий единице. Бели cpai6aтывают пороговые элементы 9 и 15, то ячейка «И 17 посылает сигнал в ячейку «ИЛИ 19. Бели срабатывают пороговые элементы/ и 14, то ячейка «И 18 посылает сигнал в

ячейки «ИЛИ 19, которая выдает сигнал, соответствующий единице.

Сумматор, выполненный на операционном усилителе 20, формирует сигнал, соответствующий старшему разряду Wi.

В блоке 3 ключи 23 открываются напряжением, соответствующим сомножителю Y, причем напряжение открывания для каждого из десяти ключей отличается от предыдущего на величину f/cT. Нри открывании каждого ключа через него поступает на вход операционного усилителя 25 напряжение, соответствующее -X,с входного инвертора / с коэффициенто,.м усиления «единица. Таким образом, если на операционный усилитель 25 больше никаких напряжений не подавать, то выходной его силпал соответствовал бы произведению XY, (напряжение на выходе менялось бы от О до 10000). Но на операционный усилитель 25 подается напрЯЖение, соответствующее Wi с коэффициентом усиления «десять. Следовательно, с выхода усилителя 25 снимается напряжение, точно соответствующее младщему разряду Wz результата умножения XY.

Предмет изобретения

Устройство для ускоренного перемножения двух одноразрядных десятичных чисел, содержащее блоки формирования соответственно старшего и младшего разрядов произведения, включающие операционные усилители, пассивные сум1маторы, ключевые схемы, пороговые элементы, логические ячейки «И, «ИЛИ и источники напряжения, отличающееся тем, что, с целью упрощения устройства и обеспечения возможности работы с мпогоуровневыми сигналами, одна входная клемма устройства, подключенная к источнику напряжения, соответствующему первому сомножителю, соединена со входом первого операционного усилителя и с первым входом первого и пятого сумматоров блока формирования старшего разр5 1да, другая входная клемма устройства, подключенная к источнику на|Пряжения, соответствующему второму сомножителю, подключена ко входу .второго операционного усилителя, .к первому .входу второго и вторОМу вхо.ду пятого сумматоров формирования старщего разряда и через цепочку последовательно сое.диненных стабилитро.нов к первым входам десяти ключевых схем блока фор.мирования младщего разряда, вторые входы которых соединены с выходом первого операционного усилителя, который подключен к первому входу третьего и шестого сумматоров блока формиро.вания старшего разряда, выход второго операционного усилител я подключен к первому выходу четвертого и второму входу щестого сумматоров и также, как выход nepBoiro операционного усилителя и четвертый источник напряжения через диод, включенный в обратном направлении, лодсоединены к одному из входов суммирующего операционного усили

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовый одноразрядный двоичный сумматор | 1973 |

|

SU462179A1 |

| Умножитель | 1986 |

|

SU1327093A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| СПОСОБ ПЕРЕМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 2010 |

|

RU2525477C2 |

| Матричное вычислительное устройство | 1979 |

|

SU824195A1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для умножения | 1979 |

|

SU911514A1 |

Даты

1972-01-01—Публикация