Црёдлбжениая .матрица от1Ю1СИт:Сй (К ()&Aaсти а(в(томати1ки и ,слителыной. тех1ники и дюжет найти Широкое трвмеиейие при , ipafsработке накюиителей равлиганых запоминающих устрой1ст1в.

И:з1В€с1тН|Ы сх.емы матриц ЗУ «а МОП-транЗисторах, представляющИб собой в бо/льшияст1В€ случа ев набор ст атических трипгеров, объединенных по CTpoiKaiM н столбцам в матрицу.

iB матрицах со словариой оргатизаци-ей у которых считывайИе и. запись 1Прои|Сх,одят через одни и те же разрядные шины, затворы проходиых транзисторов, например, каждой строки, объединяются в числовую (адресную) шину, а истоки (стоки) униполярности транзистора каж|дого столбца объединяются в разрядиы.е шйн-ы.

В известных матрицах, у которых выборка Производится ПО) системе совладения, собственная схема запоминающих ячеек включает в .себя координатный транзистогр.

Известные технические решения iCseMHon структуры матриц с координатной организацией имеют следующие недостатки: относительно большое йолич1ест,В|О элементов на единицу информации при уменьШ|ении кюличе1СТВ|а. внешник еыврдов, что усложняет тсипологдаю и coiaroeTCTiB&HHo снидаавт npjOneiHT выхода лодных изделий;

относительно невысокое быстродействие при уменьшении колИЧ|ест1ва а1КТИ1в:ных элементов на единицу информации;; большое количестто пересечений, затрудняющее технологию изготовления схем и-повышающее стоимость изделий.

Целью изобретения являет ся уменыше-ние (Количества вНеоших выводов, повы;шенпе быс1тродей1с1т1ВИ1Я, умшьшеИие количества активных элементов ма единицу информация и обеспечение резервирования каждой единицы информации в соот(ветствуюш,их Ipynnax. |Э;та цель достигается путем вынесения координатного транзистора ив соста1ва зашоминающей яче1йки (трИГге;ра) и i представления (Матрицы, в виде условных групп элементов матриц, объединенных по строкам в общие адресные шины, например в шины X. При этом в-р1азр1ядныеШИНЫ каждоГО столбца попарно (Включены симметричные униполя(р1ные Л1О:П-транзи1сторы с объединенными затворами, общие точки которых объединены с соответствующими общими, точка ми, затворо(в транзисторных пар в других условных групна-х элементов матриц. Эти объединенные тоЧ1ки для данной .схемы представляют вторую координату, например К|ООрД1Инату Y, а од1ноименные стоки (И истоки к,ажщой пары транзисторов отдельных усчтовных групп

пись-считывание одного из разрядов всех адресов. Сггруктура схе|м|ы маггриады целесообразна с точки зрения организации нако|пите л ЗУ, так как транзисторы, включзиные IB разрядные (ди-ффузаоганые) шины, являются юро.ме ТОГО буфериы.ми, элементаМИ, работающими на конкретную емкостную и неш,и1ней|но-о.м.иче1окую «а грузку, что в свою очередь, онижает тре:бо1ва1ни:я к мощности разрядных формирователей записи информации и обеспечивает возможность нарафазной записи ИИ формации.

Предлож-еииая матрица более технолог.ич1на -по сравнению с иавесрньими, так как ее изготовлеиие сводится IK изготовлению матрицы со словариой Оргаиизацией ис относительно «1е1б.олышой по кол.ич€ству активных KOiMWOlieiHTOB (тр аизисторое) логи-ноокой приотавкюй:, объединяющей в себе группу транзисторов. Это 31начИ|Телыно у-м€Иьшает к олнчесгво оересечепий но тонкому офисному слою, так (как все иереСел ения, связанные с организацией коор|д 11гт1ной системы, конструктивно вы1полн.яф4й( толстом маскирующем диэлектриче1Сйб.м олое.

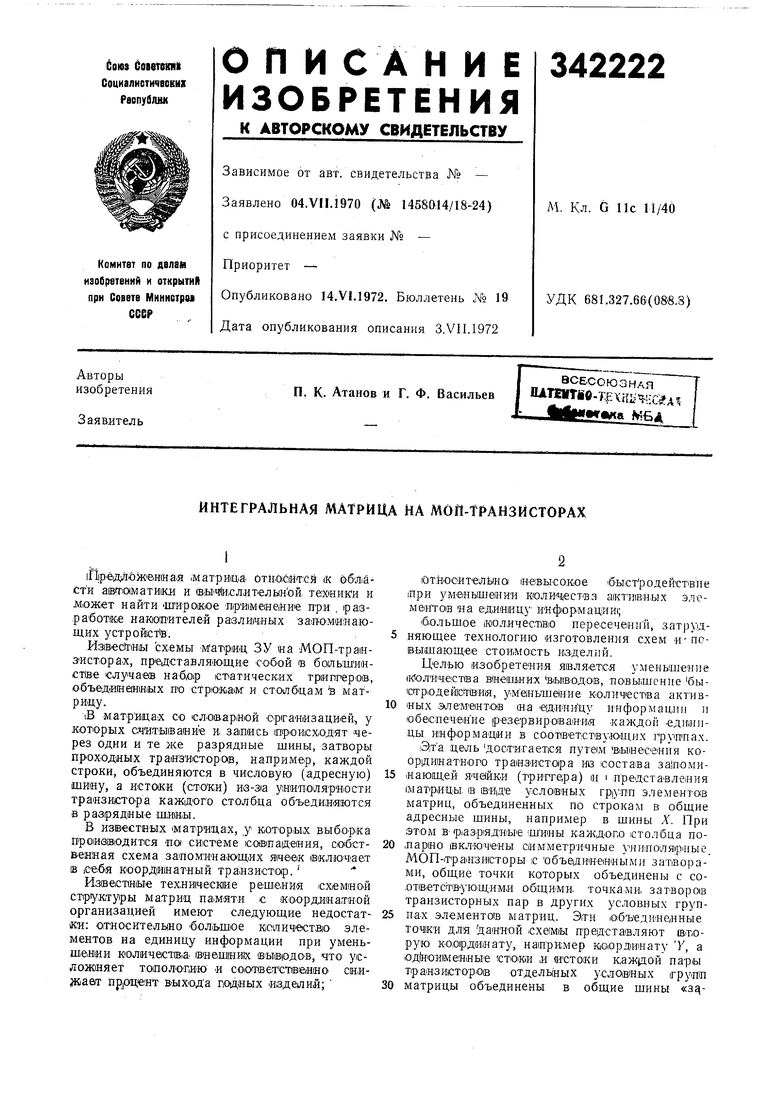

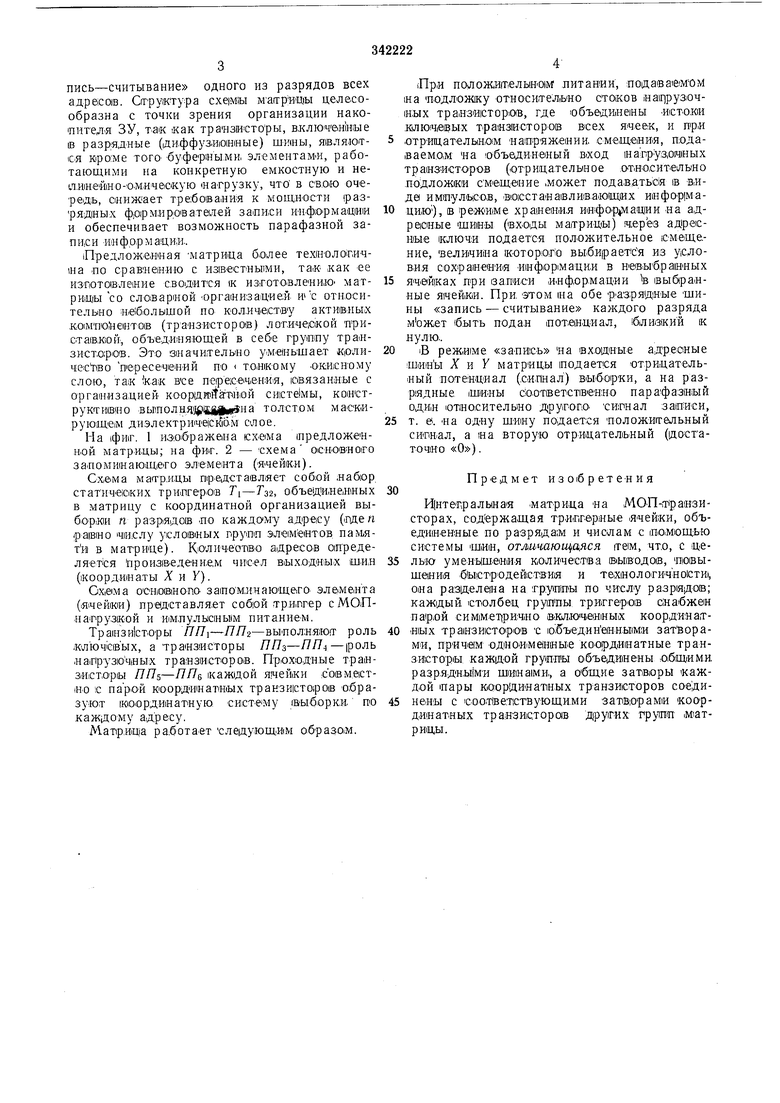

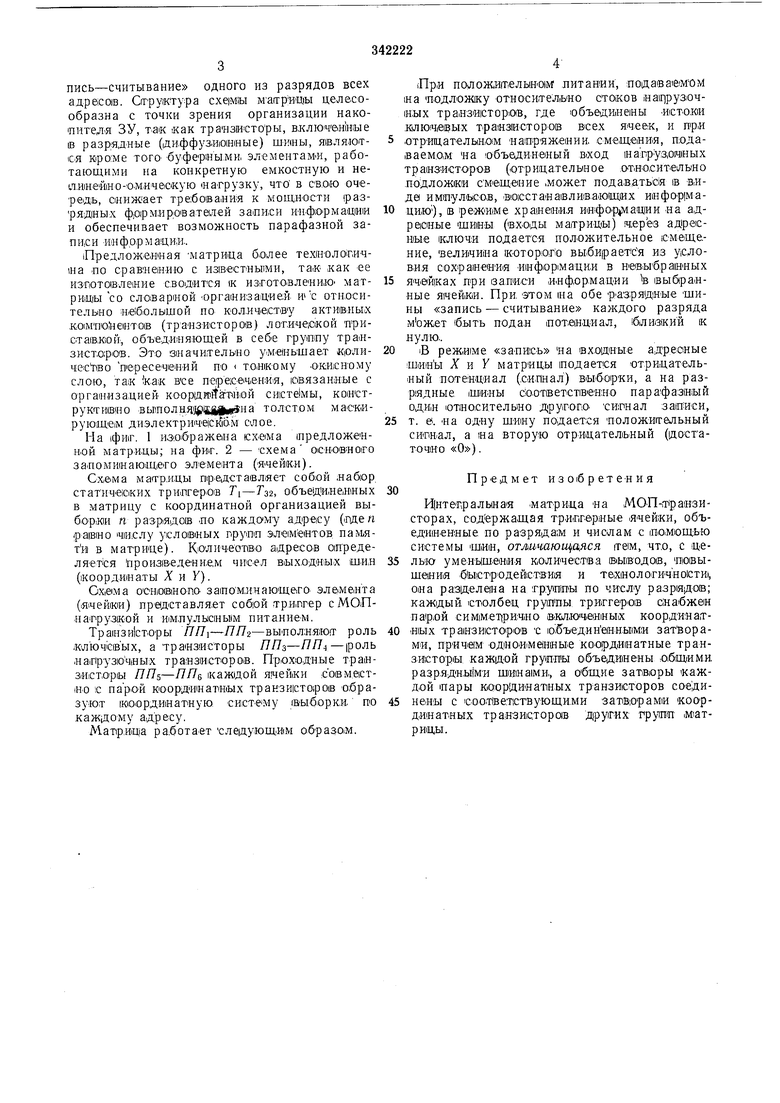

На 1ФИ1Г. 1 изображена схема предложенной матрицы; на фиг. 2 - схема основного за1номинающ1е1го элемента (ячейки).

Сх;бма ма1тр,ицы пр-едставляет собой набюр статических TpHnrepoiB TI-Тзг, объеМине.нных в матрицу с координатной организацией выборми п разрядов но каждому адресу (вдеп paiBHo числу условных лрупп Э ле1М е1Нтов. иамяти в матрице). Количество адресов определяется произведение,м чисел выходных шиц (координаты X и У).

GxeiMa основно-по за1пом.и:нающе1го эле1мента (.ячейки) представляет собой триггер сМОПна грузкой и .пулысны1м питание.

Транзисторы ТУЯ -ПП -вынолняюТ роль .ключевых, а транзисторы ЯЯз-ЯЯ4-роль нагрузочных транзисторов. Проходные транзисторы ЯЯб-ЯЯб каждой я чейки совместно с парой координатных транзисторов образуют координатную систе му (В-ыборки. по каждому адресу.

MaTipHHia работает следующем образом.

(При положите л ыном литании, подаваемом на подлож1ку относительно стоков нафузочных транзисторов, где объединены истоки ключевых транзисторов всех ячеек, и при .отри1цатель)НО1М напряжении, смещения, подаваемом на объединаный вйод напрузомных транзисторов (отрицательное .атносителыно .подложки смещение .может подаваться в виде им1пул1Ь|Сов, восстанавливающих И1нфор|мацию), в режиме хранения ин|фор ации на адресные шины (входы матрицы) ч,ерез адре1сные ключи подается положительное смещение, величина 1которо;Го выбирается И|3 условия сохранения инф|0р1мации в невыбранных

ячЭйках при 8 а лиси информации b выбранные ячейки. При, этом 1На обе р-азрядные шины «запись - считывание каждого разряда может (быть подан потенциал, б|ЛИ13кий к нулю..

iB режиме «запись на входные адресные щины X и У матрицы подается отрицательный лотенциал (сишал) выборки, а на разрядные шины соответственно парафазный один относительно другого- сишнал записи,

т. в. на одну щину подается положиггельный сигн.ал, а на вторую отрицательный (достаточно «О).

Предмет изобретения

И|нтеГраль1на1Я -матрица на -МО-П-траизисторах, содержащая тр-игг-ерные ячейки, объединенные по разрядам и числам с помощью системы шин, отличающа яся iTeiM, что, с цельвд уменыш-ения количества 1В1Ыводо1В, повышения -б ыстродействи1Я и те-хнологично1сти1, она разделана на группы по числу разрядов; каждый столбец группы трвггерО1в с;набжен парой сим|Мет1рично |В:Ключенны1Х к-оординаггН1ЫХ тра|нзисторов с о-бъединенными затворами, причем -однои1ме1нны-е ко-ординатные транзисторы каждой грушиы объединены О|бщими. разр-ядны1ми щинами-, а общие затворы каждой пары координатных тр анзисторов соединены с с-оо-т1вегг1ствующи.ми затворами координатных трашисторав друг-их грушш М1атрицы.

te

Уг

У

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

Даты

1972-01-01—Публикация