Изобретение относится к автоматике и вычислительной технике.

Известен триггер на МОП-транзисторах, стоки которых через нагрузочные транзисторы соединены с шиной питания и со стоками входных транзисторов.

Цель изобретения - повышение быстродействия и экономичности устройства. Достигается она тем, что в каждое плечо предлагаемого триггера включены дополнительные нагрузочные транзисторы, затворы которых подклю чены к противоположным входам триггера, a стоки объединены и подключены к шине питания через управляюш,ий транзистор, затвор которого соединен с перовым управляющим входом триггера, a затворы нагрузочных транзисторов соединены со вторым управляюш,им входом.

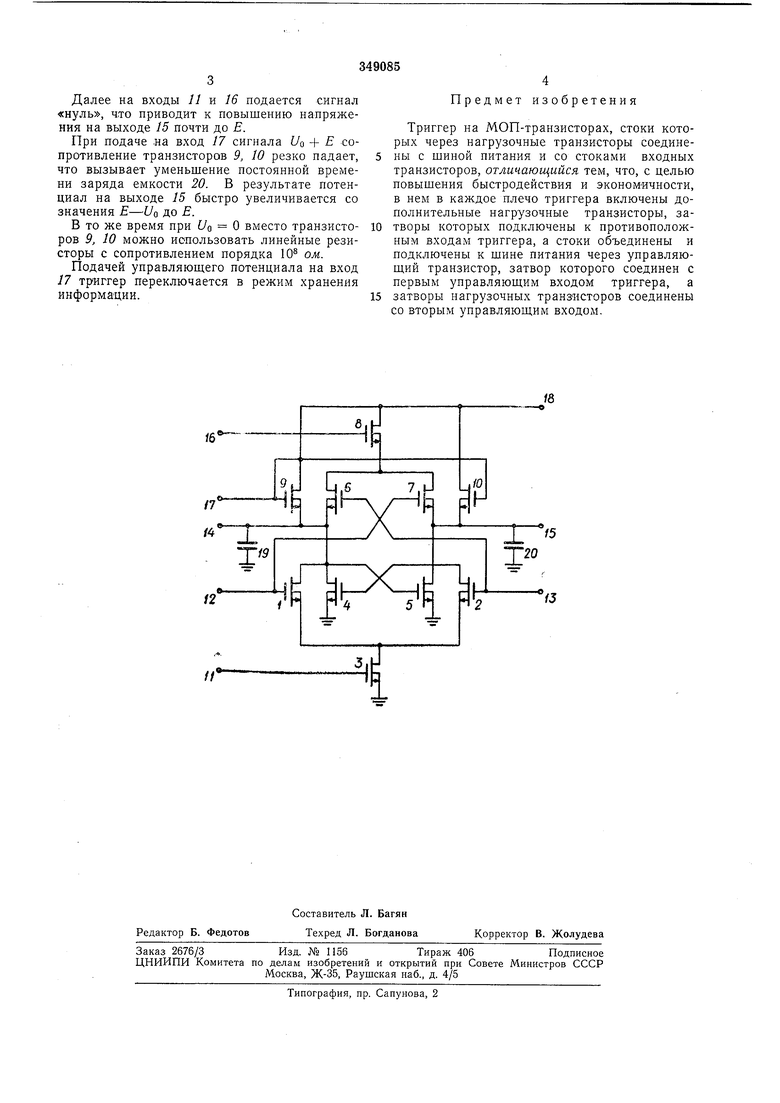

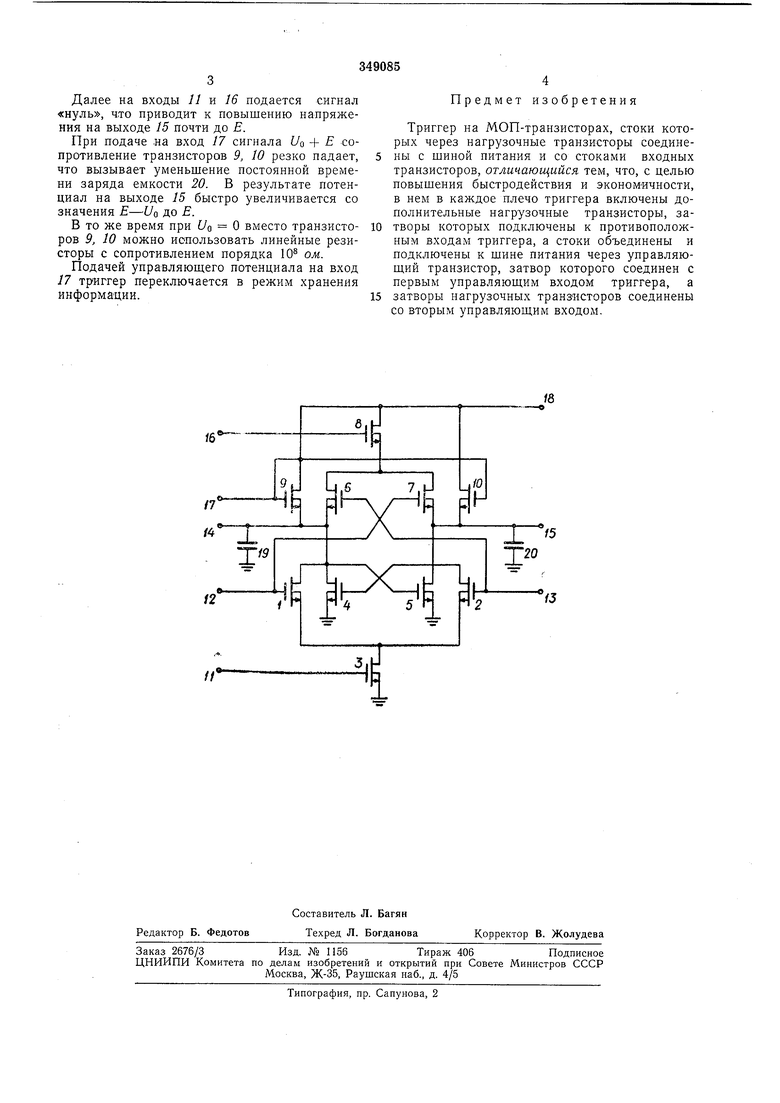

На чертеже представлена принципиальная электрическая схема устройства.

Триггер на МОП-транзисторах /-10 содержит вход 11 управления установкой в «нуль и «единицу, противоположные входы 12 и 13, выходы 14 и 15, первый « второй управляющие входы 16 и 17 соответственно и шину питания 18. Транзисторы /-3 образуют схему «И-ПЕ установки в «нуль и «единицу. Стоки транзисторов 1, 2, 4, 5 через нагрузочные транзисторы 9, 10 подключены к шине питания 18. Затворы дополнительных

нагрузочных транзисторов 6, 7 подключены к противоположным входам 13 и 12 триггера, a их стоки объединены и подключены к шине питания 18 через управляющий транзистор 8.

При работе триггера в режиме хранения информации нужно на входы // и 16 подать сигнал низкого потенциала - «нуль, a на вход 17 - управляющее напряжение, амплитуда которого определяется токами утечки транзисторов /-5; через транзисторы 9 и 10 протекает ток заряда паразитных емкостей 19 и 20.

Работа устройства в режиме приема и выдачи информации складывается из нескольких этапов.

Вначале на входы 12 и 13 подаются сигналы «единица и «нуль соответственно, a затем на вход 11 - «единица. При этом на выходе 14 устанавливается низкий потенциал.

После этого на вход 16 подается «единица, в результате чего через транзисторы 7 к 8 течет ток заряда емкости 20, которая заряжается до напряжения Е-t/o, где Е - напряжение питания, a Uo-пороговое напряжение транзистора.

Таким образом происходит фиксация состояния триггера, определяемого высоким потенциалом на выходе 15 и низким - на выходе 14.

Далее на входы 11 и 16 подается сигнал «нуль, что приводит к повышению напряжения на выходе 15 почти до Е.

При подаче .на вход 17 сигнала UQ + Е сопротивление транзисторов Я Ю резко падает, что вызывает уменьшение постоянной времени заряда емкости 20. В результате потенциал на выходе 15 быстро увеличивается со значения Е-UQ до Е.

В то же время при t/o О вместо транзисторов 9, 10 можно использовать линейные резисторы с сопротивлением порядка 10 ом.

Подачей управляюш,его потенциала на вход 17 триггер переключается в режим хранения информации.

Предмет изобретения

Триггер на МОП-транзисторах, стоки которых через нагрузочные транзисторы соединены с шиной питания и со стоками входных транзисторов, отличающийся тем, что, с целью повышения быстродействия и экономичности, в нем в каждое плечо триггера включены дополнительные нагрузочные транзисторы, затворы которых подключены к противоположным входам триггера, а стоки объединены и подключены к шине питания через управляюш,ий транзистор, затвор которого соединен с первым управляющим входом триггера, а

затворы нагрузочных транзисторов соединены со вторым управляюш,им входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| БАЗОВЫЙ УСИЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДИФФЕРЕНЦИАЛЬНОЙ ДИНАМИЧЕСКОЙ ЛОГИКИ (ВАРИАНТЫ) | 1999 |

|

RU2154338C1 |

| Устройство считывания для программируемой логической матрицы | 1988 |

|

SU1566410A1 |

/б

sJ СГ ГЛ up

нБ ан

.

;l(|lPS

//

15

V5

Даты

1972-01-01—Публикация