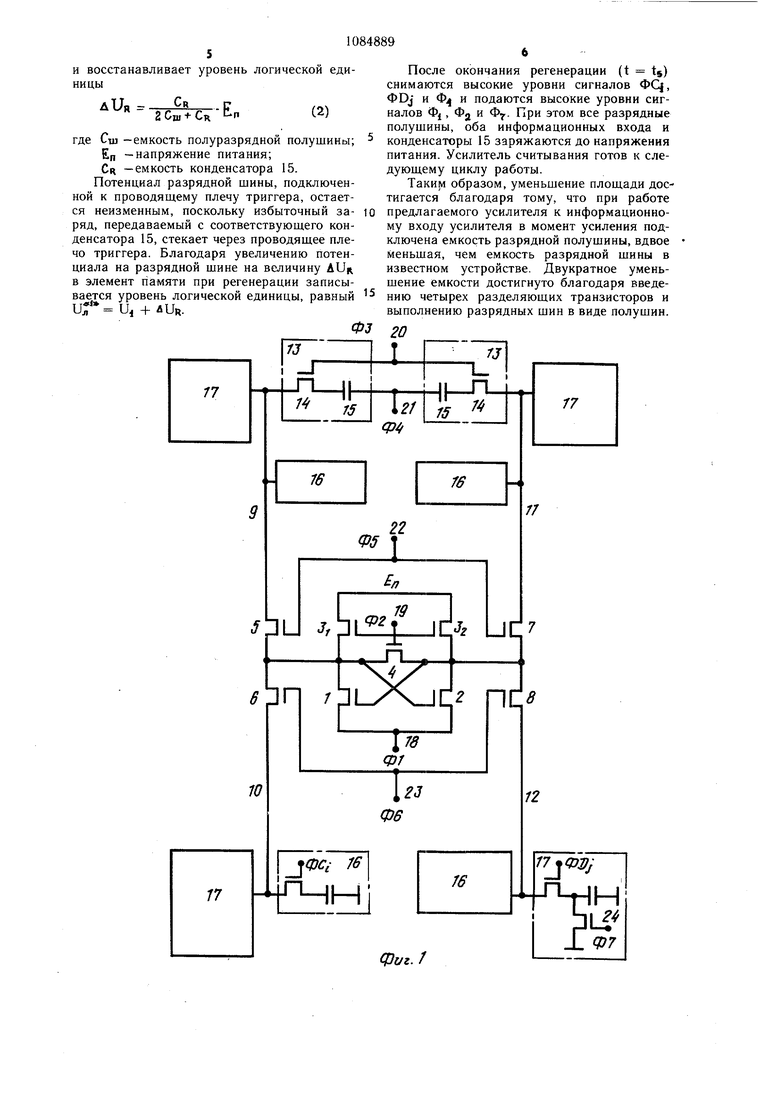

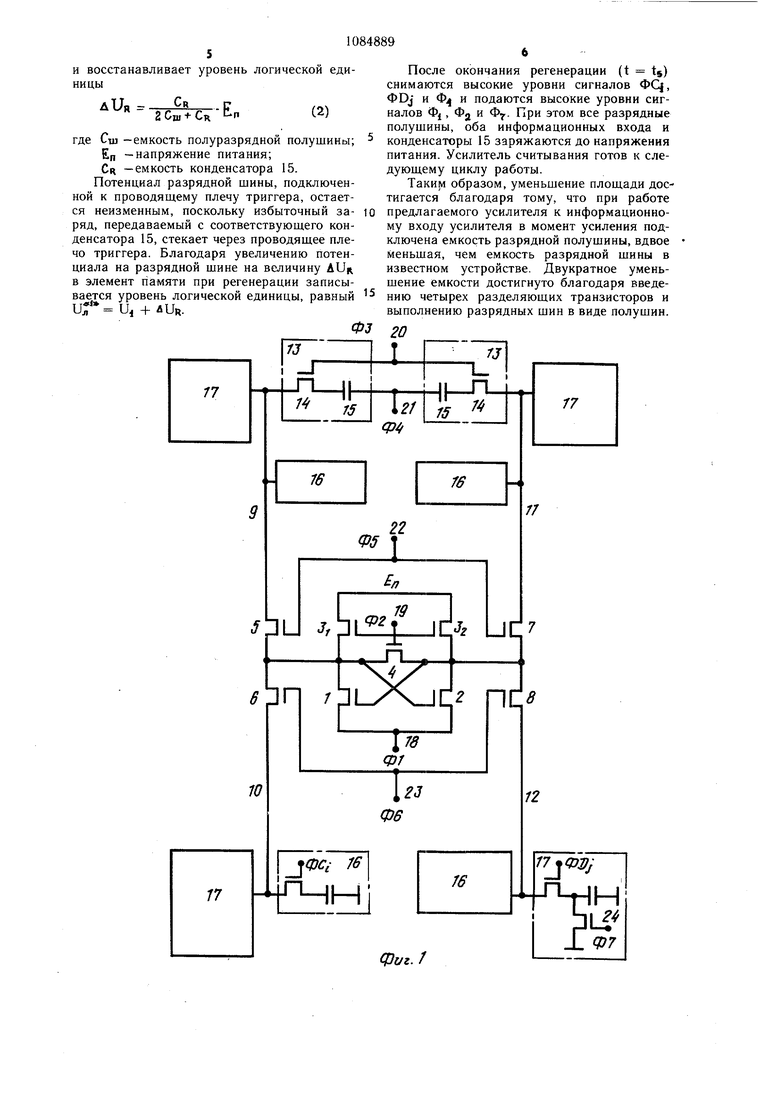

Изобретение относится к вычислительной технике, а именно к усилителю считывания, который может быть использован в интегральном полупроводниковом МДП динамическом запоминающем устройстве на однотранзисторных элементах памяти. Известен усилитель считывания, выполненный на основе триггера динамического типа, плечи которого образуют информационные входы усилителя считывания, к каждому из которых подключены транзисторы предзаряда и через соответствующие разрядные шины однотранзисторные элементы памяти и один опорный элемент I. При работе такого усилителя на его информационные входы поступает дифференциальный сигнал. Поступивший из элемента памяти сигнал усиливается усилителем считывания и снова записывается в этот же элемент памяти. При усилении, из-за емкостной связи между входами усилителя и частичного разряда плеча триггера с большим потенциалом, происходит частичная потеря уровня логической единицы, которая достигает 20% от его максимального значения. В результате после усиления в элемент памяти записывается уменьшенный уровень логической единицы, который составляет всего 80% его номинального значения, равного напряжению питания. Потеря уровня логической единицы приводит к снижению надежности работы усилителя считывания и создает возможность считывания ложной информации при последующих обращениях к этому элементу памяти, что является недостатком этого усилителя считывания. Наиболее близким по технической сущности к изобретению является усилитель считывания, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены, два нагрузочных транзистора, стоки которых объединены, а истоки подключены к стокам переключающих транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток - с истоком второго нагрузочного транзистора, а затвор - с затворами нагрузочных транзисторов и первой шиной управления, конденсаторы и тран. зисторы регенерации, затворы которых подключены ко второй шине управления, истоки транзисторов регенерации подключены к стокам переключающих транзисторов, а стоки - к одним обкладкам конденсаторов, другие обкладки которых подключены к третьей шине управления 2. Известны усилитель считывания позволяет благодаря наличию блоков восстановления уровня логической единицы восстановить уровень логической единицы после усиления информации до его номинальной ве личины, равной напряжению питания, что существенно увеличивает надежность работы. При работе усилителя в начальный момент усиления на его информационных входах установлен дифференциальный сигнал ди, поступивший из элемента памяти: , где Схр-емкость хранения элемента памяти; Сщ -емкость разрядной шины; СВУ -емкость информационных входов усилителя; ЕП -напряжение питания. Элемент памяти должен облада ь величиной емкости Csp которая при данной величине емкости разрядной шины Сш обеспечит (минимальную) необходимую величину информационного сигнала, достаточную для правильного считывания и усиления. При этом, как следует из выражения (1), уменьц1ение величины емкости разрядной шины Сш, подключенной к информационным входам усилителя считывания в момент опроса элемента памяти, позволит для получения необходимой величины дифференциального сигнала ли использовать меньшую величину емкости хранения элемента памяти Схр и тем самым уменьшить площадь элемента хранения. Поскольку элементы хранения занимают более площади усилителя считывания, это дает возможность уменьшения его площади. Недостатком известного усилителя считывания является большая площадь, требуемая для получения необходимой величины дифференциального сигнала. Цель изобретения - повышение степени интеграции устройства. Поставленная цель достигается тем, что в усилитель считывания, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены и подключены к первой шине управления, два нагрузочных транзистора, стоки которых объединены, а истоки подключены к стокам переключающих транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток - с истоком второго нагрузочного транзистора, а затвор - с затворами нагрузочных транзисторов и второй щиной управления, конденсаторы, транзисторы регенерации, затворы которых объединены и подключены к третьей шине управления, а истоки соединены с одними обкладками конденсаторов, другие обкладки которых подключены к четвертой шине управления, введены четыре разделяющих Транзистора, причем истоки первого и второго разделяющих транзисторов подключены к стоку первого переключающего транзистора, а истоки третьего и четвертого разделяющих транзисторов подключены к стоку второго переключающего транзистора, стоки первого и третьего разделяющих транзисторов подключены соответственно к стокам первого и второго транзисторов регенерации затворы первого и третьего, второго и четвертого разделяющих транзисторов подключены соответственно к пятой и шестой шинам управления, истоки разделяющих транзисTQpoB являются информационными входами усилителя считывания. На фиг. 1 дана схема усилителя считывания; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит первый 1 и второй 2 переключающие транзисторы, два нагрузочных транзистора 3i и Зг, балансный транзистор 4 первый 5, второй 6, третий 7 и четвертый 8 разделяющие транзисторы, первую 9, вторую 10, третью 11 и четвертую 12 разрядные полущины, два блока 13 восстановления уровня логической единицы, каждый из которых содержит транзистор 14 регенерации и конденсатор 15, однотранзисторные элементы 16 памяти, соединенные с разрядными полущинами и четыре опорных элемента 17, подключенные к каждой разрядной полущине, шины 18-24 управления. Стоки разделяющих транзисторов соединены с разрядными полущинами, а истоки - с информационными входами усилителя считывания. Стоки транзисторов регенерации соединены соответственно с первой 9 и третьей 11 разрядными полущинами. Однотранзисторные элементы 16 памяти имеют входы включения , опорные элементы 17 имеют входы включения ФD - ФDj и вход установки опорного напряжения Фг. В исходном состоянии (t) на шинах 18 и 24 установлен высокий уровень сигналов Ф| и Фт, на шинах 19 - 23 установлен высокий уровень напряжения UB сигналов Ф, , Ф,, Фг и Ф, - , -i-j, t-j и чб, превыщающии уровень напряжения питания как минимум на величину порогового напряжения транзисторов ( + HT), на шине 21 установлен низкий уровень сигнала Ф , на входах включения однотранзисторных элементов памяти и опорных элементов установлены низкие уровни сигналов ФС и ФО|. При этом все четыре разрядные полушины и оба конденсатора 15 блоков восстановления уровня логической единицы заряжены до напряжения питания. В опорных элементах сигналом Ф установлен опорный уровень напряжения. В элементе памяти хранится записанная туда ранее информация. В начале рабочего интервала (t to) снимаются высокие уровни сигналов Ф, Фд и Ф, и одного из сигналов Ф5 или Ф . Допустим снимается высокий уровень сигнала Ф. Тракзисторы 14 регенерации и разделяющие транзисторы 6 и 8 переходят в закрытое состояние и отключают от информационных входов усилителя емкости разрядных полущин 10 и 12 и конденсаторы 15. К информационным входам остаются подключенными только разрядные полушины 9 и 11. После этого в момент времени t t производится обращение к одному из элементов памяти, подключенному к разрядной полушине 9 или 11, допустим к полушине 9, для чего подается высокий уровень сигнала ФС. Одновременно с этим производится обращение к опорному элементу, подключенному к противоположной разрядной полушине, в данном случае к полущине 11 (подается высокий уровень сигнала ODj). В результате на информационных входах устанавливается дифференциальный сигнал ли, соответствующий информации, хранящейся в выбранном элементе памяти: ди Ui-Uj, если хранилась единица; ли -(LJj ), если хранился нуль, где Ui и Uj - потенциалы на первом и втором информационных входах, соответственно. Для определенности будем считать, что в элементе памяти хранилась единица, т.е. Uj- Uj. Так как разделяющие транзисторы 6 и о находятся в закрытом состоянии и отключают от информационных входов разрядные полущины 10 и 12, в предлагаемом усилителе дифференциальный сигнал ЛУ такой же величины, как и в известном усилителе, получается при меньшей площади элемента памяти. Это приводит к уменьшению площади усилителя считывания. После установления на информационных входах дифференциального сигнала AU(t tj) подается низкий уровень сигнал Ф включения усиления. При этом второе плечо триггера (с меньшим установившимся уровнем потенциала Uj) переходит в проводящее состояние и потенциал на втором информационном входе уменьшается до нуля, а на первом плече (с большим установившимся уровнем потенциала U|) происходит лишь частичная потеря уровня напряжения из-за емкостной связи и небольшого приоткрывания этого плеча. В момент времени t tj подаются высокие уровни сигналов Ф, и Ф, при этом транзисторы 14 регенерации и разделяющие транзисторы 6 и 8 переходят в проводящее состояние. Разрядная полущина 12, конденсатор 15, соединенный с полушиной 11, разряжаются через проводящее плечо триггера. После этого в момент времени подается высокий уровень сигнала Ф . В результате заряд с конденсаторов 15 передается на соответствующие разрядные полущины 9 н 11. При этом потенциал разрядной шины, подключенной к закрытому плечу триггера, увеличивается на величину AlJR и восстанавливает уровень логической единицы(2) где CTU -емкость полуразрядной полушины; Е„ -напряжение питания; CR -емкость конденсатора 15. Потенциал разрядной шины, подключенной к проводящему плечу триггера, остается неизменным, поскольку избыточный заряд, передаваемый с соответствующего конденсатора 15, стекает через проводящее плечо триггера. Благодаря увеличению потенциала на разрядной шине на величину AU в элемент ггамяти при регенерации записывается уровень логической единицы, равный Ыл i + лик. После окончания регенерации (t tj) снимаются высокие уровни сигналов ФQ, ODj и Ф и подаются высокие уровни сигналов Ф, Фд и Фf. При этом все разрядные полушины, оба информационных входа и конденсаторы 15 заряжаются до напряжения питания. Усилитель считывания готов к следующему циклу работы. Таким образом, уменьшение площади достигается благодаря тому, что при работе предлагаемого усилителя к информационному входу усилителя в момент усиления подключена емкость разрядной полушины, вдвое Меньшая, чем емкость разрядной шины в известном устройстве. Двукратное уменьшение емкости достигнуто благодаря введению четырех разделяющих транзисторов и выполнению разрядных шин в виде полушин.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Усилитель считывания | 1978 |

|

SU769617A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2047919C1 |

| Усилитель считывания | 1980 |

|

SU938316A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий два переключающих транзистора, сток первого из которых соединен с затвором второго переключающего транзистора, сток которого соединен с затвором первого переключающего транзистора, истоки переключающих транзисторов объединены и подключены к первой шине управления, два нагрузочных транзистора, стоки которых объединены, а истоки подключены к стокам переключающих транзисторов, балансный транзистор, исток которого соединен с истоком первого нагрузочного транзистора, сток - с истоком второго нагрузочного транзистора, а затвор - с затворами нагрузочных транзисторов и второй шиной управления, конденсаторы, транзисторы регенерации, затворы которых объединены и подключены к третьей щине управления, а истоки соединены с одними обкладками конденсаторов, другие обкладки которых подключены к четвертой шине управления, отличающийся тем, что, с целью повышения степени интеграции устройства, в него введены четыре разделяющих транзистора, причем истоки первого и второго разделяющих транзисторов подключены к стоку первого переключающего транзистора, а истоки третьего и четвертого разделяющих транзисторов подключены к стоку второго переключающего транзистора, стоки первого и третьего разделяющих тран 2 @ зисторов подключены соответственно к стокам первого и второго транзисторов регене(Л рации, затворы первого и третьего, второго и четвертого разделяющих транзисторов подключены соответственно к пятой и щестой щинам управления, истоки разделяющих транзисторов являются информационными входами усилителя считывания. ас 4 00 00 со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4158241, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Усилитель считывания | 1978 |

|

SU769617A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-04-07—Публикация

1982-12-30—Подача