в ю

1 V

а

ff tf ч

а ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Дешифратор на МДП-транзисторах | 1983 |

|

SU1455362A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Параллельный дешифратор на допол-НяющиХ Мдп-ТРАНзиСТОРАХ" | 1978 |

|

SU798997A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Адресный формирователь | 1981 |

|

SU1007133A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

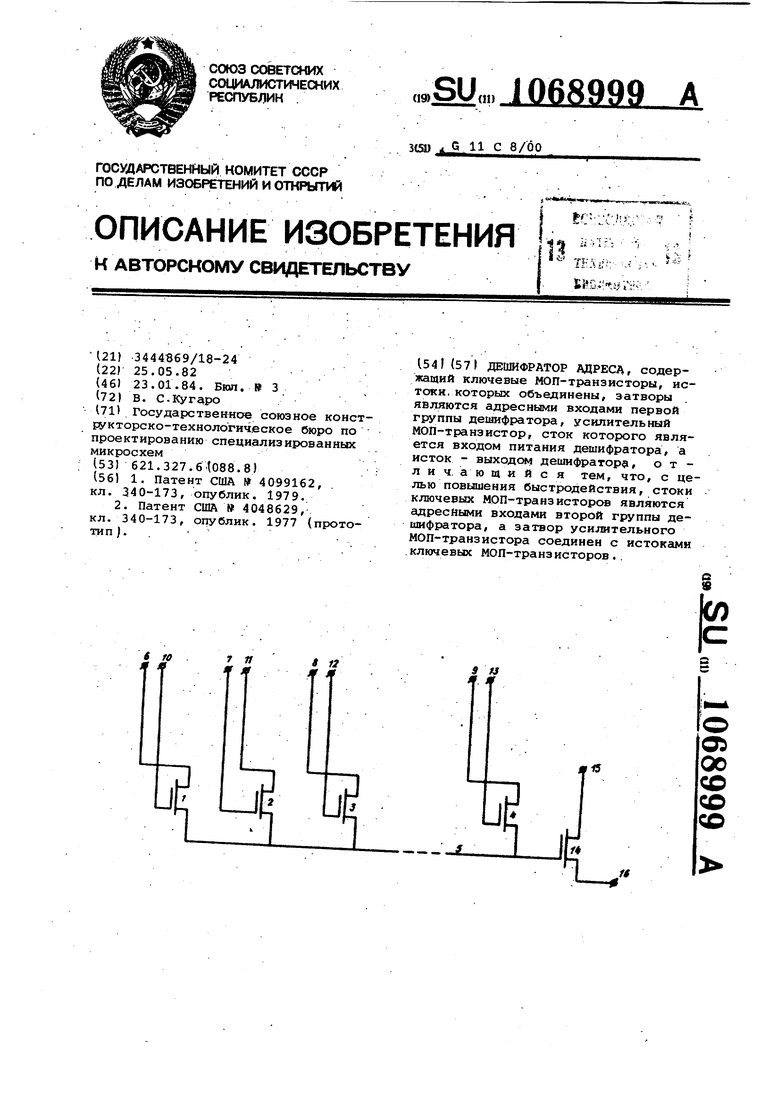

ДЕШИФРАТОР АДРЕСА, содержащий ключевые МОП-транзисторы, истокн. которых объединены, затворы являются адресными входами первой группы дешифратора, усилительный МОП-транзистор, сток которого является входом питания дешифратора, а исток - выходом дешифратора, о т ли ч а ю щ и и с я тем, что, с целью повышения быстродействия, стоки ключевых МОП-транзисторов являются адресными входами второй группы дешифратора, а затвор усилительного МОП-транзистора соединен с истоками ключевых МОП-транзисторов..

и

Изобретение, относится к микроэлектронике и может быть испольэовано в микросхемах памяти на МДП элементах. , В интегральных схемах памяти на МДП-транэисторах. в качестве дешифраторов адреса наибольшее, распространение получили элементы НЕ-ИЛИ, в ко торых используется принцип предзаряда а для активации выбранной шины применяются динамические повторители Использование предзаряжённых узлов позволяет исключить сквозное потребление в схеме деишфратора адреса и уменьшить время переключения венти. лей НЕ-ИЛИ, а применение, динамических повторителей повьдиает скорость заряда выбраннойвыходно.й .шины дешифратора ГЦ. Однако разряд затвора транзистора динамического повторителя невыб-. .ранного вентиля дешифратора происходит через проходной транзистор, раз.деляющий затвор транзистора динамического повторителя и шину, объединяющую ст-оки адресных транзисторов вент1шя НЕ-ИЛИ, и через открытые адресные транзисторы (в худшем случае через один открытый адресный транзистор), :т.е. процесс разряда относит.ельНОбольшой емкости затвог ра транзистора динамического повтори теля замедлен, .так как в судшем случае разряд емкости проходит через два транзистора. Кроме того, для. на дежного отделения емкости.затвора . транзистора .динамического повторите ля от емкости шины, объединяющей сто ки/адресных транзисторов, затворы проходнь1х транзисторов смещаются ис точником опорного напряжения или же тактируются специально формируемым импульсом, что усложняет схему де. шифратора и уменьшает скорость ее работы.. Наиболее близким к изобретению п технической сущности и схемному решению является дешифратор адреса, в котором управление затвором проходн го транзистора осуществляется при п мощи источника опорного напряжения, благодаря чему уменьшается опасност паразитного роста потенциала в невыбранном вентиле дешифратора прл условии неполного разряда емкости затвора динамического ловторителя и одновременном включении импульса, управляющего включением дешифратора С2, Дешифратор адреса обладает перечисленными выше недостатками, приче в нем НИНЫ адресных сигналов предва рительно разряжены. Заряд адресных шин при активации адресных буферов является относительно длительным процессом, что дополнительно снижае быстродействие известного дешифратор Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, то в дешифраторе адреса, содержащем ключевые МОП-транзисторы, истоки которых объединены, затворы являются адресными входами первой группы дешифратора, усилительный МОП-транзи-J стор, сток которого является входом питания дешифратора, а исток - выходом дешифратора, затвор усилительного МОП-транзистора соединен с истоками ключевых МОП-транзисторов, стоки ключевых МОП-транзисторов являются адресными входами второй группы дешифратора ... На чертеже представлена принципиальная схема дешифратора на восемь выходов. Дешифратор адреса содержит ключевые МОП-транзисторы 1-4, истоки которых объединены шиной 5, шины 6-9 прямых адресных сигналов, шины 1013 инверсных адресных сигналов, усилительный МОП-транзистор 14, затвор которого соединен с шиной 5 , сток соединен с шиной 15 питания, а исток 16 является выходом дешифратора. Дешифратор работает следуклцим образом. .. В течение периода восстановления, т.е. когда нет-обращения к схеме памяти, все итиньз 6-13 адресных сигналов заряжены до потенциала логичес- . кой единицы и через транзисторы 1-4 заряжена шина 5, объединяющая истоки транзисторов и затвор транзистора-14., В течение периода восстановления на шине 15 тактового питания поддерживается уровень логического нуля, так что шина 16 выхода дешифратора адреса разряжена через открытый транзистор 14. При обращении к схеме питания на адресных шинах фррмируются сигналы, соответствующие принятой адресной информации. В тех вентилях дешифратора, где сток хотя бы одного .транзистора, например транзистора 2, подключен к адресной шине, на которой установлен потенциал логического нуля, шина, объединяющая истоки транзисторов, разряжается через этот ., транзистор (его затвор при этом подключен к шине адресного сигнала инверсного сигналу, тактирующему сток адресного транзистора, т.е. к шине,. на которой поддерживается потенциал логической единицы. В выбранном вентиле дешифратора., то есть в таком вентиле, где все затворы транзисторов подключены к адресным шинам, имеющим потенциал логического нуля, на шине, объединяющей истоки транзисторов, сохраняется потенциал логичес-. кой единицы. При появлении импульса тактового питания начинается заряд шины выхода дешифратора адреса, и

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4099162, | |||

| кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 4048629, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Способ получения субстантивных красителей | 1923 |

|

SU1541A1 |

Авторы

Даты

1984-01-23—Публикация

1982-05-25—Подача