Изобретение относится к области автоматики, 1вычислительной техни-ки и может найти применение в тактируемых узлах преобразования цифровой информации интегральиых схем па МДП структурах при /построении делителей частоты тактовых имлульсов.

Известен делитель частоты, содержащий три полевых МДП транзистора с индуцированным каналом, (первый из которых истоком, а ива других стоком .подключены к выходной шине, сток лервого транзистора соединен с шиной питания, а истслк второго - ,с затвором третьего. Затворы первого и второго транзисторов подключены к шинам тактовых импульсов.

Целью изобретения я-вляется повышение надежности работы делителя. Это достигается тем, .что между истоком третьего транзистора и обпдей шиной источника питания включен дополнительный транзистор, затвор которого связан с шиной входных сигналов.

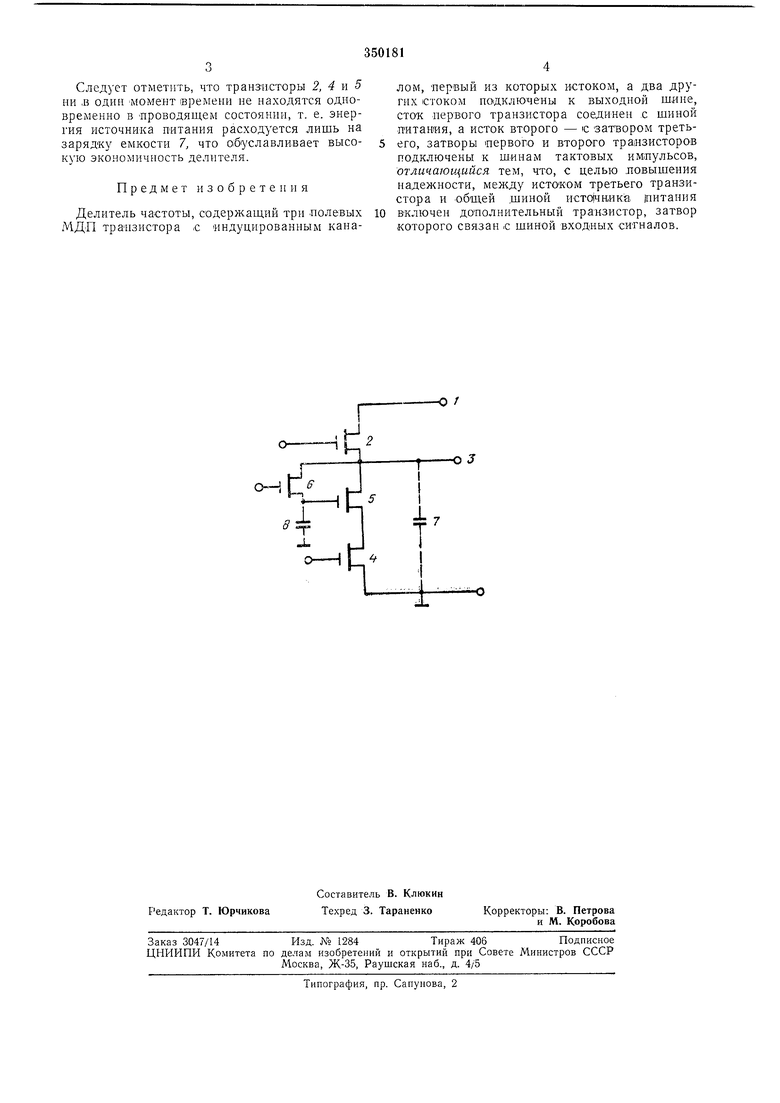

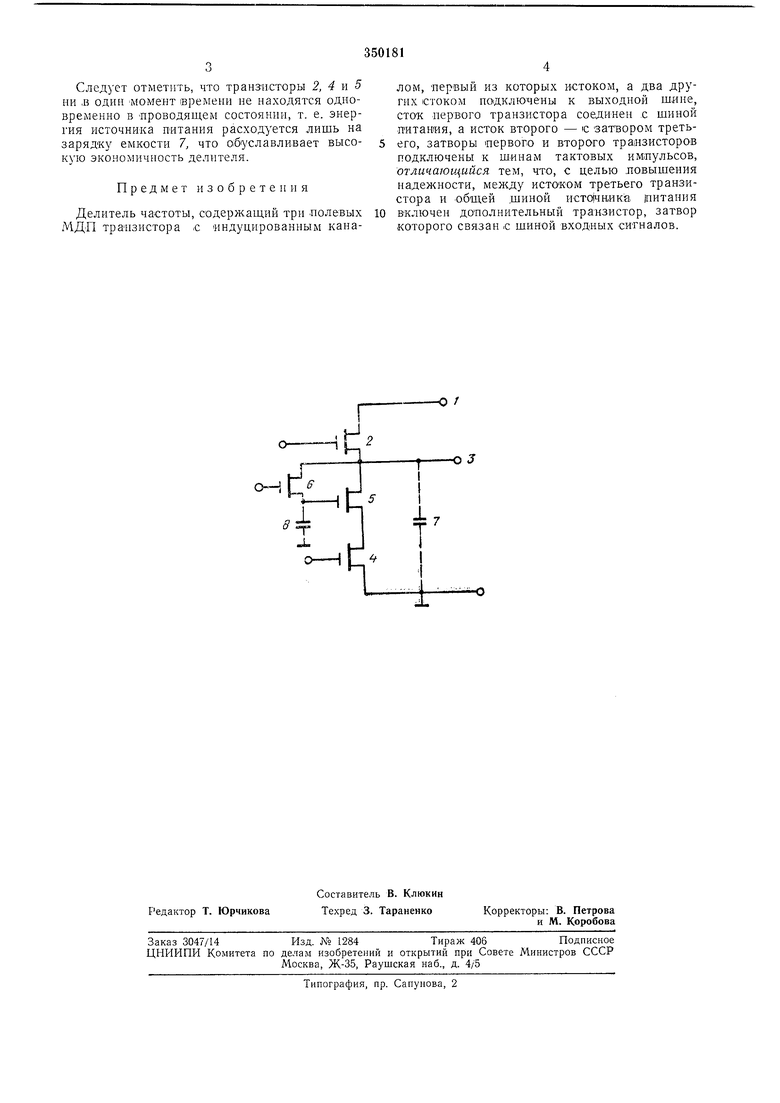

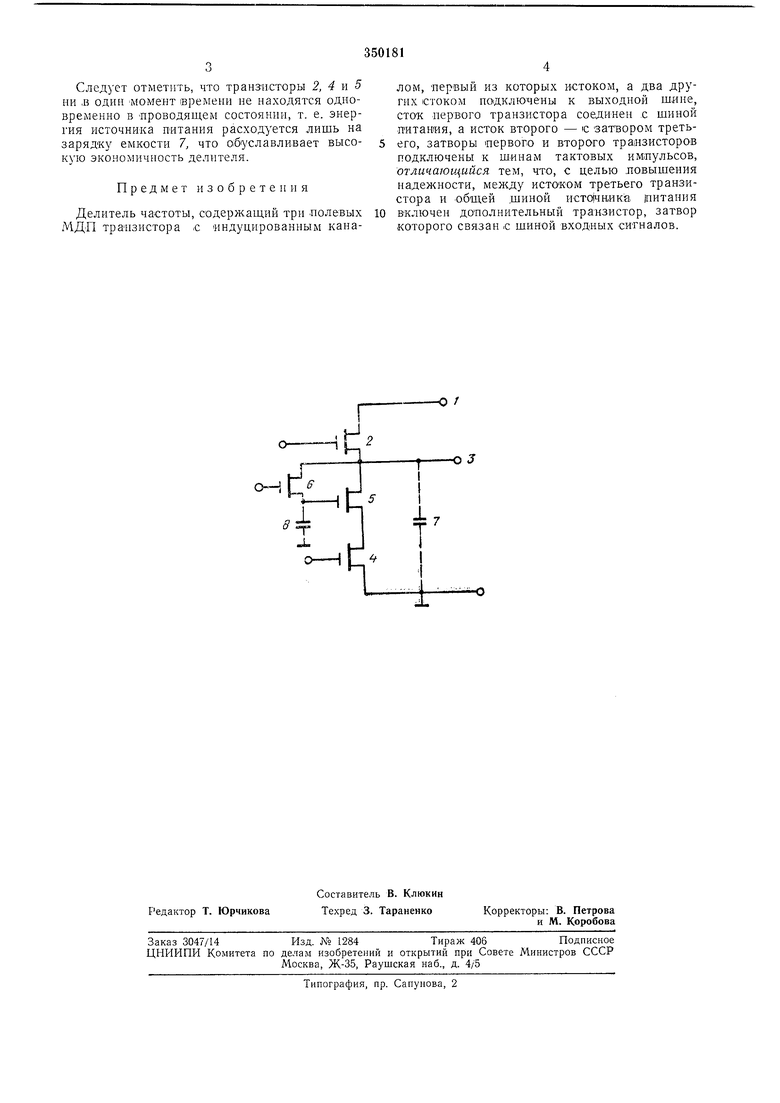

На чертеже показана принципиальная схема делителя.

В пачальный момент времени потенциалы всех точек схемы, кроме шины / и не-посредственно соединенного с ней стока транзистора 2, равны нулю.

Прохождение основного импульса иервого такта не влечет за собой изменения состоЯ:Н11я схемы, но запаздываюш,ий импульс этого такта открывает транзистор 2 и поднимает потенциал на выходе 3. При этом, ес,1и амплитуда имнульса превышает потенцпал шины / по крайней мере на величину порогового напряжения транзистора 2, уровень напряжения логической единицы равен -потенциалу шины /.

Входной им-пульс первого такта, поданный на затвор транзистора 4 вслед за окончанием запаздываюгцего пмпульса, не вызывает снижения выходного уровня, поскольку в это время транзистор 5 заперт.

Далее на затвор транзистора 6 приходит основной импульс второго такта. Транзистор 6 открывается и часть заряда поступает с емкости 7 на емкость 8, переводя транзистор 5 в ироводяшее состояние. При условии, что емкость § Семкости 7, уровень напряжения логической единицы суш,ественно не понижается, а кроме этого, он немедленно восстанавливается запаздывающим импульсом второго такта.

Очередной входной импульс открывает транзистор 4 и выходной уровень падает до нуля.

С началом третьего такта основной импульс открывает транзистор 6, емкость 8 (разряжается на емкость 7, но в снлу упомянутого условия (емкость 5 емкости7) это опять не вызывает существенного изменения выходного уровня. Схема возвращается в состояние, имевшее место до начала первого такта.

Следует отметить, что транзисторы 2, 4 и 5 ни .в один чмомент времени не находятся одновременно в -проводящем состоянин, т. е. энергия источника Иитания расходуется лишь на зарядку емкости 7, что обуславливает высокую экономичность делителя.

Предмет изобретения

Делитель частоты, содержащий три полевых МДП транзистора с индуцированным каналом, первый из которых истоком, а два других стоком нодключены к выходной щине, сток первого транзистора соединен с шиной питаиия, а исток второго - с затвором третьего, затворы первого и второго транзисторов подключены к щинам тактовых импульсов, отличающийся тем, что, с целью .повышения надежности, между истоком третьего транзистора и общей шиной исто|чник& )нитания Включен донолнительный транзистор, затвор которого связан с щиной входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1972 |

|

SU353353A1 |

| Г. И. Берлинков | 1972 |

|

SU345622A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Дешифратор адреса | 1978 |

|

SU741470A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| СЧЕТНЫЙ ТРИГГЕР НА МДН-ТРАНЗИСТОРАХ | 1973 |

|

SU369717A1 |

О J

Даты

1972-01-01—Публикация