Изобретение относится к области автоматики и вычислительной техники.

Известен делитель частоты на полевых МДП транзисторах с индуцированным каналом, содержащий два последовательно соединенных транзистора и транзистор обратной связи. Такой делитель сложен, что связано с большим количеством элементов, используемых для реализации схемы; и имеет большую величину потребляемой мощности.

Целью изобретения является упрощение схемы и снижение потребляемой мощности делителя частоты. Это достигается тем, что последовательно соединенные транзисторы включены между двумя шинами импульсного питания, затвор и сток одного из этих транзисторов подсоединены к одной из шин импульсного питания, а между затвором и стоком другого транзистора включен транзистор обратной связи, затвор которого связан с шиной входных сигналов, а сток - с шиной выходных сигналов.

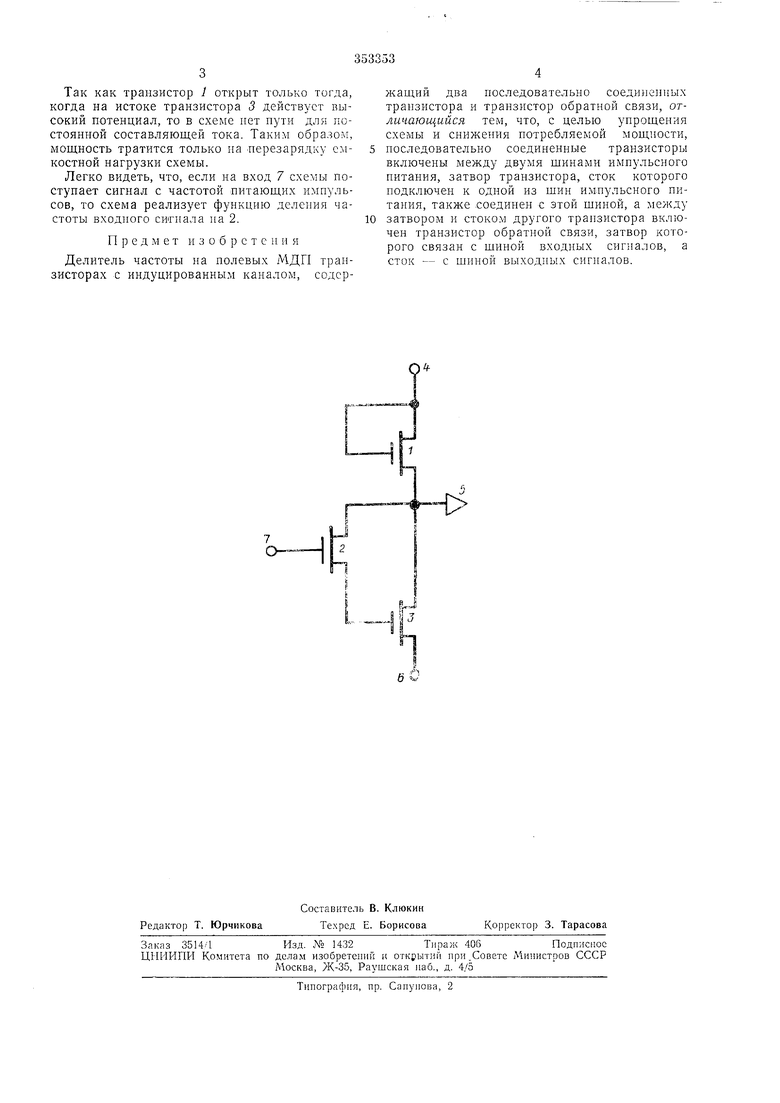

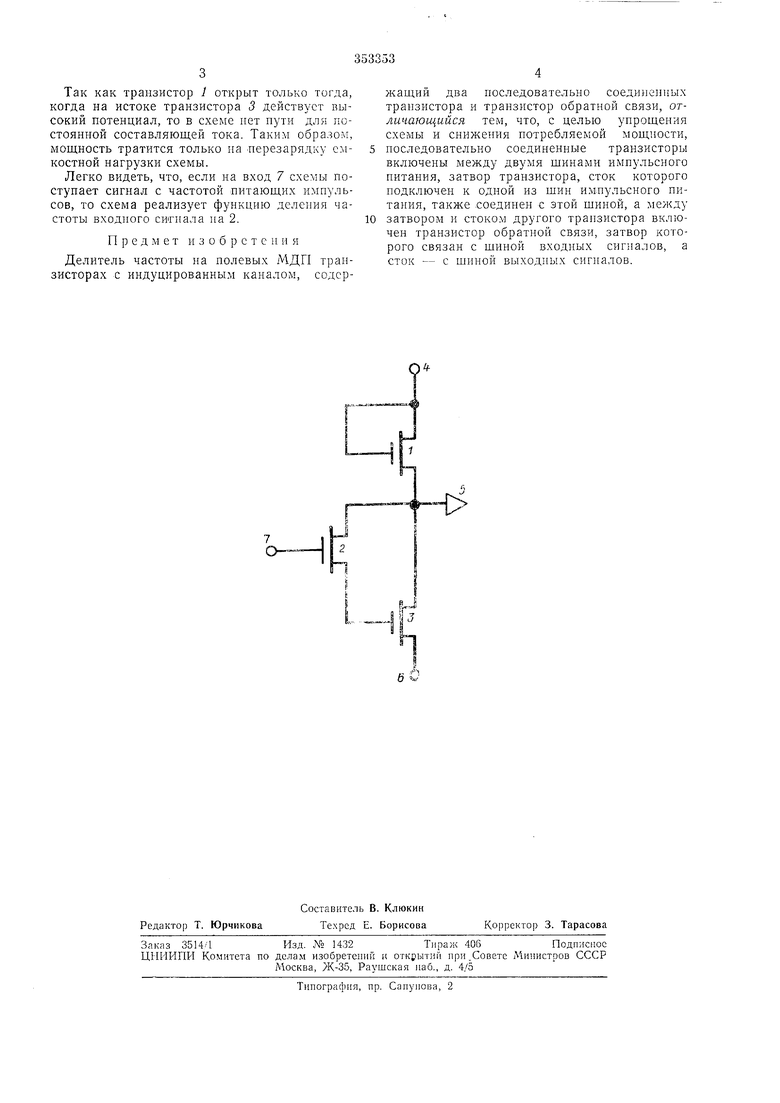

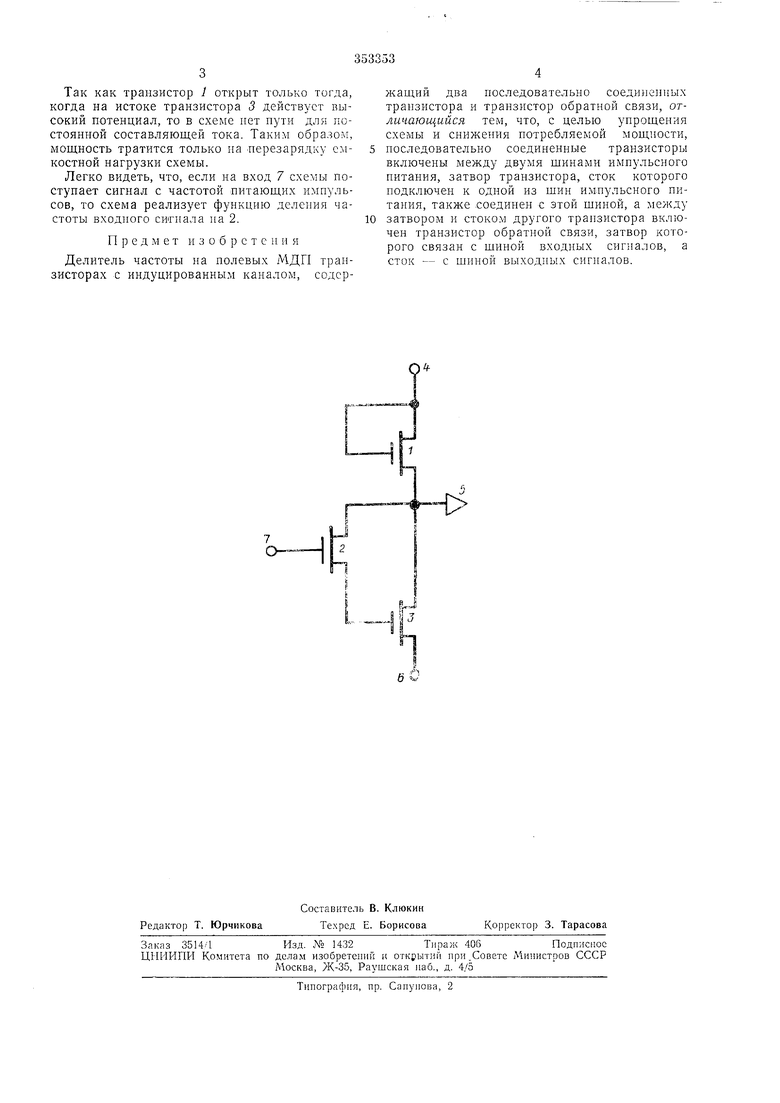

Иа чертеже показана принципиальная схема делителя частоты.

Схема построена на полевых МДП транзисторах 1, 2 Н 3 с индуцированным каналом. Транзисторы / и 5 последовательно соединены в цепочку, а транзистор 2 является транзистором обратной связи.

В исходном положении все узлы схемы имеют низкий потенциал (потенциал общей шины источника питания).

Когда приходит импульс на шину 4 питания, выход 5 схемы заряжается через транзистор 1. Так как при этом транзистор 2 закрыт, то на затворе транзистора 3 сохраняется низкий потенциал. По окончании действия импульса на шине 4 спадает потенциал на истоке транзистора 3, однако он остается закрытым, и высокий уровень сигнала на выходе схемы сохраняется. Когда приходит входной сигнал на затвор

транзистора 2, последний открывается, и на затвор транзистора 3 передается высокий уровень напряжения с выхода схемы. При эгом необходимо, чтобы емкость выхода схемы зпачительно превышала емкость затвора тра)1зистора 3. На выходе схемы по-преж){ему сохраняется высокий уровень напряжения, так как на истоке транзистора 3 действует высокий потенциал.

Когда приходит очередной импульс на шину 4, выходная емкость с.хемы подзаряжается, а по окончании этого сигнала и уменьшения до нуля потенциала на шине 6 питапия разряжается через транзистор 3 и внутреннее сопротивление генератора импульсов питания,

Так как транзистор 1 открыт только тогда, когда на истоке транзистора 3 действует высокий потенциал, то в схеме нет нути дл постоянной составляющей тока. Таким образом, мощность тратится только иа .перезарядку емкостной нагрузки схемы.

Легко видеть, что, если на вход 7 схемы поступает сигнал с частотой питающих нмпульсов, то схема реализует функцию деления частоты входного сигнала иа 2.

Предмет изобретения

Делитель частоты на нолевых МДП транзисторах с индуцированным каналом, содержащий два последовательно соединенных транзистора и транзистор обратной связи, отличающийся тем, что, с целью упрощения схемы и снижения потребляемой мощности, последовательно соединенные транзисторы включены между двумя шинами импульсного питания, затвор транзистора, сток которого подключен к одной из шин импульсного питания, соединен с этой шиной, а Л1ежду затвором и стоком другого транзистора включен транзиетор обратной связи, затвор которого связан с шиной входных сигналов, а сток - с шиной выходных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Г. И. Берлинков | 1972 |

|

SU345622A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU396718A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1972 |

|

SU350181A1 |

| СЧЕТНЫЙ ТРИГГЕР НА МДН-ТРАНЗИСТОРАХ | 1973 |

|

SU369717A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

Даты

1972-01-01—Публикация