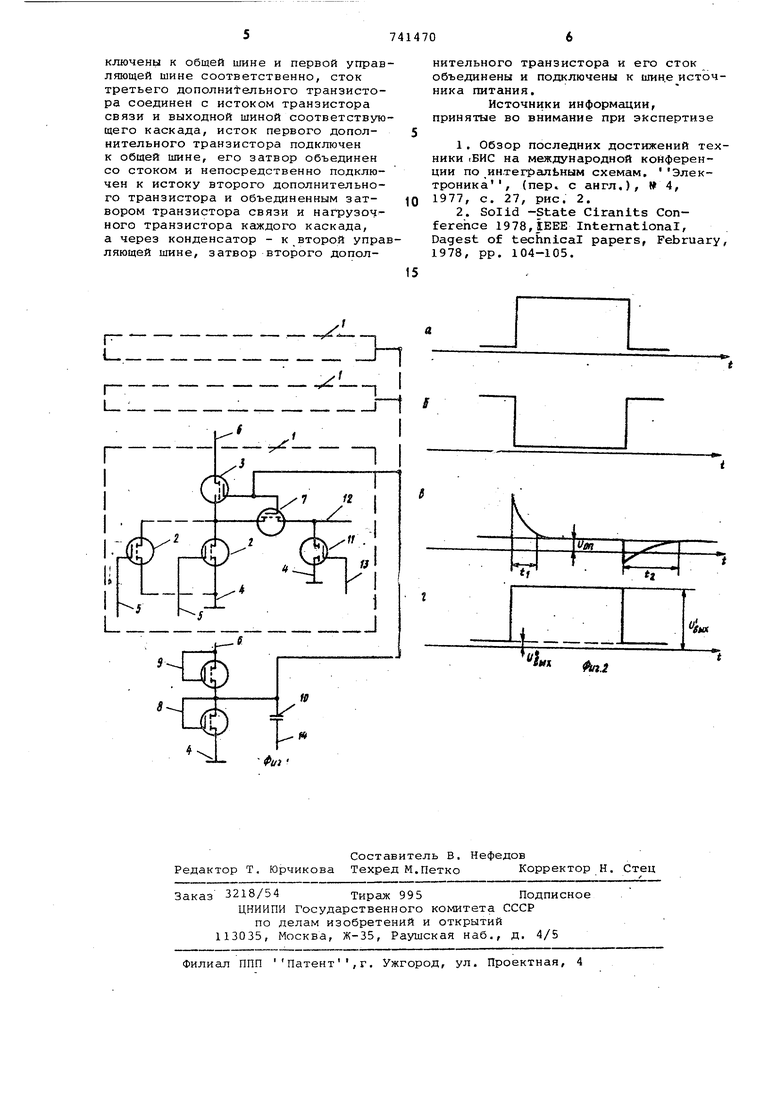

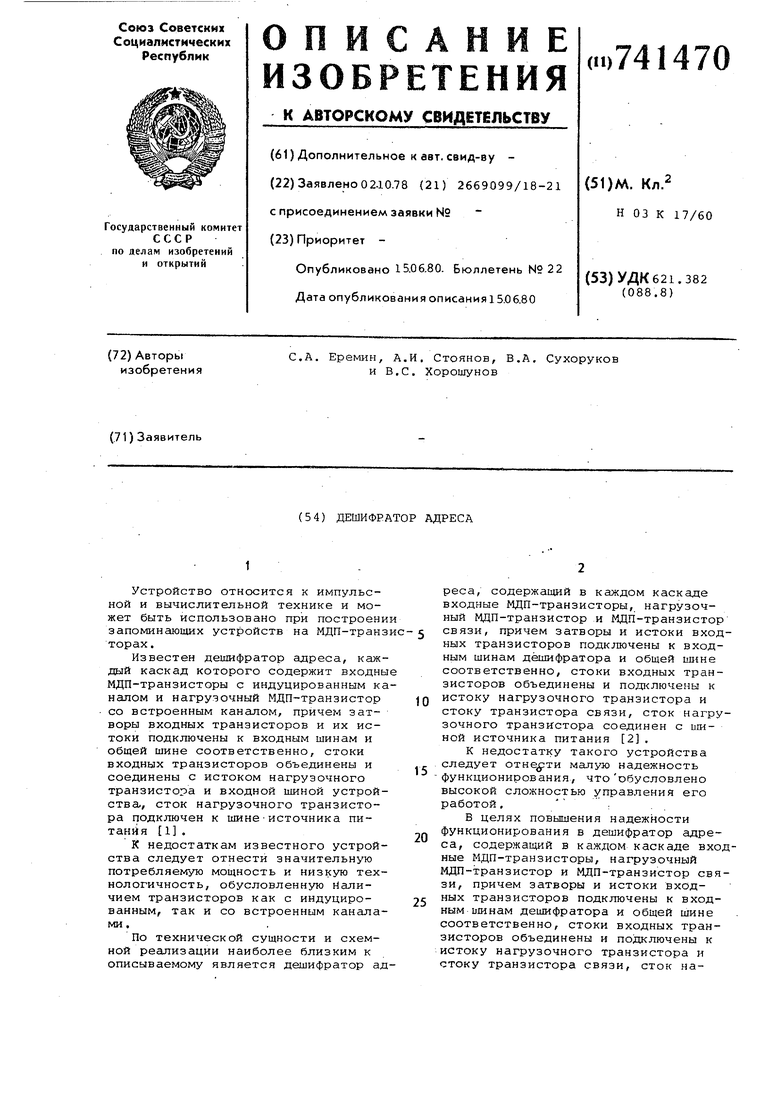

Устройство относится к импульсной и вычислительной технике и может быть использовано при построени запоминающих устройств на МДП-тран торах. Известен дешифратор адреса, каж дый каскад которого содержит входны МДП-транзисторы с индуцированным к налом и нагрузочный МДП-транзистор со встроенным каналом, причем затворы входных транзисторов и их истоки подключены к входным шинам и общей шине соответственно, стоки входных транзисторов объединены и соединены с истоком нагрузочного транзистора и входной шиной устрой ства, сток нагрузочного транзистора подключен к шинеисточника питания 1 . К недостаткам известного устрой ства следует отнести значительную потребляемую мощность и низкую тех нологичность, обусловленную Наличием транзисторов как с индуцированным, так и со встроенным канала ми . По технической сущности и схемной реализации наиболее близким к описываемому является дешифратор а реса, содержащий в каждом каскаде входные МДП-транзисторы, нагрузочный МДП-транзистор и МДП-транзистор связи, причем затворы и истоки входных транзисторов подключены к входным шинам дешифратора и общей ишне соответственно, стоки входных транзисторов объединены и подключены к истоку нагрузочного транзистора и стоку транзистора связи, сток нагрузочного транзистора соединен с шиной источника питания 2. К недостатку такого устройства следует отнести малую надежность функционирования, что обусловлено высокой сложностью управления его работой, : В целях повышения надежности функционирования в дешифратор адреса, содержащий в каждом каскаде входные МДП-транзисторы, нагрузочный МДП-транзистор и МДП-транзистор связи, причем затворы и истоки входных транзисторов подк.шочены к входным иш нам дешифратора и общей шине соответственно, стоки входных транзисторов объединены и подключены к истоку нагрузочного транзистора и стоку транзистора связи, сток нагрузочного транзистора соединен с шиной источника питания, введены конденсатор, дополнительные первый и второй МДП-транзисторы и в каждый каскад третий дополнительный МДП-транзистор, Причем исток и затвор третьего дополнительного тран зистора подключены к.общей шине и пе вой управляющей шина соответственно сток третьего дополнительного транзистора соединен с истоком транзистора связи и выходной шиной соответствующего каскада, исток первого дополнительного транзистора подклю.чен к общей шине, его затвор объединен со стоком и непосредственно подключен к истоку второго дополнительного транзистора и объединенным затворам транзистора связи и на грузочного транзистора каждого каскада, а через конденсатор - к второй управляющей щине, затвор второго до полнительного транзистора и его сто объединены и подключены к шине источника питания. На фиг, 1 изображена принципиальная схема описываемого дешифратора а реса; на фиг,- 2 приведены временные диаграммы его работы. Дешифратор адреса содержит в каждом из N каскадов 1 N 2 входных тран зисторов 2, стоки которых объединены с истоком нагрузочных транзисторов Истоки транзисторов 2 подключены к общей шине 4, а затворы - к входным шинам 5, Сток нагрузочного транзисто подсоединен к шине источника питания 6, его затвор объединен с затвором транзистора 7 связи, с затвор и стоком первого дополнительного тр зистора 8 и с истоком второго допол нительного транзистора 9, образующих делитель напряжения, а также с перв выводом конденсатора 10. Затвор и сток транзистора 9 присоединены к ш не источника питания 6, Исток транзистора связи объединен со стоком третьего дополнительного транзистора 11 и присоединен к выходной шине 12, Затвор транзистора 11 подключен к первой управляющей шине 13,- а исток - к общей шине 4, к которой подключен также исток транзистора 8 Второй вывод конденсатора 10 подключен к второй управляющей шине 14, При использовании описываемого дешифратора для построения запомина щих устройств в качестве первой и . второй управляющих шин ..используются шина выбора кристалла и инверсная шина выбора кристалла соответственн Дешифратор адреса работает сле 1ующим образом. Транзисторы 8 и 9 образуют делитель напряжения питания, формирующий в средней точк напряжение Uon-U,iop,где Опор- пороговое напряжение транзисторов. Если на управляющих шинах 14 и 13 присутствуют сигналы низкого и высокого уровней соответственно (фиг, 2а и б), то транзисторы 3 и 7 заперты. Транзистор 11 открыт и на выходной шине 12 каскада - низкий уровень напряжения,. Потребление каскадом мощности от источника питания 6 отсутствует. При поступлении на шины 14 и 13 высокого и низкого уровней напряжения соответственно транзистор 11 закрывается. Напряжение на затворах транзисторов 3 и 7 скачкообразно возрастает на величину амплитуды сигнала на шине 14 (фиг, 2в), и открываются транзисторы 3 и 7, Когда все транзисторы 2 заперты на выходной шине 12 каскада формируется высокий уровень напряжения (фиг, 2 г - сплошная линия). Через промежуток времени -fc j длит ельность которого определяется значением емкости конденсатора 10 и значением крутизны транзистора 8, напряжение на затворах транзисторов 3 и 7 уменьшается до величины и„ор, транзисторы запираются, что обеспечивает сохранение на выходной шине высокого уровня напряжения. Когда хотя бы один из входных транзисторов открыт, на выходной шине 12 формируется и сохраняется низкий уровень напряжения (фиг. 2гпунктирная линия). Так же как и в первом случае через промежуток времени t входную адресную информацию можно менять - напряжение на выходной шине сохраняется. Через время -Ь„ после снятия сигнала высокого уровня с шины 14 дешифратор адреса готов к повторному циклу работы, , Простота управления и незначительная мощность, потребляемая в статическом состоянии, обусловливают высокую надежность функционирования дешифратора. Формула изобретения Дешифратор адреса, содержащий в каждом каскаде -входные МДП-транзисторы, нагрузочный МДП-транзистор и МДП-транзистор связи, причем затворы и истоки входных транзисторов подключены к входным шинаЕм дешифратора ,и общей шине соответственно, стоки входных траййИсторов объединены и подключены к истоку нагрузочного транзистора и стоку транзистора связи, сток нагрузочного транзистора соединен с шиной источника питания, отличающийся тем, что, с целью повышения надежности функционирования, в него бведены конденсатор, дополнительные первый и второй МДП-транзисторы и в каждый каскад третий дополнительный МДП-транзистор, причем исток и затвор третьего дополнительного транзистора подключены к общей шине и первой управляющей шине соответственно, сток третьего дополнительного транзистора соединен с истоком транзистора связи и выходной шиной соответствующего каскада, исток первого дополнительного транзистора подключен к общей шине, его затвор объединен со стоком и непосредственно подключен к истоку второго дополнительного транзистора и объединенным затвором транзистора связи и нагрузоч ного транзистора каждого каскада, а через конденсатор - к второй управляющей шине, затвор второго дополнительного транзистора и его сток объединены и подключены к шин.е источника питания.

Источники информации, принятые во внимание при экспертизе

1.Обзор последних достижений техники iBHC на международной конференции по ин.тегралЬным схемам, Электроника, (пер. с англ.), 4,

1977,с. 27, рис. 2.

2.Solid -State Ciranits Conference 1978,IEEE International, Dagest of technical papers, February,

1978,pp. 104-105.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор адреса | 1980 |

|

SU938408A1 |

| Инвертор на мдп-транзисторах | 1976 |

|

SU646441A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Динамический инвертор на МДП-транзисторах | 1982 |

|

SU1080210A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Матричный накопитель для полупроводникового запоминающего устройства | 1978 |

|

SU729636A1 |

«j

tun

.i

Авторы

Даты

1980-06-15—Публикация

1978-10-02—Подача