I

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки сложных логических блоков на этапе серийного производства.

Известно устройство для контроля дискретных логических схем, содержащее генератор импульсов, двоичный счетчик, разделительные схемы, схему контроля уровней, компаратор, преобразователь, формирователь уровней, элементы И, ИЛИ, ИЛИ-НЕ о индикаторные элементы 1.

Недостат1 и этого устройства - ограниченные функциональные возможности и низкое быстродействие, так как в каждый момент времени ведется контроль только одного блока с помощью тестов, которые генерируются с помощью двоичного счетчика, и при этом отсутствует возможность оперативно изменять последовательность прохождения тестов.

Наиболее близким техническим рещени- 20 ем к изобретению является устройство для контроля логических блоков, содержащее блок ввода, блок памяти, коммутатор, блок сравнения, блок индикации, регистр настройки, блок управления. Первый выход блока ввода соединен со входом блока памяти, выход которого подключен к первому входу коммутатора, выходами соединенного с внещними контактами контролируемого узла, второй выход блока ввода соединен со входом блока управления, выходы которого подключены соответственно к управляющим входам блока ввода, блока памяти, регистра настройки и блока индикации, соединенного входом с выходом блока сравнения. Вход регистра настройки соединен с первым выходом блока ввода, а выход - со вторым входом коммутатора, выход блока Памяти подключен к первому входу блока сравнения, второй вход которого соединен с выходом коммутатора 2.

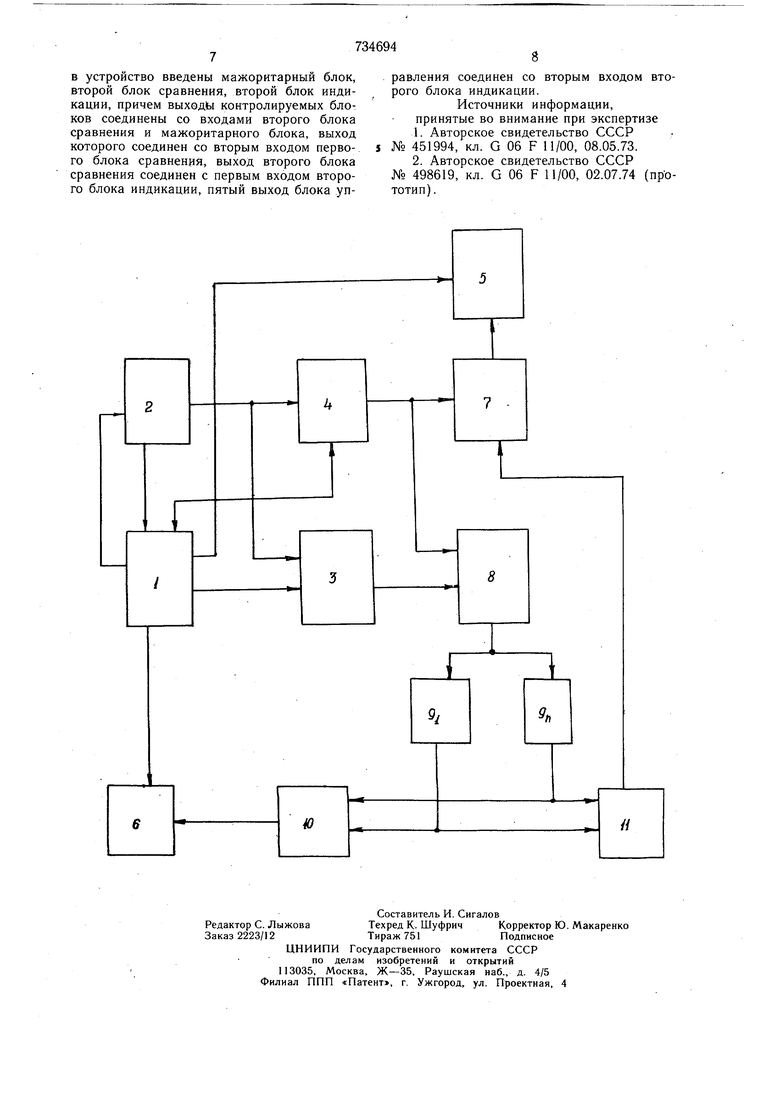

Это устройство обладает недостаточной достоверностью контроля, так как точность контроля зависит от таких факторов, как случайные сбои в работе блока ввода, коммутатора и блока сравнения. Кроме того, такое устройство контроля неэффективно при использовании в серийном производстве сложных микроэлектронных логических блоков, так как для одновременного контроля п-идентичных логических блоков необходимо наличие для каждого из них п-отдельных подобных устройств, что значительно усложняет и удорожает всю систему контроля в целом. Цель изобретения - повышение производительности устройства. Поставленная цель достигается тем, что в устройство для контроля логических блоков, содержащее блок ввода, блок управления, регистр настройки, блок памяти, первый блок индикации и коммутатор, причем первый, второй, третий и четвертые выходы блока управления соединены соответственно со входом блока ввода, с управляющим входом блока памяти, с первым входом первого блока индикации, с первым входом регистра настройки, выход которого соединен с первым входом коммутатора, выход коммутатора соединен со входами контролируемых блоков, первый и второй выходы блока ввода соединены соответственно со входом блока управления, с информационным входом блока памяти, выход которого соединен с первым входом первого блока сравнения и со вторым входом коммутатора, выход первого блока сравнения соединен со вторым входом первого блока индикации, второй выход блока ввода соединен со вторым входом регистра настройки, введены мажоритарный блок, второй блок сравнения, второй блок индикации, причем выходы контролируемых блоков соединены со входами второго блока сравнения и мажоритарного блока, выход которого соединен со вторым входом первого блока сравнения, выход второго блока сравнения соединен с первым входом второго блока индикации, пятый выход блока управления соединен со вторым входом второго блока индикации. На чертеже представлена схема устройства для контроля логических блоков. Устройство содержит блок 1 управления, выходы которого подключены к управляющим входам блока 2 ввода, регистра 3 настройки, блока 4 памяти, первого 5 и второго 6 блока индикации. Блок 2 ввода предназначен для ввода тестовой программы с внешнего программного устройства, информации входных и выходных контактов объекта контроля и командной информации, одним выходом соединен со входами регистра 3 настройки, блока 4 памяти и блока 1 управления, выход блока 4 памяти подключен ко входу первого блока 7 сравнения и второму входу коммутатора 8, первый вход которого связан с выходом регистра 3 настройки, а выход соединен со входами проверяемых блоков 9п, выходы проверяемых блоков подключены ко входам второго блока 10 сравнения и входам мажоритарного блока 11, выход которого соединен со вторым входом блока 7 сравнения. Выходы блоков 7 и 10 сравнения подключены соответственно ко входам блоков 5 и 6 индикации. Мажоритарный блок 11 предназначен для выбора сигнала, наиболее часто всречающ ося на одноименном контакте по всем проверяемым блокам в конкретном элементарном тесте. Сравнение информации на выходе мажоритарного блока 11 с эталонной информацией, хранящейся в памяти блока 4, осуществляется первым блоком 7 сравнения. Второй блок 10 сравнения предназначен для сравнения между собой сигналов на выходных контактах проверяемых блоков 9i-9п. Контроль проверяемых блоков осуществляется с помощью тестов, состоящих из последовательности элементарных тестов, разрядность которых равна числу внешних контактов одного проверяемого блока. Каждый элементарный тест включает в себя стимулы и эталоны (стимулы - совокупность сигналов, одновременно подаваемых на входные контакты; эталоны - совокупность сигналов, которые должны появиться на выходах исправных блоков при подаче на нх входы стимулов). принцип работы в предлагаемом устройстве основан на поразрядном сравнении логических сигналов со всех контактов проверяемых блоков с эталонными, задаваемыми программой проверки, а также на поразрядном их сравнении между собой. В частном случае один из проверяемых блоков может быть установлен заведомо исправным, т. е. может служить аппаратным эталоном для остальных блоков. Устройство работает следующим образом. На блоке 1 управления последовательно нажимаются кнопки «Сброс, «Программа, «Пуск и соответственно вырабатываются команды. По команде «Сброс осуществляется обнуление устройства перед началом работы. По команде «Программа идет запись в блок 4 памяти номеров этапов начала и конца полного цикла тестовой информации для конкретных проверяемых блоков. По команде «Пуск происходит обращение к внешним программным устройствам, команд ная информация из блока 2 ввода поступает в блок 1 управления и в соответствии с ней идет запись информации о назначении внешних контактов проверяемых блоков в регистр 3настройки и тестовой информации в блок 4памяти. После окончания данного первого этапа, который заключается в разделении входов и выходов и записи тестовой информации, начинается считывание тестовой информации из блока 4 памяти, очередной элементарный тест из блока памяти поступает на первый вход первого блока 7 сравнения и вход коммутатора 8, коммутатор выдает входные воздействия стимулов на проверяемые блоки 9i-9п. Работой коммутатора 8 управляет регистр 3 настройки, в котором хранится информация о назначении внешних контактов проверяемых блоков. Реакция проверяемых блоков, т. е. сигналы, характеризующие реальные состояния всех логических выходов, вместе со стимулами поступает в мажоритарный блок 11, с выхода которого информация поступает на вход первого блока 7 сравнения, и на вход второго блока 10 сравнения. Блоки 7 и 10 сравнения выдают результат контроля в виде двухальтернативного решения «Годен-Брак. Если результат сравнения «Годен на обоих блоках сравнения, то продолжается дальнейшая проверка блоков. Снова подается команда обращения к внешним программным устройствам и очередной элементарный тест записывается в блок 4 памяти, следует новая подача входного воздействия на проверяемые блоки, вновь осуществляется сравнение и анализ сигналов и стимулов со всех внещних контактов проверяемых блоков между собой на блоке 10 и с эталонными значениями, хранящимися в блоке 4 памяти, на блоке 7 сравнения. Если результат сравнения «Брак в одном из блоков сравнения или в обоих сразу, то производится останов проверки, по которому прекращается обращение к внешним программным устройствам, запрещается стирание информации из блока 4 памяти и ввод новой. Блок 5 индикации отображает при этом адреса (номера) контактов, по которым выдается результат «Брак из блока 7 сравнения, и номер этапа, на котором произощло Данное несравнение. Блок 6 индикации отображает адреса (номера) контактов, по которым выдается результат «Брак из блока 10 сравнения и номер того проверяемого блока (блоков), по вине которого (которых) происходит несравнение. с помощью переключателя «Контроль на передних панелях блоков 5 и 6 индикаций коммутируются табло «Адрес неисправноети. При установке переключателя в положение «Тест в блоке 5 индикации на табло индицируется эталонная информация о всех контактах проверяемых блоков, а при установке переключателя «Контроль в блоке б индикации в положении «Выход 1 индицируется информация со всех контактов первого проверяемого блока 9 i, при установке в положение «Выход п - информация со всех контактов проверяемого блока 9 . В положении данного переключателя «Брак на обоих блоках 5 и 6 индикации отображается информация о тех контактах, которые дают брак при сравнении стимулов и сигналов в блоках 7 и 10 сравнения соответственно. Табло «Годен -«Брак отображает состояние проверяемых блоков и, кроме того, данное табло в блоке б индикации индицирует номер того блока (блоков), информация с которого (которых) в данном 4 элементарном тесте отличается от информации других проверяемых блоков. После анализа места и характера неисправности оператор, по своему усмотрению, может прекратить дальнейшую проверку с целью ликвидации неисправности или продолжить проверку с целью выявления, по крайней мере, одного абсолютно исправного (эталонного) проверяемого блока. Переход к следующему этапу проверки после останова осуществляется командой «Шаг из блока 1 управления. При этом снимается «Останов, и в блок 4 памяти вводится новая тестовая информация и стирается старая. В устройстве предусмотрен циклический режим работы, при котором любая группа элементарных тестов циклически подается на входы проверяемых блоков 9i-9п, что позволяет проследить, например, с помощью осциллографа или логического щупа-индикатера прохождение сигналов по внутренним цепям проверяемых блоков и методом сравнения с эталонным определить место и характер неисправности. Таким образом, предлагаемое устройство позволяет обеспечить контроль проверяемых блоков с повыщенной достоверностью, значительно облегчает поиск неисправности внутри блока путем простого сравнения контролируемых точек с одноименными точками других блоков, позволяет проверить одновременно п идентичных блоков, что существенно повыщает эффективность использования всего оборудования, входящего в данное; устройство, в сравнении с известными устройствами контроля логических блоков. Формула изобретения Устройство для контроля логических блоков, содержащее блок ввода, блок управления, регистр настройки, блок памяти, первый блок индикации и коммутатор, причем первый, второй, третий и четвертые выходы блока управления соединены соответственно со входом блока ввода, с управляющим входом блока памяти, с первым входом первого блока индикации, с первым входом регистра настройки, выход которого соединен с первым входом коммутатора, выход коммутатора соединен со входом контролируемых блоков, первый и второй выходы блока ввода соеди-нены соответственно со входом блока управления, с информационным входом блока памяти, выход которого соединен с первым входом первого блока сравнения и со вторым входом коммутатора, выход первого блока сравнения соединен со вторым входом первого блока индикации, второй выход блока ввода соединен со вторым входом регистра настройки, отличающееся тем, что, с целью повышения производительности.

в устройство введены мажоритарный блок, второй блок сравнения, второй блок индикации, причем выходЬ контролируемых блоков соединены со входами второго блока сравнения и мажоритарного блока, выход которого соединен со вторым входом первого блока сравнения, выход второго блока сравнения соединен с первым входом второго блока индикации, пятый выход блока управления соединен со вторым входом второго блока индикации.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 451994, кл. G 06 F 11/00, 08.05.73.

2.Авторское свидетельство СССР

№ 498619, кл. G 06 F 11/00, 02.07.74 (прЪтотип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1974 |

|

SU498619A1 |

| Устройство для контроля логическихблОКОВ | 1978 |

|

SU813430A1 |

| Устройство для контроля цифровых узлов | 1977 |

|

SU643876A2 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU932497A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1247898A2 |

Авторы

Даты

1980-05-15—Публикация

1978-01-13—Подача