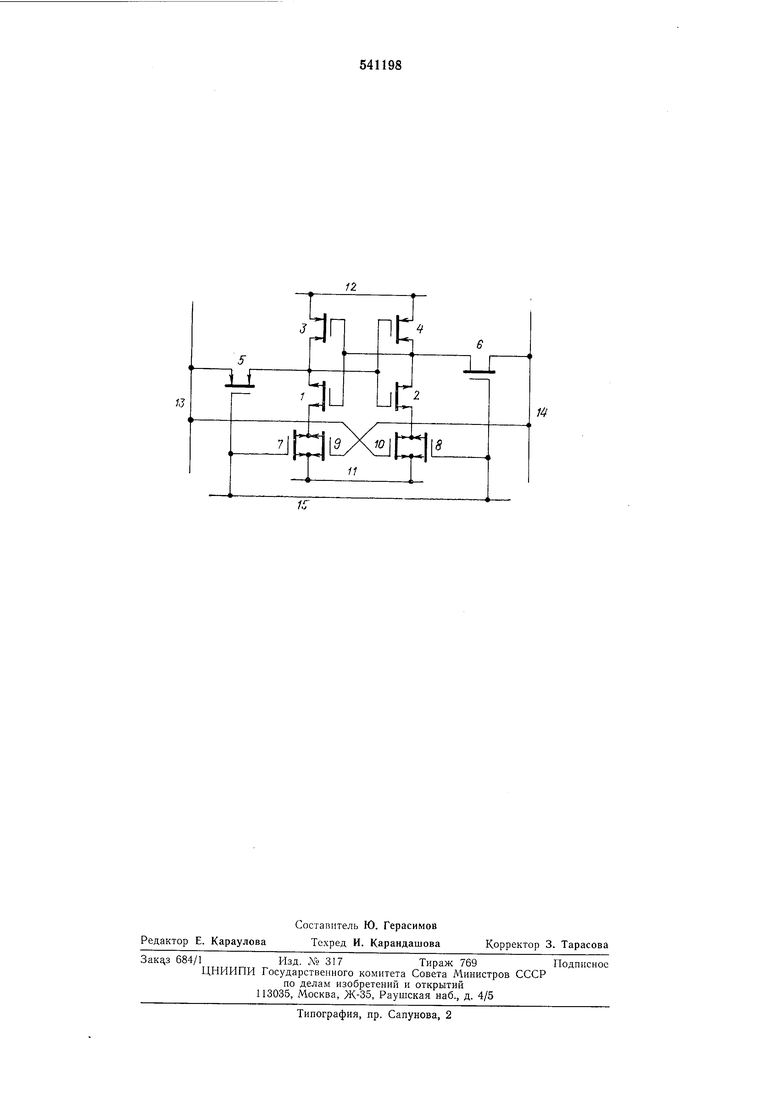

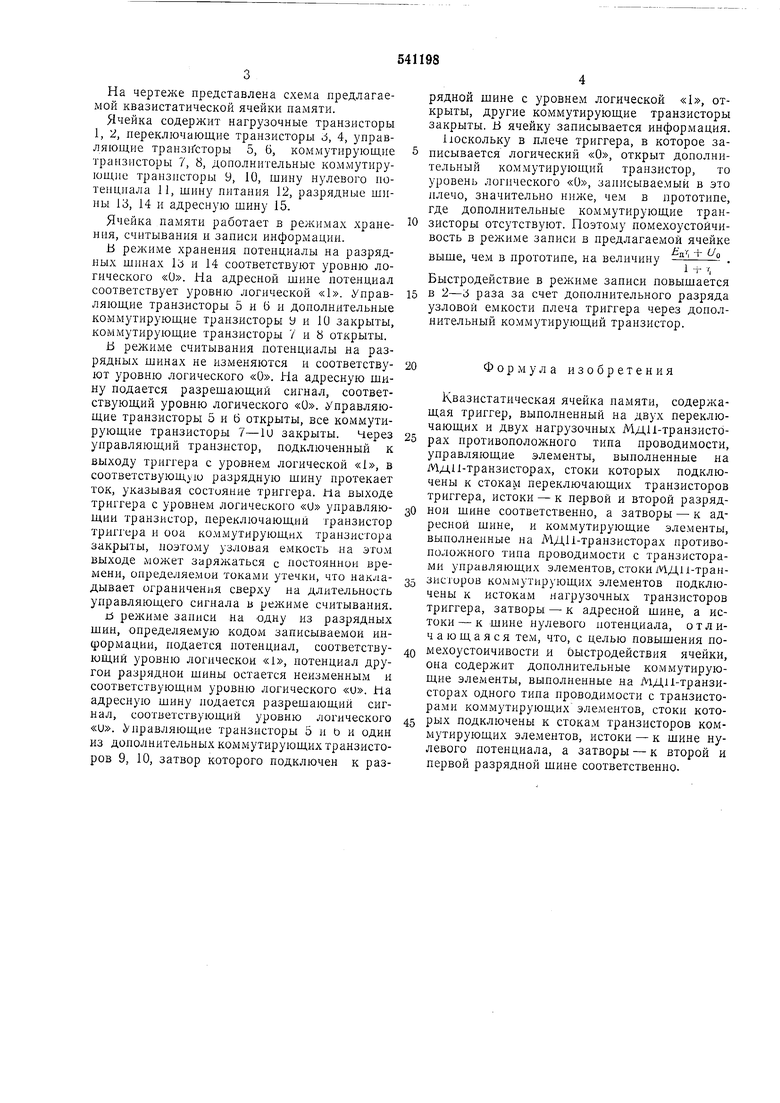

На чертел е представлена схема предлагаемой квазистатической ячейки памяти.

Ячейка содержит нагрузочные транзисторы 1, 2, переключающие транзисторы 6, 4, управляющие транзисторы 5, 6, коммутирующие транзисторы 7, 8, дополнительные коммутирующие транзисторы 9, 10, шину нулевого иотенциала 11, шину питания 12, разрядные шины 13, 14 и адресную шину 15.

Ячейка памяти работает в режимах хранения, считывания и записи информации.

В режиме хранения потенциалы на разрядных шинах 15 и 14 соответствуют уровню логического «О. На адресной шине потенциал соответствует уровню логической «1. Управляющие транзисторы 5 и b и дополнительные коммутирующие транзисторы У и 10 закрыты, коммутирующие транзисторы 7 и 8 открыты.

И режиме считывания потенциалы на разрядных шинах не изменяются и соответствуют уровню логического «О. На адресную шину подается разрешающий сигнал, соответствующий уровню логического «О. Управляющие транзисторы 5 и б открыты, все коммутирующие транзисторы 7-1и закрыты. Через управляющий транзистор, подключенный к выходу триггера с уровнем логической «1, в соответствующую разрядную шину протекает ток, указывая состояние триггера, rta выходе триггера с уровнем логического «U управляющий транзистор, переключающий транзистор триггера и ооа коммутирующих траизистора закрыты, поэтому узловая емкость на этом выходе может заряжаться с постоянной времени, определяемой токами утечки, что накладывает ограничения сверху на длительность управляющего сигнала в режиме считывания, ь режиме записи на одну из разрядных щин, определяемую кодом записываемой информации, подается потенциал, соответствующий уровню логической «1, потенциал другой разрядной шины остается неизменным и соответствующим уровню логического «и. На адресную шину подается разрешающий сигнал, соответствующий уровню логического «и. Управляющие транзисторы 5 и D и один из дополнительных коммутирующих транзисторов 9, 10, затвор которого подключен к разрядной шине с уровнем логической «1, открыты, другие коммутирующие транзисторы закрыты. Б ячейку записывается информация. Поскольку в плече триггера, в которое записывается логический «О, открыт дополнительный коммутирзющий транзистор, то уровень логического «О, записываемый в это плечо, значительно ниже, чем в прототипе, где дополнительные коммутирующие транзисторы отсутствуют. Поэтому помехоустойчивость в режиме записи в предлагаемой ячейке

п| + 0

выще, чем в прототипе, на величину .

Быстродействие в режиме записи повыщается в 2-6 раза за счет дополнительного разряда узловой емкости плеча триггера через дополнительный коммутирующий транзистор.

Формула изобретения

20

Квазистатическая ячейка памяти, содержащая триггер, выполненный на двух переключающих и двух нагрузочных МДН-транзистоpax противоположного типа проводимости, управляющие элементы, выполненные на Мди-транзисторах, стоки которых подключены к стокам переключающих транзисторов триггера, истоки - к первой и второй разрядНОИ щипе соответственно, а затворы - к адресной шине, и коммутирующие элементы, выполненные на МДН-транзисторах противоположного типа проводимости с транзисторами управляющих элементов, стоки МДИ-транзисторов ко.ммутирующих элементов подключены к истокам нагрузочных транзисторов триггера, затворы - к адресной шине, а истоки- к шине пулевого потенциала, отличающаяся тем, что, с целью повышения помехоустоичивости и быстродействия ячейки, она содержит дополнительные коммутирующие элементы, выполненные па МДИ-транзисторах одного типа проводимости с транзисторами коммзтирующих элементов, стоки которых подключены к стокам транзисторов коммутирующих элементов, истоки - к шине нулевого потенциала, а затворы - к второй и первой разрядной щине соответственно.

J3

W

| название | год | авторы | номер документа |

|---|---|---|---|

| Квазистатическая ячейка памяти | 1974 |

|

SU541197A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Ячейка памяти статического оперативного запоминающего устройства с радиоактивным источником питания | 2021 |

|

RU2777553C1 |

| Квазистатическая ячейка памяти | 1975 |

|

SU598119A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

Авторы

Даты

1976-12-30—Публикация

1974-08-22—Подача