Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминающих устройств.

Цель изобретения - повышение быстродействия и надежности устройства.

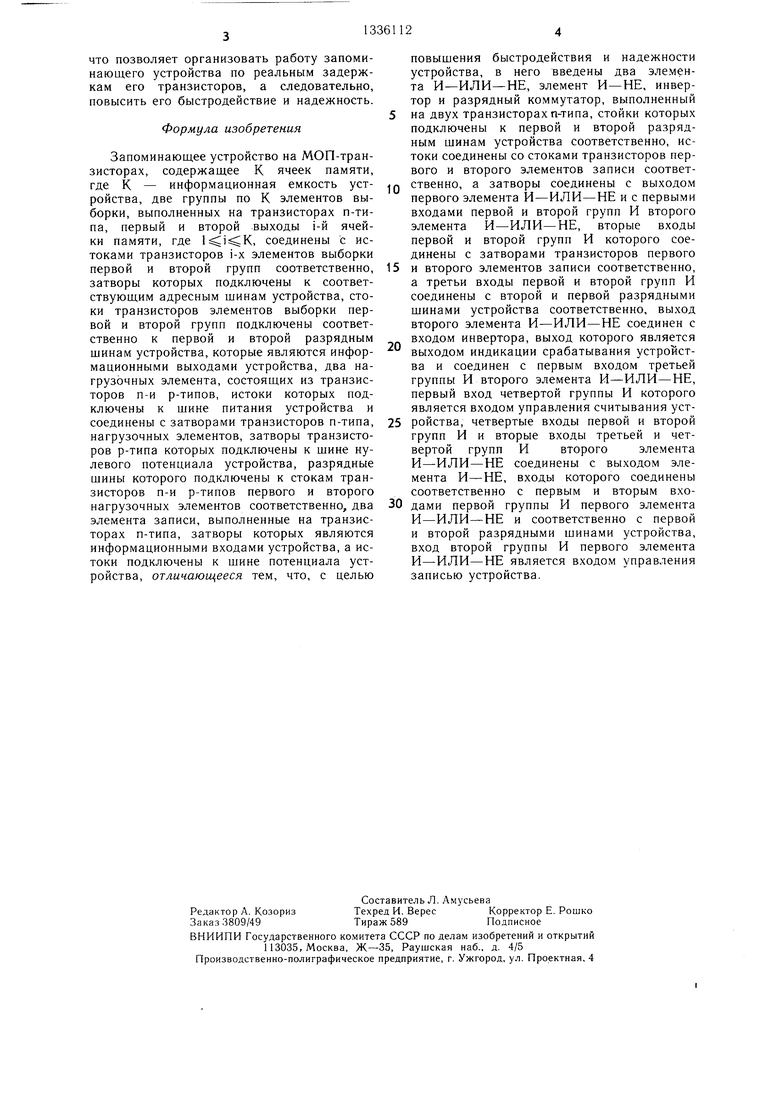

На чертеже приведена схема запоминающего устройства.

Устройство содержит ячейки 1 памяти, первую 2 и вторую 3 группы элементов выборки, нагрузочные элементы на транзисторах 4-7, элементы 8 и 9 записи. Кроме того, имеется разрядный коммутатор на транзисторах п-типа 10 и 11, элементы И-ИЛИ-НЕ 12 и 13, элемент И-НЕ 14 и инвертор 15.

Разрядные щины 16 и 17 являются информационными выходами устройства, а адресные шины 18 - входами выборки устройства. Затворы транзисторов 8 и 9 являются информационными входами 19 и 20 устройства. Выход инвертора 15 является выходом 21 индикации срабатывания устройства, первый вход третьей группы И второго элемента И-ИЛИ-НЕ 13 является входом управления считыванием устройства, а вход второй группы И первого элемента И-ИЛИ-НЕ 12 является входом управления записью устройства.

Запоминающее устройство работает следующим образом.

В режиме хранения на адресные шины 18 всех ячеек 1 подается низкий потенциал, закрывающий транзисторы 2 и 3, на вход 22 управления считыванием устройства также подается низкий потенциал. Кроме того, на вход 23 управления записью устройства подается высокий потенциал, в результате чего на выходе элемента 12 имеется низкий потенциал, закрывающий транзисторы 10 и 11. Таким образом, в режиме хранения на щина.х 16 и 17 устанавливается высокий потенциал, и в результате на выходе элемента 14 имеется низкий потенциал, на выходе элемента 13 - высокий потенциал, а на выходе инвертора 15 и выходе 21 устройства - низкий потенциал, что свидетельствует о завершении переходных процессов в этом режиме.

В режиме чтения информации из ячейки 1 на ее адресную шину 18 подается высокий потенциал, открывающий транзисторы 2 и 3, и низкий потенциал с первого или второго выхода этой ячейки 1 поступает на шину 16 или 17. Одновременно подается высокий потенциал на вход 22 устройства. После того, как на выходе элемента 14 появится высокий потенциал, на выходе элемента 13 появится низкий потенциал, а затем на выходе инвертора 15 и выходе 21 устройства появится высокий потенциал, что является признаком завершения переходных процессов в этом режиме.

В режиме записи информации в ячейку 1 на ее адресную шину 18, как и а предыдущем случае, подается высокий потенциал, открывающий транзисторы 2 и 3, и

низкий потенциал с первого или второго выхода этой ячейки 1 поступает на шину 16 или 17. Одновременно с этим на информационные входы 19 и 20 устройства выставляется записываемая информация, т. е. на один из них подается высокий

потенциал, а на другой - низкий потенциал, в результате чего открывается один из транзисторов 8 или 9. Кроме того, на выход 23 управления записью устройства подается низкий потенциал. Появление

5 низкого потенциала на шине 16 или 17 приводит к тому, что на выходе элементов 12 и 14 появляется высокий потенциал. Если информация, установленная на информационных входах 19 и 20 устройства, совпадает с ранее записанной

0 в ячейку 1, то изменения состояния последней не происходит, и после того, как на выходе элементов 12 и 14 появится высокий потенциал, на выходе элемента 13 появится низкий потенциал, а затем на вы5 ходе инвертора 15 и выходе 21 устройства - высокий потенциал, что является признаком завершения переходных процессов. Если же информация, установленная на информационных входах 19 и 20 устройства, противоположна ранее записанной

0 в ячейку 1, то происходит переключение последней. При этом, несмотря на высокий потенциал на выходе элементов 12 и 14, переключения элемента 13 не произойдет до тех пор, пока в ячейке 1 не установится требуемое состояние. В этом слу5

чае сначала на обеих шинах 16 и 17 поя5

вится низкий потенциал: на одной из-за того, что высокий потенциал на информационном входе 19 или 20 открывает транзистор 8 или 9, а на другой - из-за того, что через открытый транзистор 2

или 3 поступает низкий потенциал с первого или второго выхода ячейки 1. Затем, когда информация запишется в ячейку 1, на одной из шин 16 или 17 восстановится высокий потенциал. Только после этого на выходе элемента 13 появится низкий потенциал, а на выходе инвертора 15 и выходе 2 устройства - высокий потенциал.

В предлагаемом устройстве признаком завершения переходных процессов в режиме

0 записи или чтения является появление высокого потенциала на управляющем выходе устройства, в режиме хранения - появление на нем низкого потенциала. Этот сигнал появляется по окончании реальных переходных процессов при любых величинах

5 задержек транзисторов.

Таким образом, в предлагаемом устройстве индицируются моменты окончания переходных процессов во всех режимах.

что позволяет организовать работу запоминающего устройства по реальным задержкам его транзисторов, а следовательно, повысить его быстродействие и надежность.

Формула изобретения

Запоминающее устройство на МОП-транзисторах, содержащее К ячеек памяти, где К - информационная емкость устройства, две группы по К элементов выборки, выполненных на транзисторах п-ти- па, первый и второй выходы i-й ячейки памяти, где , соединены с истоками транзисторов i-x элементов выборки первой и второй групп соответственно, затворы которых подключены к соответствующим адресным шинам устройства, стоки транзисторов элементов выборки первой и второй групп подключены соответственно к первой и второй разрядным шинам устройства, которые являются информационными выходами устройства, два нагрузочных элемента, состоящих из транзисторов п-и р-типов, истоки которых подключены к шине питания устройства и соединены с затворами транзисторов п-типа, нагрузочных элементов, затворы транзисторов р-типа которых подключены к шине нулевого потенциала устройства, разрядные шины которого подключены к стокам транзисторов п-и р-типов первого и второго нагрузочных элементов соответственно, два элемента записи, выполненные на транзисторах п-типа, затворы которых являются информационными входами устройства, а истоки подключены к шине потенциала устройства, отличающееся тем, что, с целью

0

повышения быстродействия и надежности устройства, в него введены два элемента И-ИЛИ-НЕ, элемент И-НЕ. инвертор и разрядный коммутатор, выполненный на двух транзисторах п-типа, стойки которых подключены к первой и второй разрядным шинам устройства соответственно, истоки соединены со стоками транзисторов первого и второго элементов записи соответственно, а затворы соединены с выходом первого элемента И-ИЛИ-НЕ и с первыми входами первой и второй групп И второго элемента И-ИЛИ-НЕ, вторые входы первой и второй групп И которого соединены с затворами транзисторов первого

5 и второго элементов записи соответственно, а третьи входы первой и второй групп И соединены с второй и первой разрядными шинами устройства соответственно, выход второго элемента И-ИЛИ-НЕ соединен с входом инвертора, выход которого является выходом индикации срабатывания устройства и соединен с первым входом третьей группы И второго элемента И-ИЛИ-НЕ, первый вход четвертой группы И которого является входом управления считывания уст5 ройства, четвертые входы первой и второй групп И и вторые входы третьей и четвертой групп И второго элемента И-ИЛИ-НЕ соединены с выходом элемента И-НЕ, входы которого соединены соответственно с первым и вторым вхо0 дами первой группы И первого элемента И-ИЛИ-НЕ и соответственно с первой и второй разрядными шинами устройства, вход второй группы И первого элемента И-ИЛИ-НЕ является входом управления записью устройства.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1365129A1 |

| Запоминающее устройство типа "очереди | 1987 |

|

SU1532977A1 |

| Запоминающее устройство | 1987 |

|

SU1465911A1 |

| Запоминающее устройство на МОП-транзисторах | 1986 |

|

SU1411823A2 |

| Параллельный асинхронный регистр | 1988 |

|

SU1624530A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| ЯЧЕЙКА ПАМЯТИ | 1985 |

|

RU1318096C |

| Запоминающее устройство | 1987 |

|

SU1474738A1 |

| Магазинное запоминающее устройство | 1986 |

|

SU1472947A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения оперативных запоминаю- ш,их устройств. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается за счет введения в устройство разрядного коммутатора, выполненного на транзисторах 10 и 11, элементов И-ИЛИ-НЕ 12 и 13, элемента И-НЕ 14, инвертора 15 с соответствующими связями. Перечисленные элементы позволяют осуществлять индикацию моментов окончания переходных процессов в устройстве. В результате возможна асинхронная организация работы устройства. 1 ил. (Л со 00 О5

| Мурога С | |||

| Системное проектирование сверхбольших интегральных схем | |||

| - М.: Мир, 1985, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ изготовления зажимов конденсатора | 1919 |

|

SU3065A1 |

| Clare, c | |||

| Способ правки цилиндрических винтовых пружин | 1952 |

|

SU95051A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-07—Подача