(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1718215A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ДЕЛЕНИЯ ЧИСЕЛ | 1991 |

|

RU2010311C1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

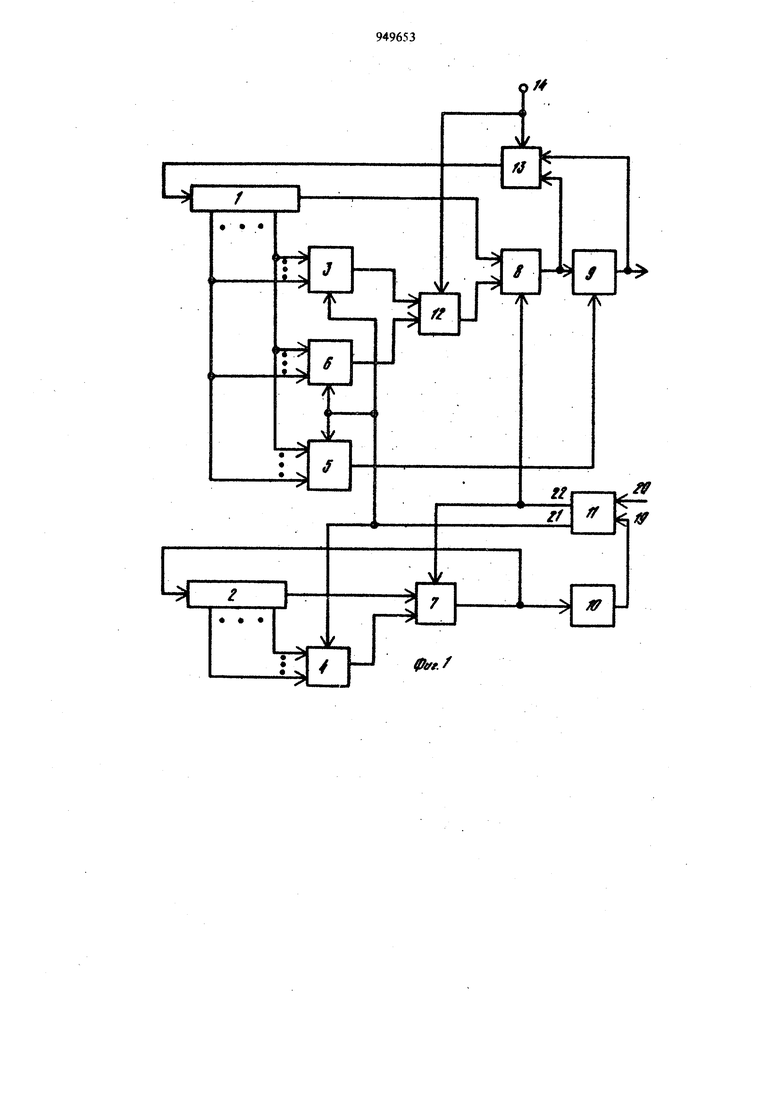

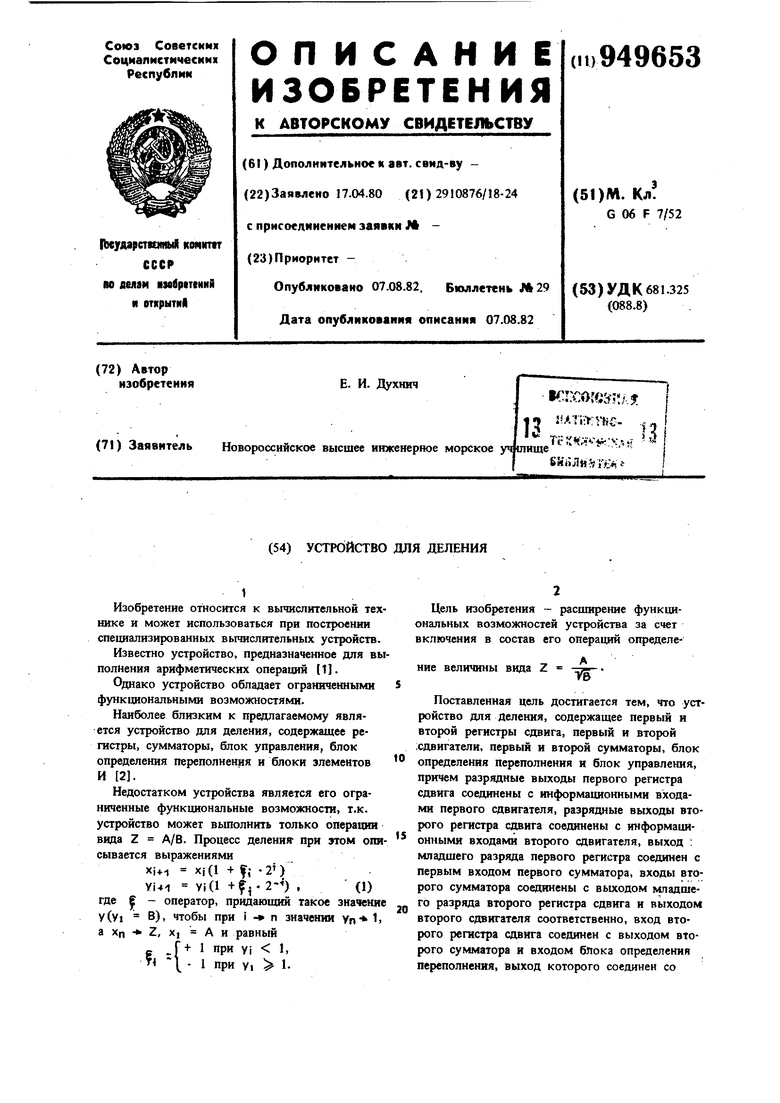

Изобретение относится к вычислительной тех нике и может использоваться при построении специализированных вычислительных устройств. Известно устройство, предназначенное для вы полнения арифметических операций (t. Однако устройство обладает ограниченны ш функциональными возможностями. Наиболее близким к предлагаемому является устройство для деления, содержащее регистры, сумматоры, блок управления, блок определения переполнения и блоки элементов И 2. Недостатком устройства является его ограниченные функциональные возможности, т.к. устройство может вьшолнить только операции вида Z А/В. Процесс деления при этом опи сывается выражениями xi(l + f; -2) Vi4i У|(1 +f. . 2--) ,(1) где - оператор, придающий такое значени У (У В), чтобы при i - п значении Vn . а Хп - Z, xi А и равный g .+ 1 при vj 1, - 1 при VI 1. Цель изобретения - расширение функциональных возможностей устройства за счет включения в состав его операций определение величины вида Z Поставленная цель достигается тем, что устройство для деления, содержащее первый и второй регистры сдвига, первый и второй :сдвигатели, первый и второй сумматоры, блок определения переполнения и блок управления, причем разрядные выходы первого регистра сдвига соединены с информационными входами первого сдвигателя, разрядные выходы второго регистра сдвига соединены с информационными входами второго сдвигателя, выход : младщего разряда первого регистра соединен с первым входом первого сумматора, входы второго сумматора соединены с выходом младпте го разряда второго регистра сдвига и вь1ходом второго сдвигателя соответственно, вход второго регистра сдвига соединен с выходом второго сумматора и входом бпока определения переполнения, выход которого соединен со 39 входом блока управления, первый выход кото рого соединен с управляющими входами первого и второго сумматоров, второй выход бло ка управления соед1шен с управляющими входами первого и второго сдвигателей, содержит третий и четвертый сдвигатели, первый и второй коммутаторы и третий сумматор, причем информационные входы третьего и четвертого сдвигателей соединены с разрядными выходами первого регистра сдвига, управляющие входы третьего и четвертого сдвигателей соединены .со вторым выходом блока управления, выходы первого и третьего сдвигателей соединен с информационными входами первого коммутатора, выход четвертого сдвигателя соединен с первым входом третьего сумматора, второй вход которого соединен с выходом первого сумматора, информационные входы второго коммутатора соединены с выходами первого и третьего сумматорюв, управляющие входы первого и второго коммутаторов соединены со входом признака операции устройств выход второго коммутатора соединен со входом первого регистра сдвига, выход первого коммутатора соединен со вторым входом пер вого сумматора, выход третьего сумматора соединен с выходом устройства. Блок управления содержит генератор тактовых импульсов, первый и второй счетчики, триггер, причем выход генератора тактовых импульсов соединен со входом первого счетчика, п-ый информационный выход последнего разряда которого соединен со счетным входом второго счетчика, информационные выходы разрядов которого соединены с первым выходом блока управления, единичный выход триггера соединен со вторым выходом блока управления, единичный вход триггера соединен с входом блока управления, а нулевые входы первого и второго счетчиков и первый нулевой вход триггера соединены t установочньГм входом блока управления, выход последнего разряда первого счетчика соединен со вторым нулевым входом триггер На фиг. 1 показана структурная схема уст ройства; на фиг. 2 - функциональная схема блока управления. Устройство содержит регистры 1 и 2 сдвига, первый второй, третий и четвертый сдвигатели 3-6, первый, второй и третий сумматоры 7-9. Блок 10 определения переполнения, блок 11 управления, первый и второй коммутаторы 12 и 13, управляю1шш вход 14 Блок 11 управления содержит генератор 15 тактовых импульсов, первый и второй счетчики 16 и 17, триггер 18, вход 19 и установочный вход 20, первый и второй выходы .21 и 22. Устройство работает следующим образом. Перед началом вычислений значения А и В хранятся в регистрах 1 и 2 соответственно. В случае выполнения операции Z по о сигналу, поступающему на вход 14, коммутатор 13 соединяет выход сумматора 8 со входом регистра 1, а коммутатор 12 соединяет вход сумматора 8 с выходом сдвигателя -3. При этом устройство работает по формулам О).д в случае выполнения операции Z у по сигналу, поступающему на вход 14, коммутатор 13 соединяет выход сумматора 9 со йходом регистра 1, а коммутатор 12 соединяет вход сумматора 8 с выходом сдвигателя 6. При этом делитель обрабатывается по формуле(f.( Тогда при значения . Хр- Z. С началом очередной итерации сдвигатели 4-6 соединяют соответствующие выходы регистров Г и 2 со входами сумматоров (вычислителей) 7-8 и сумматора 9 таким образом, что выхрдов,регистров поступают значения х|.2 xj-f ,yj 2. Значения xj и vj с выходов младщих разрядов регистров 1 и 2 поступают на вторые входы сумматоров (вычислителей), где в соответствии со значением оператора |. поступающим из блока управления И, суммируются (вычитаются) с xj и vj 2 соответственно. Результат с выхода сумматора (вычитателя) 8 поступает на сумматор 9 и складывается с величиной xj 2 Новые значения и yj4-t записываются в свои регистры, а величина поступает в блок 10 определения переполнения, в котором анализируется знаковый разряд (разряды) числа У|4-4. Сигнал о наличии или отсутствии переполнения поступает в блок 11 управления для выработки f,Процесс повторяется до вьшолнения заданного количества итераций. В конце операции результат Хп и Z может бьпь выведен из устройства. Блок И управления предназначен дп синхронизации работы отдельных блоков устройства для деления. На вход 20 блока управления поступает сигнал переполнения с выхода блока 10 определения переполнения. По первому sbixpду 21 блока вьщается параллельный двоичный код номера итерации для управления блоками элементов И устройства. По второму выходу 22 блока вьщается сигнал 6. для управления работой сумматоров-вычитателей. При вьздаче сигнала fj 1 сумматоры-вычитатели настраиваются на выполнение операции вычитания, а при f Р - сложения. Импульсы генератора подаются на вход первого счетчика по mod m, где m - число тактов одной итерации. С выхода счетчика 16 сигналы поступают на вход счетчика 17 итерации и нулевой вход триггера 18. Второй счетчик 17 осуществляет подсчет итераций по mod п, где п - число итераций при выполнении операции деления. Сигнал переполнения счетчика 16 выполняет сброс триггера. В единичное состояние триггер 18 устанавливается при наличии сигнала Переполнение. Перед началом работы счетчики 16 и 17 и триггер 18 устанавливаются в нулевое состоя ние сигналом Уст.О. В начале каждой итерации триггер 18 устанавливается в единичное со стояние при наличии сигнала Переполнение или остается в нулевом состоянии. После окон чания итерации сигнал переполнения счетчика 16 изменяет на единицу состояние счетчика итераций 17 и сбрасывает в ноль триггер 18. После окончания последней итерации счетчики 16 и 17 и триггер 18 оказываютсй в нулевом состоянии и работа блока заканчивается Эффективность устройства заключается в ра ширении функциональных возможностей при незначительном увеличении расхода оборудования. Формула изобретения 1. Устройство для деления, содержащее первый и второй регистры сдвига, первый и второй сдвигатели, первый и второй сумматоры, блок определения переполнения и блок управления, причем разрядные выходы первого регистра сдвига соединены с информационными входами первого сдвигателя, разрядные выходы второго регистра сдвига соединены с внформациоииыми входами второго сдвигателя, выход младшего разряда первого регистра соединен с первым входом первого сумматора, входы второго сумматора соединены с выходом младшего разряда второго регистра сдвига и выходом второго сдвигателя соответ ствеино, вход второго регистра сдвига соединен с выходом второго сумматора и входом блока определения переполнения, выход которого соединен со входом блока управления, первый выход которого соединен с упрайляю щнмя входами первого и второго сумматоров второй выход блока управления соединен С управляющими .входами первого и второго сдвигателей, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности получения частного от делимого и корня квадратного от делителя, оно содержит третий и четвертый сдвигатели, -первый и второй коммутаторы и третий сумматор, причем информационные входы третьего и четвертого сдвигателей сое-, динены с разрядными выходами первого регистра сдвига, управляющие входы третьего и четвертого сдвигателей соединены со вторым выходом блока управления, выходы первого и третьего сдвигателей соединены с информационными входами первого коммутатора, вь ход четвертого сдвигателя соединен с первым входом третьего сумматора, второй вход которого соединен с выходом первого сумматора, информационные входы второго коммутатора соединены с выходами первого и третьего сумматоров, управляющие входы первого и второго коммутаторов соединены со входом признака операции устройства, выход второго коммутатора соединен со входом первого регистра сдвига, выход первого коммутатора соединен со вторым входом первого комму татора, выход третьего сумматора соединен с выходом устройства. 2. Устройство по п. 1,отлн. с я тем, что блок управления содержит ге иератор тактовых импульсов, первый и второй счетчики, Т{яптер, причем выход генератора тактовых импульсов соединен со входом первого счетчика, п-ый 11Нфо{ шшонный выход которого соединен со счетньп входом второго счетчика и нулевым входом триггера, информационные выходы которого соединены с первым выходом блока управления, единичный выход триггера соединен со вторым выходом блока управления, единичный вход триггере соединен с входом блока управления, а нулевые входы пертого, второго счетчиков и тртггера соединены с установочным входом блока управления. Источники информации, принятые во внимание прт экспертизе 1.Авторское сввдетвльство СССР N 547765, кл. G 06 F 7/38, 1974. 2.Авторское «зидетельство СССР N 570054, кл. G 06 F 7/52, 1975 (прототип).

Авторы

Даты

1982-08-07—Публикация

1980-04-17—Подача