I

Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования кодов чисел.

Известен преобразователь параллельного двоичного кода в унитарный (число-импульсный) код, в котором серии импульсов, число которых соответствует весу двоичного разряда, подаются через соответствующую схему «И на выходную схему «ИЛИ, а в качестве удвоителя импульсов использован двоичный счетчик.

.Предложенное устройство отличается тем, что в нем выход схемы «И, соответствующей разряду с весом «1, соединен со входом дополнительной схемы «ИЛИ, со вторым входом которой соедиНен выход схемы сборки, соединенный со входом выходной схемы «ИЛИ, выход дополнительной схемы «ИЛИ, соединен со входом элемента задержки.

Это позволяет упростить схему устройства.

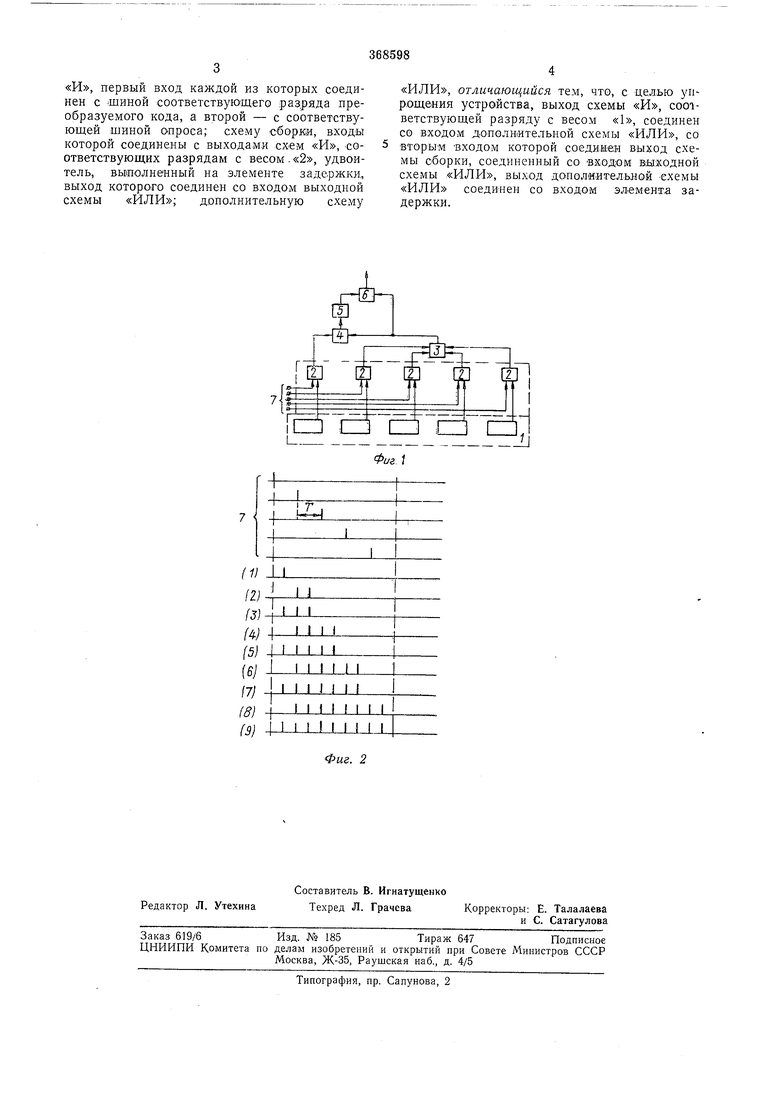

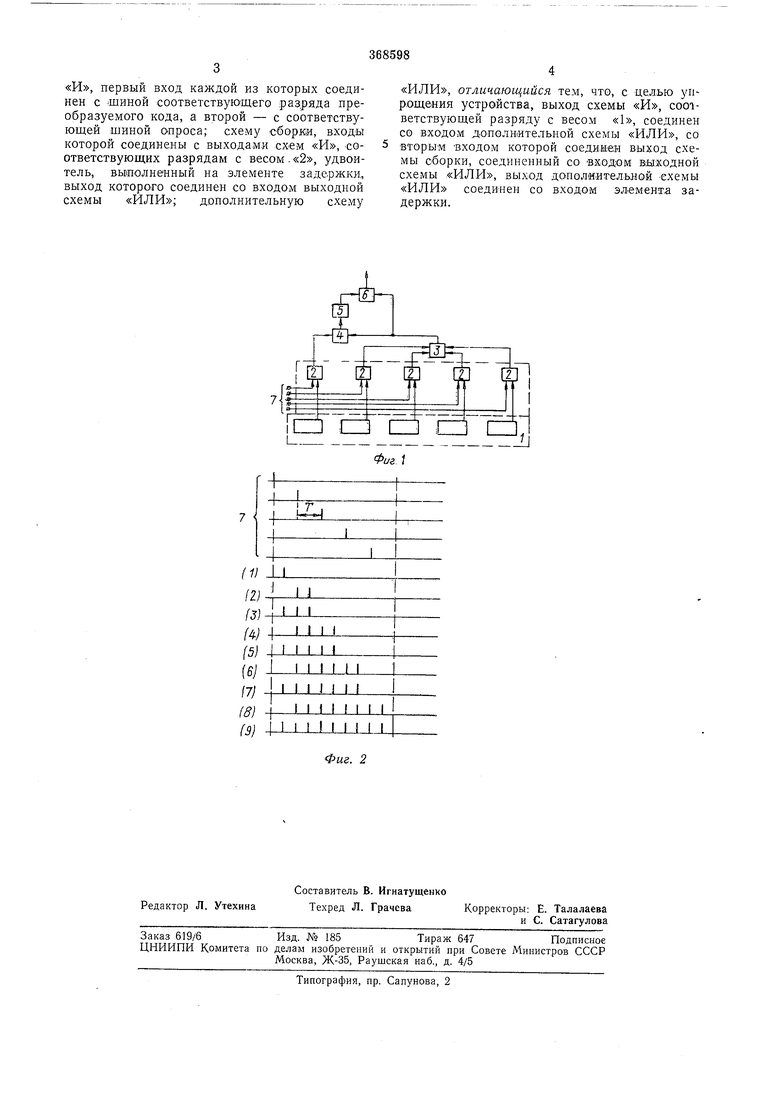

Схема устройства изображена на фиг. 1.

Устройство содержит регистр 1 для записи параллельного кода «12222, схемы «И 2, схему сборки 3, соединенную с теми схемами «И, которые соответствуют разрядам с весом «2, дополнительную схему «ИЛИ 4, элемент задержки 5, выходную cxeiviy «ИЛИ 6 и шины опроса 7.

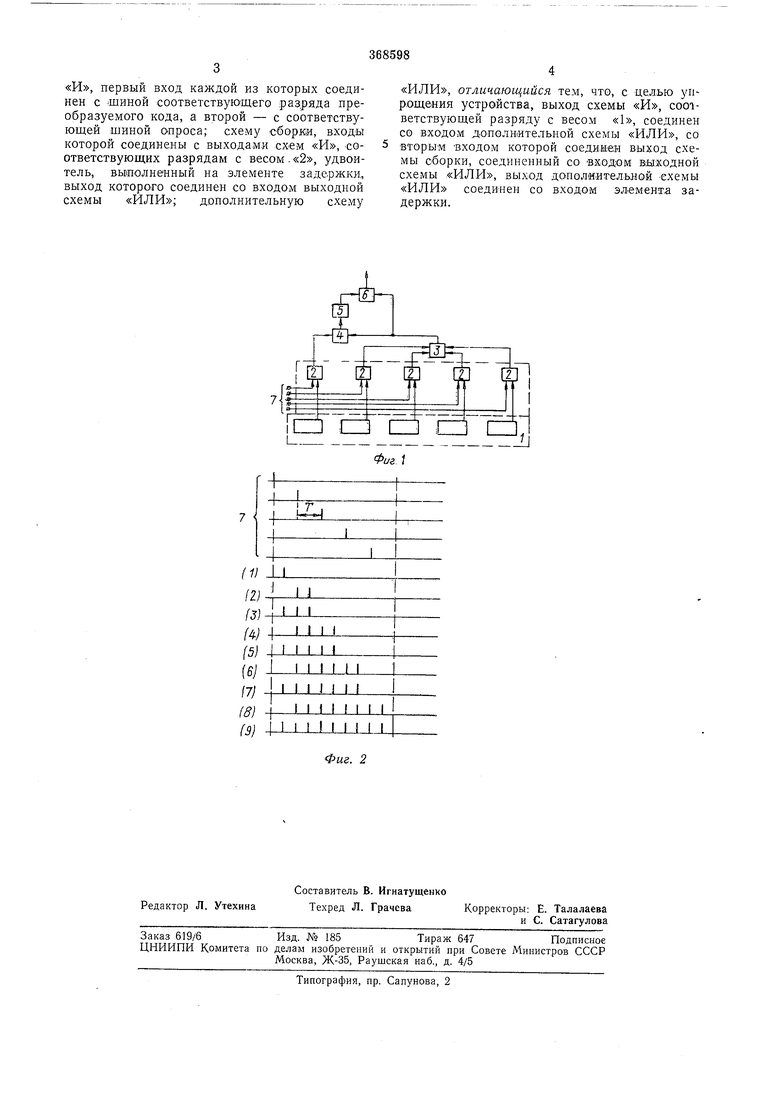

На фиг. 2 изображены временные диаграммы, иллюстрирующие распределение импульсов опроса, .подаваемых по шинам 7, в

цикле преобразования, а также выходные сигналы устройства при преобразовании десятичных чисел от «1 до «9, записанных двоично-десятичным кодом «12222 в регистре 1.

Устройство работает следующим образом.

Импульс опроса, поступающий на вход схемы «И 2, соединенной с выходо.м разряда с весом «I (крайний левый разряд регистра 1 на фиг. 1), проходит на выход устройства (выход схемы «ИЛИ 6) без удвоения (при состоянии «единица указанного разряда). Все остальные импульсы опроса, если открыты соответствующие схемы «И 2, удванваются, ибо поступают на выходную схему «ИЛИ 6 как непосредственно с выхода схемы сборки 5, так и через схему «ИЛИ 4 и элемент задержки 5.

Если величина сдвига между импульсами опроса, поступающими по щина.м 7, равна Г, то элемент 5 должен задерживать сигнал на время 0,5Г.

Выходной код выдается в виде пачки импульсов, причем в каждой пачке импульсы распределены равномерно, а положение пачки в пределах цнкла преобразования зависит от значения десятичного числа («Ь -;-«9).

Предмет изобретения

Преобразователь двончно-десятичного кода «12222 в унитарный код, содержащий схемы

«И, первый вход каждой из которых соединен с -шиной соответствующего разряда преобразуемого кода, а второй - с соответствующей шиной опроса; схему сборки, входы которой соединены с выходами сх-ем «И, соответствующих разрядам с весом.«2, удвоитель, выполненный на элементе задержки,, выход которого соединен со входом выходной схемы дополнительную схему

«ИЛИ, отличающийся тем, что, с целью упрощения устройства, выход схемы «И, соответствующей разряду с весом «1, соединен со входом дополнительной схемы «ИЛИ, со вторым -входом которой соедииен выход схемы сборки, соединенный со входом выходной схемы «ИЛИ, выход дополиигельной схемы «ИЛИ соединен со входом элемента задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода "12222" в унитарный код | 1975 |

|

SU549803A2 |

| Преобразователь двоично-десятичного кода 12222 в унитарный код | 1977 |

|

SU746497A1 |

| Преобразователь двоично-десятичного кода"12222" B пОСлЕдОВАТЕльНый КОд | 1979 |

|

SU840878A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU641441A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ | 1971 |

|

SU432486A1 |

| Преобразователь кодов | 1974 |

|

SU548857A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

iIZJ СП ZJ .rZJ

I

Фиг. 2

1

Фиг /

Авторы

Даты

1973-01-01—Публикация