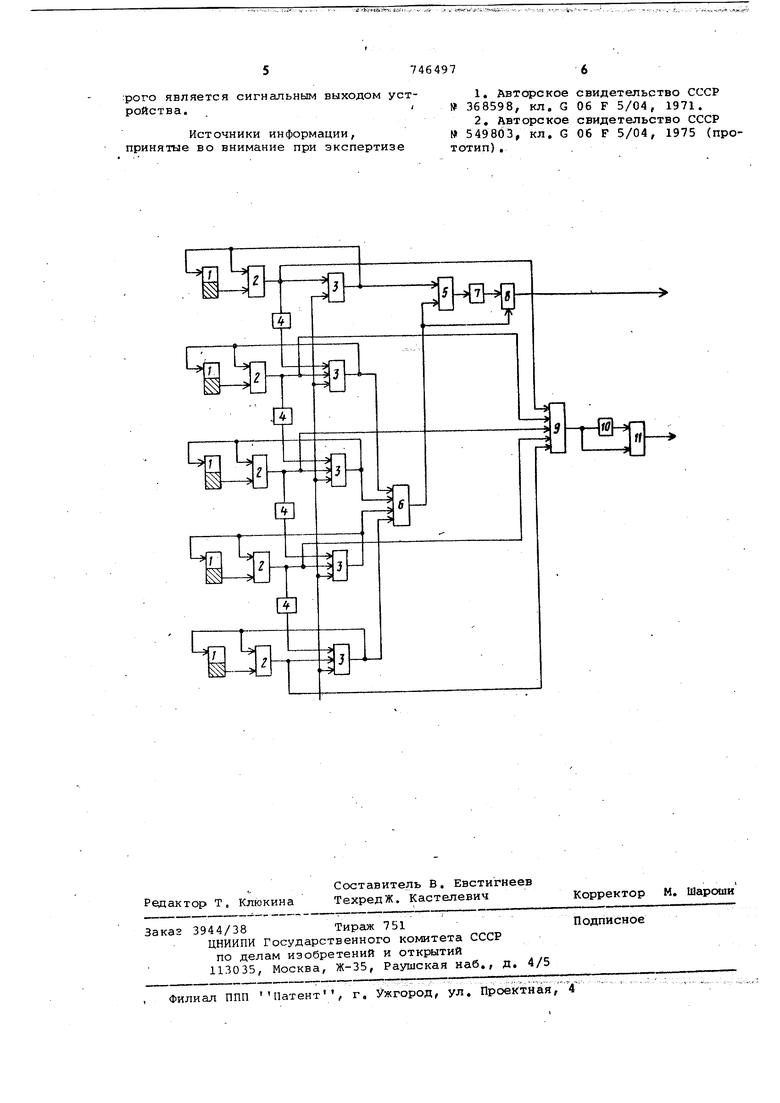

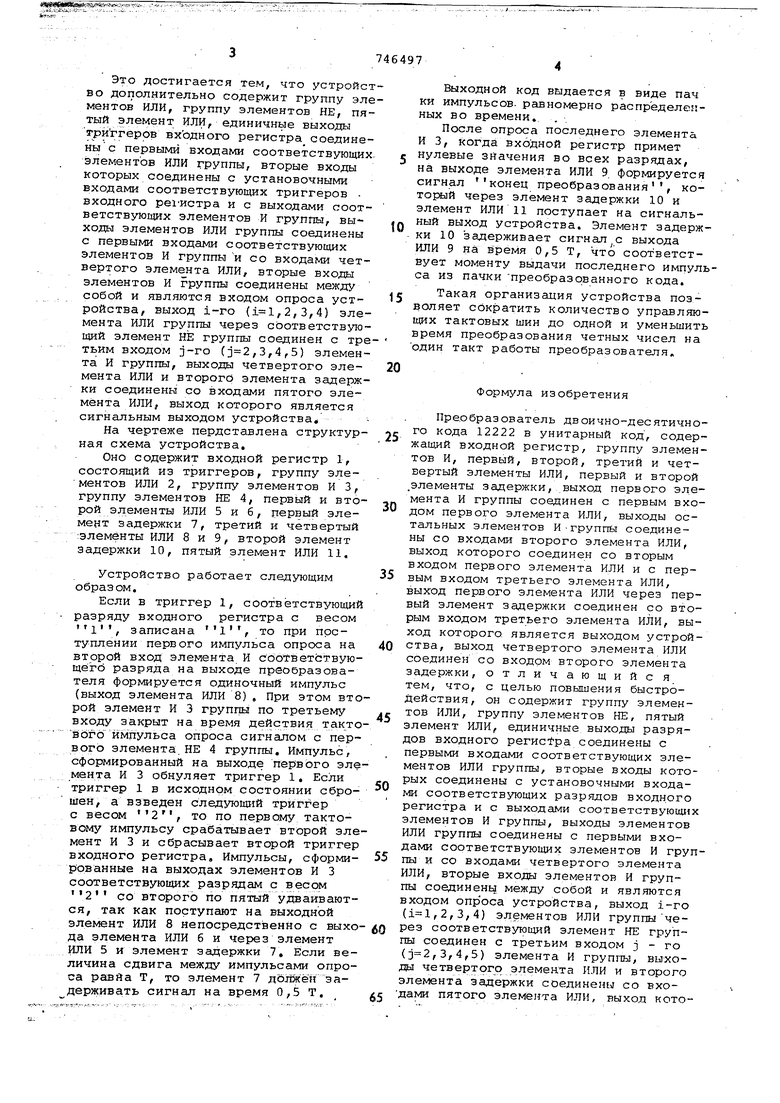

Изобретение относится к вычислительной технике и автоматике и предназначено для преобразования кодов чисел, Известен преобразователь параллельного двоично-десятичного кода в. унитарный (число-импульсный) код, со держащий регистр хранения кода, груп пу элементов И, элементы ИЛИ и элемент задержки И Недостатком известного устройства является невысокая скорость преобразования при укороченном формате двоично-десятичного кода 12222. Наиболее близким к изобретению техническим решением является преобразователь двоично-десятичного кода 12222 в унитарный, содержащий входной регистр, первую и вторую группу элементов И, первый, второй, третий и четвертый элементы ИЛИ, первую и вторую схемл задержки, единичные выходы триггеров входного регистра Сое динены с первыми входами соответствующих элементов И первой группы, вт рые входы которых являются входами устройства, выходы элементов И кроме последнего первой группы соединены с :первыми входами соответствующих элементов И второй группы, выход первого элемента И первой группы соединен с перви« входом первого элемента ИЛИ, выходм остальных элементов И первой группы соединены со входами второго . элемента ИЛИ,выход которого соединен со вторым входом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, выход первого элемента ИЛИ через первую схему задержки соединен со вторым входом третьего элемента ИЛИ, выход которого является выходом устройства, выходы элементов И второй группы соединены со входами четвертого элемента ИЛИ, выходом соединенного со входом втсчрой схемы задержки, выход которой является сигнальным выходетл устройства 2 В этом устройстве количество тактовых входов управления соответствует числу разрядов входного регистра, что увеличивает число внешних связей и усложняет управление j eo6pa30BaTeлем; преобразованиечетных чисел требует лишний такт, что снижает быстродействие устройства. Цель изобретения - повышение быстродействия. Это достигается тем, что устройс во дополнительно содержит группу эл ментов ИЛИ, группу элементов НЕ, пя тый элемент ИЛИ, единичные выходы триггеров входного регистра соедине ны с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с установочными входами соответствующих триггеров входного ре1истра и с выходс1ми соот ветствз щих элементов И группы, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И группы и со входами чет вертого элемента ИЛИ, вторые входы элементов И группы соединены между собой и являются входом опроса устройства, выход i-ro (,2,3,4) эле мента ИЛИ группы через соответствую щий элемент НЕ группы соединен с тр тьим входом j-ro (,3,4,5) элемен та И группы, выходы четвертого элемента ИЛИ и второго элемента задерж ки соединены со входами пятого элемента ИЛИ, выход которого является сигнальным выходом устройства На чертеже пердставлена структур ная схема устройства. Оно содержит входной регистр 1, состоящий из триггеров, группу элементов ИЛИ 2, группу элементов И 3, группу элементов НЕ 4, первый и вто рой элементы ИЛИ 5 и б, первый элемент задержки 7, третий и четвертый :элементы ИЛИ 8 и 9, второй элемент задержки 10, пятый элемент ИЛИ 11, Устройство работает следующим образом. Если в триггер 1, соответствующий разряду входного регистра с весом , записана Ч , то при поступлении первого импульса опроса на второй вход элемента. И соответствующего разряда на выходе преобразователя формируется одиночный импульс (выход элемента ИЛИ 8), При этом вто рой элемент И 3 группы по третьему входу закрыт на время действия такто вогоимпульса опроса сигналом с первого элемента НЕ 4 группы. Импульс, сформированный на выходе первого эле мента И 3 обнуляет триггер 1, Если триггер 1 в исходном состоянии сброшен, а взведен следующий триггер с весом 2, то по первому тактовому импульсу срабатывает второй эле мент И 3 и сбрасывает второй триггер входного регистра. Импульсы, сформированные на выходах элементов И 3 соответствующих разрядам с весом 2 со второго по пятый удваиваются, так как поступают на выходной элемент ИЛИ 8 непосредственно с выхо да элемента ИЛИ б и через элемент ИЛИ 5 и элемент задержки 7, Если величина сдвига между импульсами опроса равЯа Т, то элемент 7 должен задерживать сигнал на время 0,5 Т, Выходной код выдается в виде пач ки импульсов, равномерно распределенных во времени, . После опроса последнего элемента И 3, Когда входной регистр примет нулевые значения во всех разрядах, на выходе элемента ИЛИ 9. формируется сигнал конец преобразования , который через элемент задержки 10 и элемент ИЛИ 11 поступает на сигнальный выход устройства. Элемент задержки 10 задерживает сигнал с выхода ИЛИ 9 на 0,5 Т, что соответствует моменту выдачи последнего импульса из пачки преобразованного кода. Такая организация устройства позволяет сократить количество управляющих тактовых шин до одной и уменьшить время преобразования четных чисел на один такт работы преобразователя. Формула изобретения Преобразователь двоично-десятичного кода 12222 в унитарный код, содержащий входной регистр, группу элементов И, первый, второй, третий и четвертый элементы ИЛИ, первый и второй .элементы задержки, .выход первого эдемента И группы соединен с первым входом первого элемента ИЛИ, выходы остальных элементов И-группы соединены со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ, выход первого элемента ИЛИ через первый элемент задержки соединен со вторым входом третьего элемента ИЛИ, выход которого, является выходом устройства, выход четвертого элемента ИЛИ соединен со входом второго элемента 3адержки, отличающийс я тем, что, с целью повышения быстродействия, он содержит группу элементов ИЛИ, группу элементов НЕ, пятый элемент ИЛИ, единичные выходы разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с установочными входами соответствующих разрядов входного регистра и с выходами соответствующих элементов И группы, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И группы и со входами четвертого элемента ИЛИ, вторые входы элементов И группы соединены между собой и являются входом опроса устройства, выход i-ro (,2,3,4) элементо-в ИЛИ группычерез соответствующий элемент НЕ группы соединен с третьим входом j - го (,3,4,5) элемента И группы, выходы четвертого элемента ИЛИ и второго элемента задержки соединены со входами пятого элемента ИЛИ, выход кото;poro является сигнальным выходом устройства./

Источники информации, принятые во внимание при экспертизе

свидетельство СССР Об F 5/04 1971.

свидетельство СССР

06 F 5/04, 1975 (про

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода"12222" B пОСлЕдОВАТЕльНый КОд | 1979 |

|

SU840878A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1977 |

|

SU898417A2 |

| Преобразователь двоично-десятичного кода "12222" в унитарный код | 1975 |

|

SU549803A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА «12222» В УНИТАРНЫЙ КОД | 1973 |

|

SU368598A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

| Преобразователь двоичного кода в унитарный код | 1982 |

|

SU1049897A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

Авторы

Даты

1980-07-05—Публикация

1977-12-07—Подача