1

Изобретение относится к области вычислительной техники и предназначено для суммирования двоичных чисел.

Известен параллельный накапливающий сумматор, содержащий в каждом разряде счетный триггер регистра суммы, входные Элементы «И, вентили переноса и схему неравнозначности.

Предложенное устройство отличается тем, что единичный и нулевой выходы регистра переноса соединены через соответствующие элементы «И схемы передачи переноса с нулевым и единичным входами регистра полной суммы соответственно.

Это позволяет упростить устройство при его реализации на потенциальных элементах.

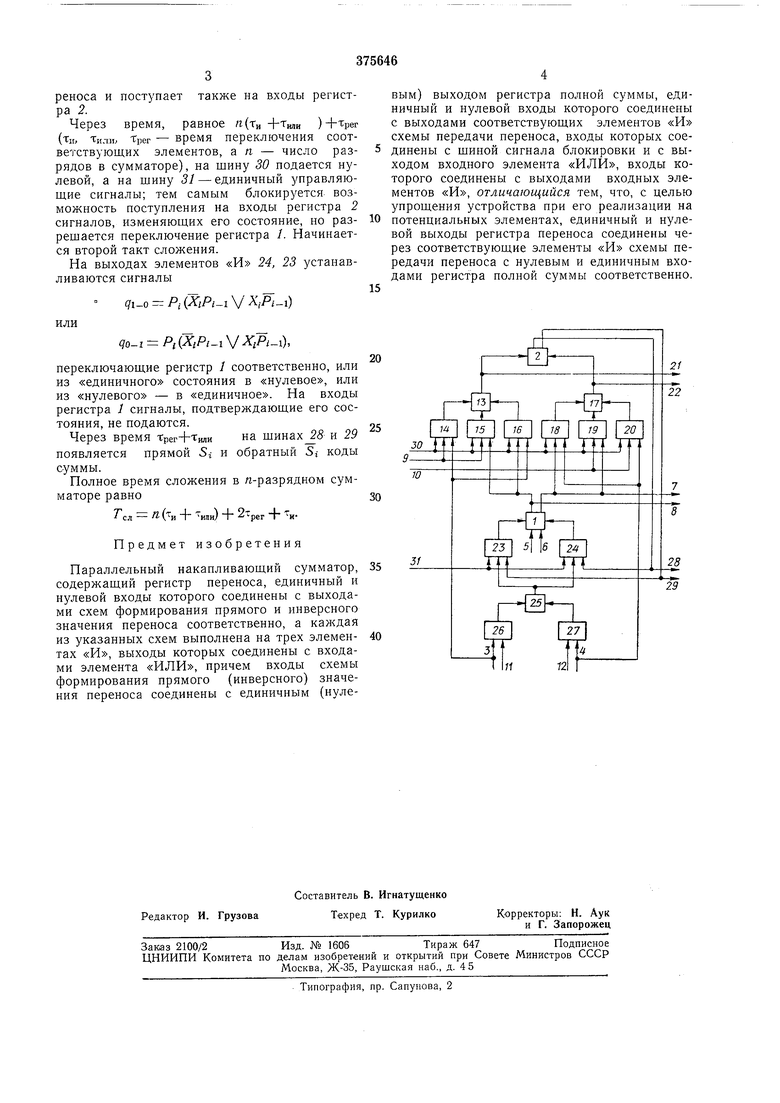

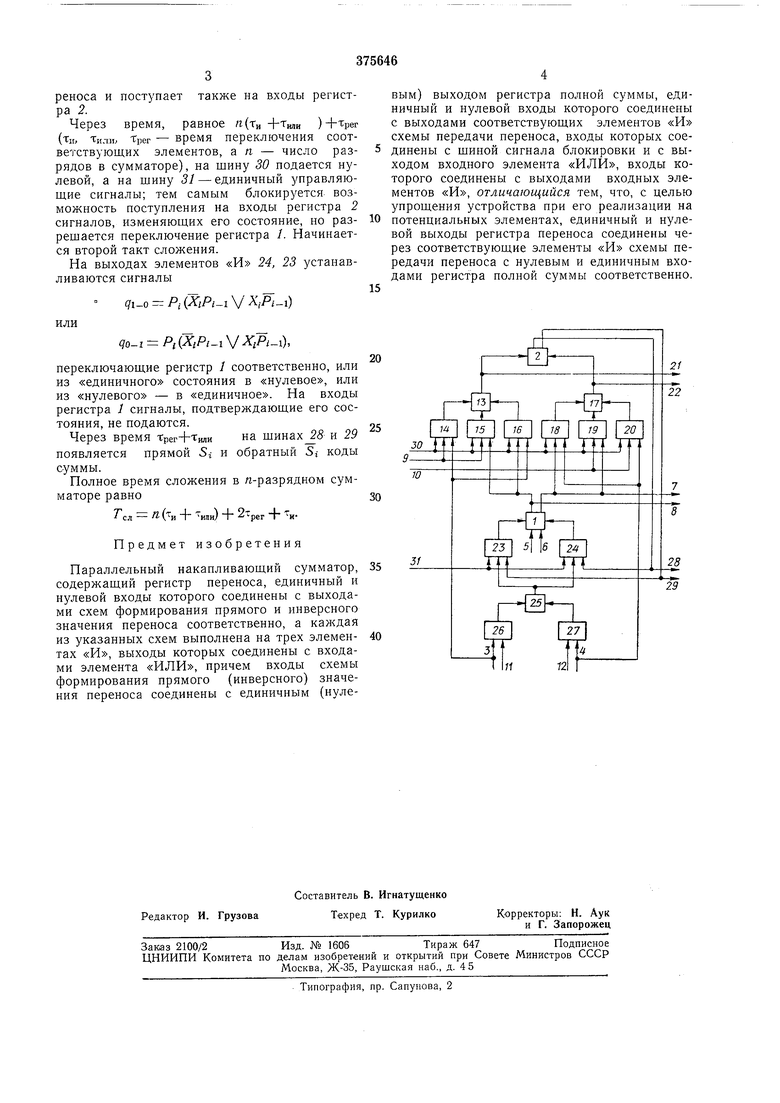

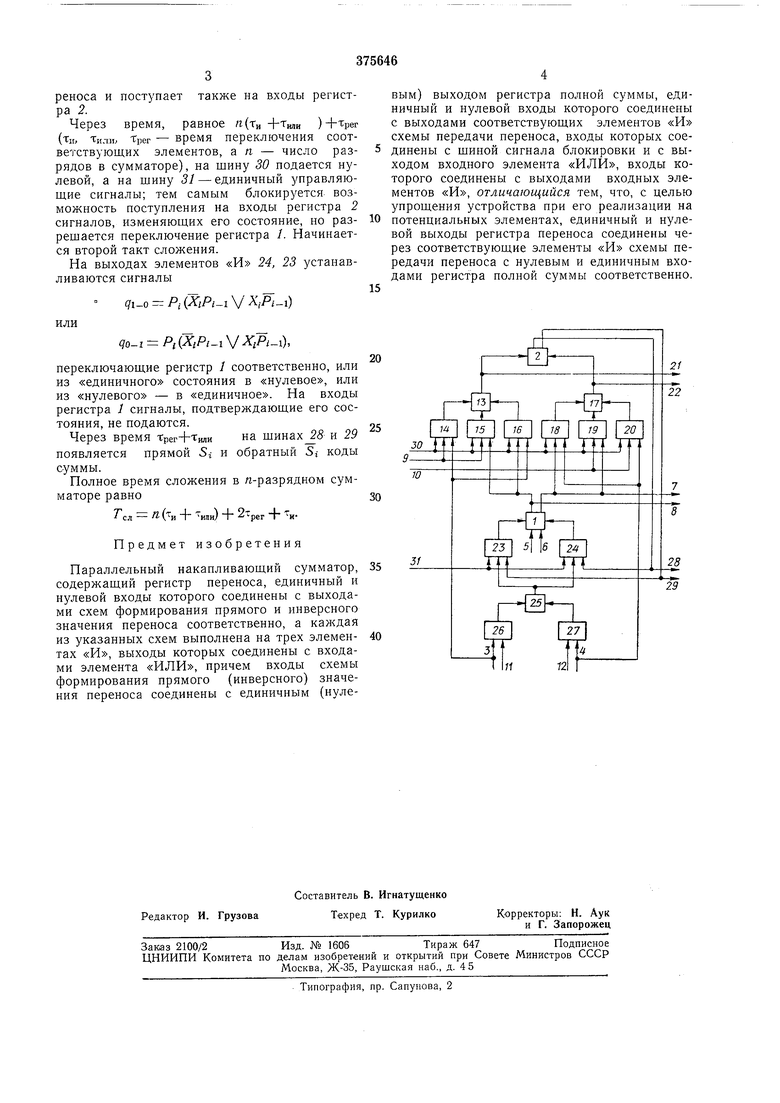

Блок-схема предложенного устройства показана на чертеже.

Устройство содержит регистр 1 полной сзммы, регистр 2 переноса шины 3 -я 4 подачи прямого (Xi) и обратного (Xi) кода первого слагаемого, щины 5 vi 6 подачи прямого (Уг) и обратного (У,) кода второго слагаемого, выходные щины 7 и S прямого (Si) и обратного (Si) кода суммы, входные щины 9 и 10 сквозного переноса из младщего, (i-1)-го разряда (Pi-i и соответственно), входные щины 11 и 12 подачи сигналов с выходов регистра переноса младщего (I-1)-го разряда.

схему формирования прямого значения переноса на элементах «ИЛИ 13 и «И 14-16, схему формирования инверсного значения пё рёноса на элементах «ИЛИ 17 и «И 18- 20, выходные щины 21 и 22 сквозного переноса в старЩий (/+1)-й разряд, элементы «И 23 и 24 схемы передачи переноса, входные элементы «ИЛИ 25 и «И 26 и 27, вьтходныё щины 28 и 29 регистра переноса, щины 30 и 31 сигналов блокировки.

Первое слагаемое подается в зстройство пО щинам 3 VI 4. Второе слагаемое либо уже записано в регистре / (т. е. является рез льТатом предыдущей операции), либо заносится в регистр по щинам 5 vi в.

Устройство работает следующим образом.

Первый такт работы начинается с подачи по щине 30 единичного сигнала блокировки, открывающего элементы «И 14-16 и 18- 20; на щине 31 в это время присутствует нулевой потенциал, запирающий элементы «И 23 и 24.

Иа выходах элементов «ИЛИ 13 и 17 формируются соответственно сигналы

PI X,YI V PI If, V IPi-i V yiPi-i,

- прямой и обратный коды переноса в старщий (г-|-1)й- разряд; перенос передается по

щинам 21 и 22 дальще по схеме сквозного переноса и поступает также па входы регистра 2.

Через время, равное «(Ти +TMH )+т;рег (tir, tjian. Трег - врбмя переключения соответствующих элементов, а я - число разрядов в сумматоре), на шину 30 подается нулевой, а на шину 31 - единичный управляюш,ие сигналы; тем самым блокируется, возможность поступления на входы регистра 2 сигналов, изменяющих его состояние, но разрешается переключение регистра /. Начинается второй такт сложения.

На выходах элементов «И 24, 23 устанавливаются сигналы

(,)

или Pi(XiP,-i JXfi-,},

переключающие регистр 1 соответственно, или из «единичного состояния в «нулевое, или из «нулевого - в «единичное. На входы регистра / сигналы, подтверждающие его состояния, не подаются.

Через время Трег+Тили на шинах 25 и 29 появляется прямой Si и обратный 5, коды суммы.

Полное время сложения в п-разрядном сумматоре равно

сл fl( гаи) + З-рег + иПредмет изобретения

Параллельный накапливающий сумматор, содержащий регистр переноса, единичный и нулевой входы которого соединены с выходами схем формирования прямого и инверсного значения переноса соответственно, а каждая из указанных схем выполнена на трех элементах «И, выходы которых соединены с входами элемента «ИЛИ, причем входы схемы формирования прямого (инверсного) значения переноса соединены с единичным (нулевым) выходом регистра полной суммы, единичный и нулевой входы которого соединены с выходами соответствующих элементов «И схемы передачи переноса, входы которых соединены с шиной сигнала блокировки и с выходом входного элемента «ИЛИ, входы которого соединены с выходами входных элементов «И, отличающийся тем, что, с целью упрощения устройства при его реализации на

потенциальных элементах, единичный и нулевой выходы регистра переноса соединены через соответствующие элементы «И схемы передачи переноса с нулевым и единичным входами регистра полной суммы соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ ДЛЯ МНОГОКАНАЛЬНЫХ АНАЛИЗАТОРОВ | 1973 |

|

SU377792A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1971 |

|

SU314746A1 |

| Накапливающий сумматор | 1976 |

|

SU634276A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| УСТРОЙСТВО для ПЕРЕНОСА | 1971 |

|

SU296107A1 |

| Устройство для суммирования чисел | 1984 |

|

SU1183959A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Сумматор | 1974 |

|

SU563675A1 |

| Устройство для сложения чисел | 1976 |

|

SU634274A1 |

Авторы

Даты

1973-01-01—Публикация