Изобретение относится к области вычислительной техники.

Известен сумматор с управляемыми элементами иамяти (регистрами), способами на время .получения промежуточных результатов и суммы образовывать элементы кодово-позиционной схемы сум.матора, а sareiM снова переключается в элементы памяти для фиксации промежуточных результатов и суммы.

Однако известное устройство сложно.

С целью со1К|ращения оборудования, в предложенном сумматоре единичный выход регис11ра переноса соединен со входами первой и второй схем «И, другие входы которых соединены соответственно с плиной инверсного .кода слагаемого и шиной инверсного кода переноса, выходы этих схем через схему соединены с нулевым входом регистра суммы, пулевой выход регистра переноса соединен со входами третьей и четвертой схем «И, другие входы которых соединены соответственно с шиной прямого кода слагаемого и прямого кода переноса, выходы схем «И через схему «ИЛИ соединены с единичным входом регистра суммы.

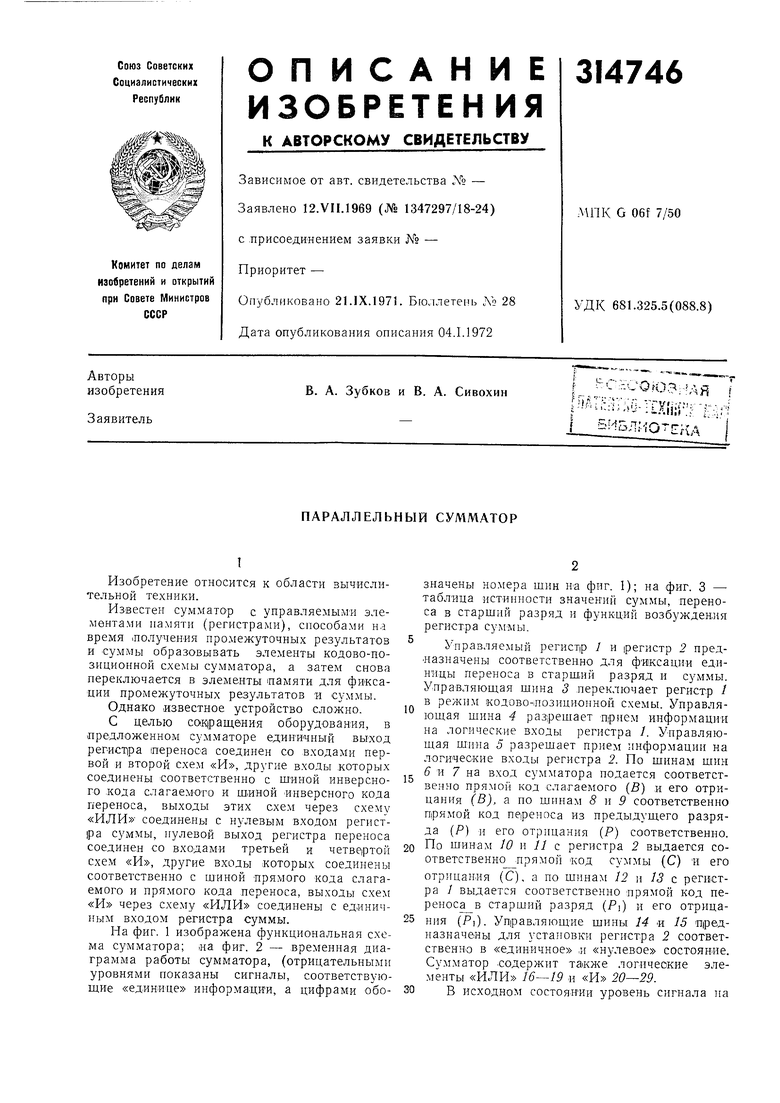

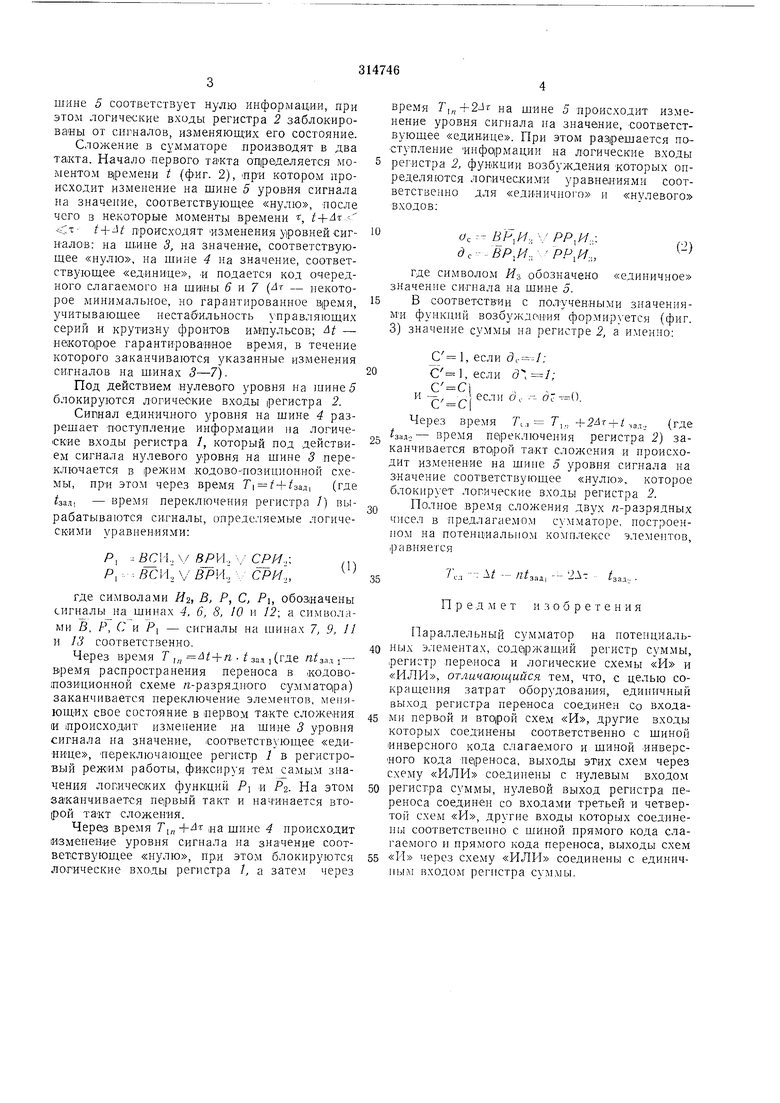

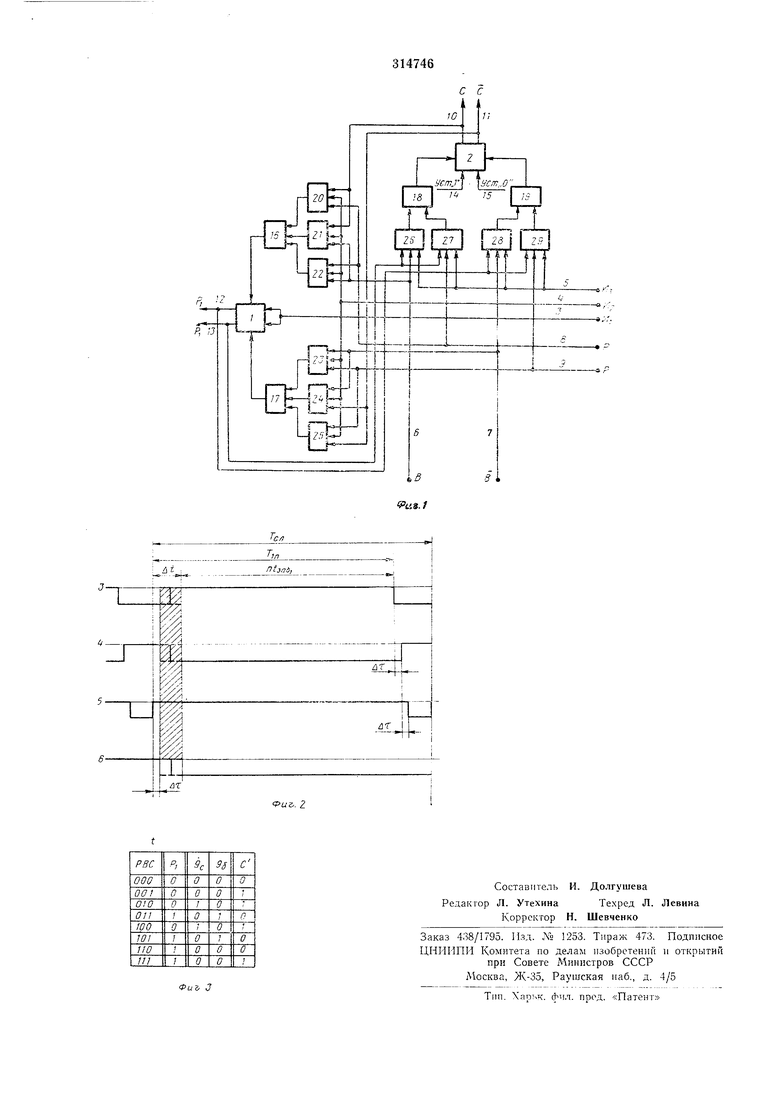

На фиг. 1 изображена функциональная схема сумматора; «а фиг. 2 - временная диаграмма работы сумматора, (отрицательными уровнями показаны сигналы, соответствующие «единице информации, а цифрами обозначены номера шин на фиг. 1); на фиг. 3 - таблица истипностп значений суммы, цереноса Б старший разряд и функций возбуждения регистра суммы.

Управляемый регистр J и регистр 2 предназначены соответственно для фиксации единицы переноса в старший разряд и суммы. Управляющая шина 3 переключает регистр / в режим кодово-позициопной схемы. Управляющая шина 4 разрешает прием информации на логические входы регистра /. Управляющая шина 5 разрешает прием информации на логические входы регистра 2. По шинам шин 6 и 7 на вход сумматора подается соответственно прямой код слагаемого (В) и его отрицания (В), а по шинам S и 5 соответственно прямой код переноса из предыдущего разряда (Я) и его отрицания (Р) соответственно. По шинам 10 и // с регистра 2 выдается соответственно прямой код суммы (С) И его

отрицания (С), а по шинам 12 и 13 с регистра / выдается соответственно прямой код переноса в старший разряд (Pj) и его отрицания (Р). Управляющие шины 14 п 15 предназначены для устагговки регистра 2 соответственно в «единичное и «нулевое состояние. Сумматор содержит также логические элементы «ИЛИ и «И 20-29.

шине 5 соответствует нулю информации, при этом логические входы регистра 2 заблокироваеы от сигналов, изменяющих его состояние.

Сложение в сумматоре тфоиз-водят в два такта. Начало первого такта определяется моментом времени t (фиг. 2), -при котором происходит изменение на шине 5 уровня сигнала на значение, соответствуюш,ее «нулю, после чего в некоторые моменты времени t, т- происходят изменения уровней сигналов: на ш.ине 3, на значение, соответствуюшее «нулю, на шине 4 на значение, соответствуюш,ее «единице, ц подается код очередного слагаемого на шены 6 и 7 - некоторое минимальное, но гарантированное время, учитывающее нестабильность управляющих серий и крутизну фронтов имцульсов; - некоторое гарантироваганое время, в течение которого заканчиваются указанные изменения сигналов на 3-7).

Под действием нулевого уровня на шине 5 блокируются логические входы регистра 2.

Силнал единичного уровня на шине 4 разрешает поступление информации на логические входы регистра /, который под действием сигнала нулевого уровня на шипе 3 переключается в режим кодово-тюзинионной схемы, при этом через время Г| г + /зад| (где , - время переключения регистра /) вырабатываются сигналы, определяемые логическими уравнениями:

/о, .5СМ.Л/ 8РИ„ V СРЯ.,; Я,., //9ЯИ., СРИ.„

где символами И2, В, Р, С, Р, обозначены сигналы на шинах 4, 6, 8, 10 и 12; а символами В. Р, С и PI - сигналы на 1пинах 7, 9, 11 и 13 соответственно.

Через время Т ,„ t+n t зад (где л/зад гвремя распространения переноса в «одово1ПОЗИЦИОННОЙ схеме п-разрядного сумматора) заканчивается переключение элементов, меняющих свое состояние в первом такте сложения 1И происходит изменение на шине 3 уровня сигнала на значение, соответствующее «единице, Переключающее регистр 1 в регистровый реж1им работы, фиксируя тем самым значения логических функций Р и PZ. На этом заканчивается первый такт и начинается второй такт сложения.

Через время -f 4т да щине 4 происходит изменение уровня сигнала на знячение соответствующее «нулю, при этом блокируются логические входы регистра /, а затем через

вреМЯ Г,„+2-5г на шине 5 происходит изменение уровня сигнала на значение, соответствующее «един-ице. При этом разрещается потупление информации на логические входы регистра 2, функции возбуждения которых онределяются логическимИ уравнениями соответственно для «едиаично1-о и «нулевого входов:

,H.,j РР,И,:,„,

д,-ВР,И,, РР,И.,,

где символом Яз обозначено «единичное значение сигнала на шине 5.

В соответствии с полученными значениями функпий возбужде1ИИЯ формир}-ется (фиг. 3) значение суммы на регистре 2, а именно:

С 1, если , если

С , . „

и ,р если а с --- .

Через время Tt., 7,., -f 24г + /,3,., (где зад., - время переключения регистра 2) заканчивается второй та.кт сложения и происходит изменение па шипе 5 уровня сигнала на значение соответствурощее «нулю, которое блокирует логические входы регистра 2. Полное .время сложения двух п-разрядных чисел в нредлагаемом сумматоре, построенном на потенциальном комплексе элементов, (равняется

7„ -: А/ - /г/зая: - , .

пред м е т изобретения

Параллельный сумматор на нотепциаль40 ных элементах, соде|ржащий регистр суммы, регистр переноса и логические схемы «И и «ИЛИ, отличающийся тем, что, с целью сокращения затрат оборултования, единичный выход регистра переноса соединен со входами первой и второй схем «И, другие входы которых соединены соответственно с щиной инверсного кода слагаемого и щиной инверсного кода переноса, выходы этих схе.м через схему «ИЛИ соединены с нулевым входом

50 регистра суммы, нулевой выход регистра переноса соединен со входами третьей и четвертой схем «И, другие входы которых соедииены соответственно с шиной прямого кода слагаемого и прямого кода переноса, выходы схем

55 «И через схему «ИЛИ соединены с единич11Ы.М входом регистра суммы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1968 |

|

SU220634A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1973 |

|

SU375646A1 |

| Цифровой интерполяционный фильтр | 1990 |

|

SU1728962A1 |

| Устройство для суммирования последовательных кодов | 1984 |

|

SU1254472A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| Устройство вычисления функции @ @ с исправлением ошибок | 1984 |

|

SU1288690A1 |

| ДВОИЧНЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 1973 |

|

SU378844A1 |

Даты

1971-01-01—Публикация