1

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах (ЗУ) цифровых вычислительных машин.

Известны постоянные ЗУ с записью информации геометрическими кодами, содержащие дещифратор адреса, щифраторы, запомипаюпше элементы и элементы связи.

Однако такие ЗУ содержат большое число запоминающих элементов, элементов связи как в числовом блоке, так и в шифраторе (декодере). В этих устройствах для записи каждой кодовой комбинации используется свой запоминающий элемент, число входов шифратора равно числу запоминающих элементов в числоном блоке, а чем больше входов имеет шифратор, тем больше элементов связи в шифраторе необходимо для записи всех возможных кодовых комбинаций.

Целью изобретения является повышение надежности устройства и увеличение объема информации.

Эта цель достигается тем, что предложенное ЗУ содержит сумматор по модулю два, к первым входам которого подключены выходы шифратора, а ко вторым - выход управляющего элемента.

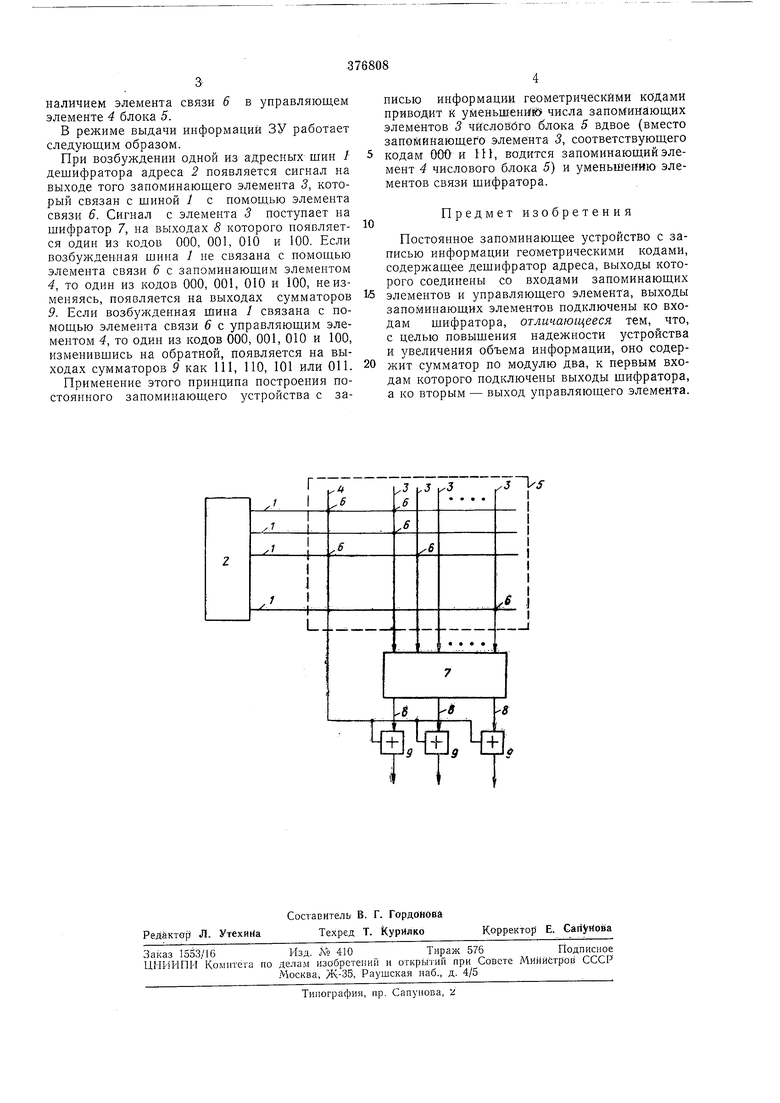

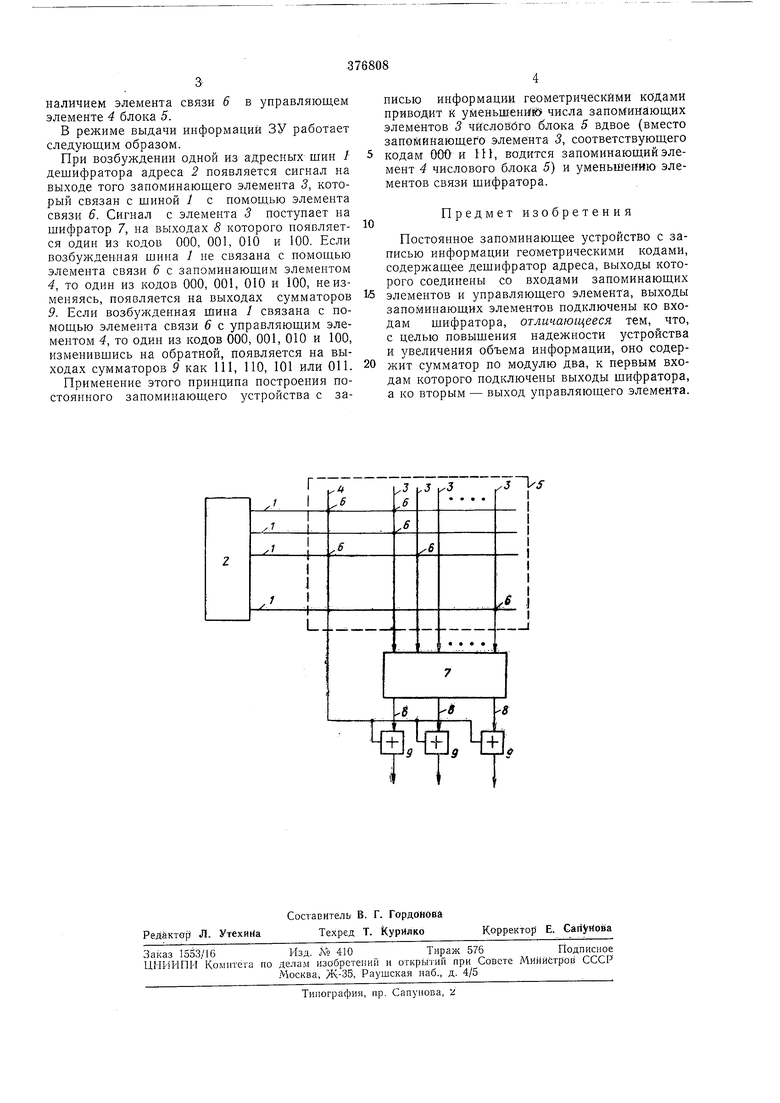

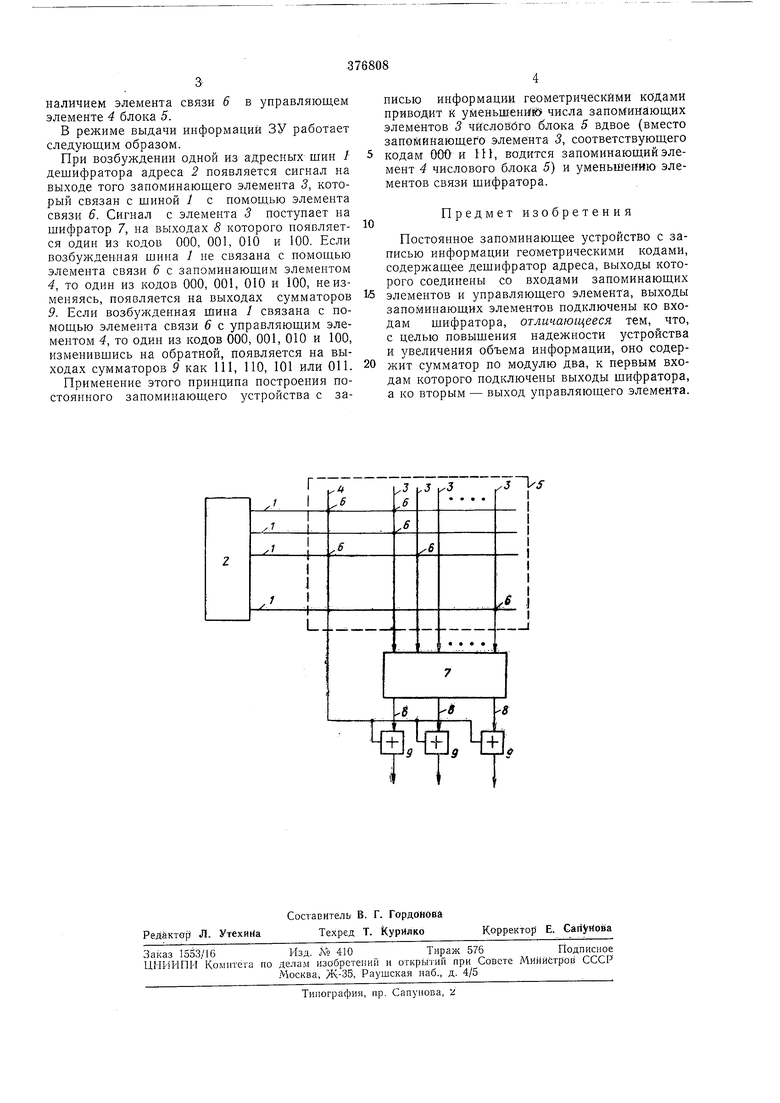

На чертеже изображена блок-схема предложенного ЗУ.

Адресные шины / дешифратора адреса 2 соединены с запоминающими элементами 3 и управляющего элемента 4 числового блока 5 с помощью элементов связи 6. Запоминающие элементы 3 подключены к шифратору 7. Выходы 8 шифратора 7 подключены к сумматорам по модулю два 9, к которым также подключен элемент 4, управляющий записью и выдачей информации в прямом и обратном

коде.

ЗУ работает следующим образом. Пусть, например, запись информации производится геометрическими кодами, соответствующими трехразрядному разбиению исходного двоичного кода. При рассмотрении всех возможных трехразрядных кодовых комбинаций оказывается, что кодовые комбинации 100, 101, ПО и 111 можно рассматривать соответственно как комбинации 011, 010, 001 и 000,

записанные в обратном коде. Отсюда следует, что одна из кодовых комбинаций Oil, 010, 001 и 000 записывается с помощью одного элемента связи 6 в соответствующий ей запоминающий элемент 3 с указанием вида кода (прямого) отсутствием элемента связи 6 в управляющем элементе 4 блока 5. Кодовые комбинации 100, 101, ПО и 111 записываются в те же три запоминающих элемента (для комбинаций 000 и 111 запоминающий элемент 3 не

нужен) с указанием вида кода (обратного)

наличием элемента связи 6 в управляющем элементе 4 блока 5.

В режиме выдачи информации ЗУ работает следующим образом.

При возбуждении одной из адресных щин / дешифратора адреса 2 появляется сигнал на выходе того запоминающего элемента 3, который связан с шиной 1 с помощью элемента связи 6. Сигнал с элемента 3 поступает на шифратор 7, на выходах 8 которого появляется один из кодов 000, 001, 010 и 100. Если возбужденная шина 1 не связана с помощью элемента связи 6 с запоминающим элементом 4, то один из кодов 000, 001, 010 и 100, не изменяясь, появляется на выходах сумматоров 9. Если возбужденная шина / связана с помощью элемента связи 6 с управляющим элементом 4, то один из кодов 000, 001, 010 и 100, изменивщись на обратной, появляется на выходах сумматоров 9 как 111, ПО, 101 или 011.

Применение этого принципа построения постоянного запоминающего устройства с записью информации геометрическими кодами приводит к уменъШенйй числа запоминающих элементов 3 чйслойбго блока 5 вдвое (вместо запоминающего элемента 3, соответствующего кодам 000 и 1Н, водится запоминающий элемент 4 числового блока 5) и уменьшению элементов связи шифратора.

Предмет изобретения

Постоянное запоминающее устройство с записью информации геометрическими кодами, содержащее дешифратор адреса, выходы которого соединены со входами запоминающих элементов и управляющего элемента, выходы запоминающих элементов подключены ко входам шифратора, отличающееся тем, что, с целью повышения надежности устройства и увеличения объема информации, оно содержит сумматор по модулю два, к первым входам которого подключены выходы шифратора, а ко вторым - выход управляющего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Устройство управления сортировкой изделий | 1986 |

|

SU1388111A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сдвига информации | 1983 |

|

SU1188783A2 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU604033A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Запоминающее устройство с коррекцией модульных ошибок | 1989 |

|

SU1633461A1 |

Т Т т

Авторы

Даты

1973-01-01—Публикация