1

Изобретение относится к вычислительной технике и может быть использовано при построении надежных ЦВМ, функционирующих в системе вычетов.

Известны устройства для определения адреса поправки корректора, функционирующего в системе вычетов, содержащее преобразователь из системы вычетов в позиционную систему со сменным набором оснований (ПСС), узел сверки и схему сравнения. Шины информационных вычетов корректирующего кода подключены к входам преобразователя, выходы которого связаны с входами схемы свертки. Выходы схемы свертки подключены к суммирующим входам схемы сравнения, на вычитающие входы которой поданы щины контрольных вычетов корректирующего кода. Выход схемы сравнения является выходом устройства определения адреса поправки.

В известном устройстве вводится информационная избыточность, характеризуемая соотнощением:

P йf J 2Pn-lP„,(1)

гдеPk - произведение всех контрольных модулей;

Phj - значение /-го контрольного модуля;

q - количество контрольных модулей;

Рп-1-Рп - произведение двух наибольщих информационных модулей.

Такая избыточность позволяет по результату, получаемому на выходе схемы сравнения, однозначно определить адрес поправки. Однако это приводит к больщим затратам избыточного оборудования, вводимого в целях коррекции.

Попытка уменьшить информационную избыточность корректирующего кода и соответствующую избыточность оборудования ЦВМ, предназначенного для хранения и обработки контрольных вычетов, приводит к появлению ошибок, оказывающихся неразличимыми по результату, получаемому на выходе схемы сравнения.

Можно показать, что при уменьшении избыточности вплоть до выполнения требования

Р,Рп-гР„(2)

каждому вектору коррекции соответствует не более двух (ЛЛ,, ДЛг) ошибок. Причем, если , то при выполнении для искаженного числа А соотношения ( имеет место ошибка ДЛ;. В противном случае ошибка равна ДЛj.

Корректирующие возможности, таким образом, могут быть сохранены за счет введения дополнительного анализа соответствующих значений возможной ощибки и искаженного числа.

Предлагаемое устройство реализует эту идею и отличается тем, что содержит постоянное запоминающее устройство ощибок и вторую схему сравнения, входы которой соединены соответственно с выходами преобразователя информационной части числа и постоянного запоминающего устройства ощибок, вход которого соединен с выходом первой схемы сравнения.

За счет введения достаточно простых дополнительных цепей в устройстве коррекции обеспечивается уменьщение объема оборудования в запоминающем и операционном устройствах вычислительной мащины, а также в узлах свертки и сравнения самого корректирующего устройства. Так, например, при переходе от (1) к (2) за счет уменьщения одного из контрольных модулей в два раза объем оборудования оперативного запоминающего и операционного устройств, оперирующих с двоично-кодированными вычетами, уменьщается на один двоичный разряд, а число конъюктивных элементов в узлах, построенных на квадратных матричных схемах, - в четыре раза.

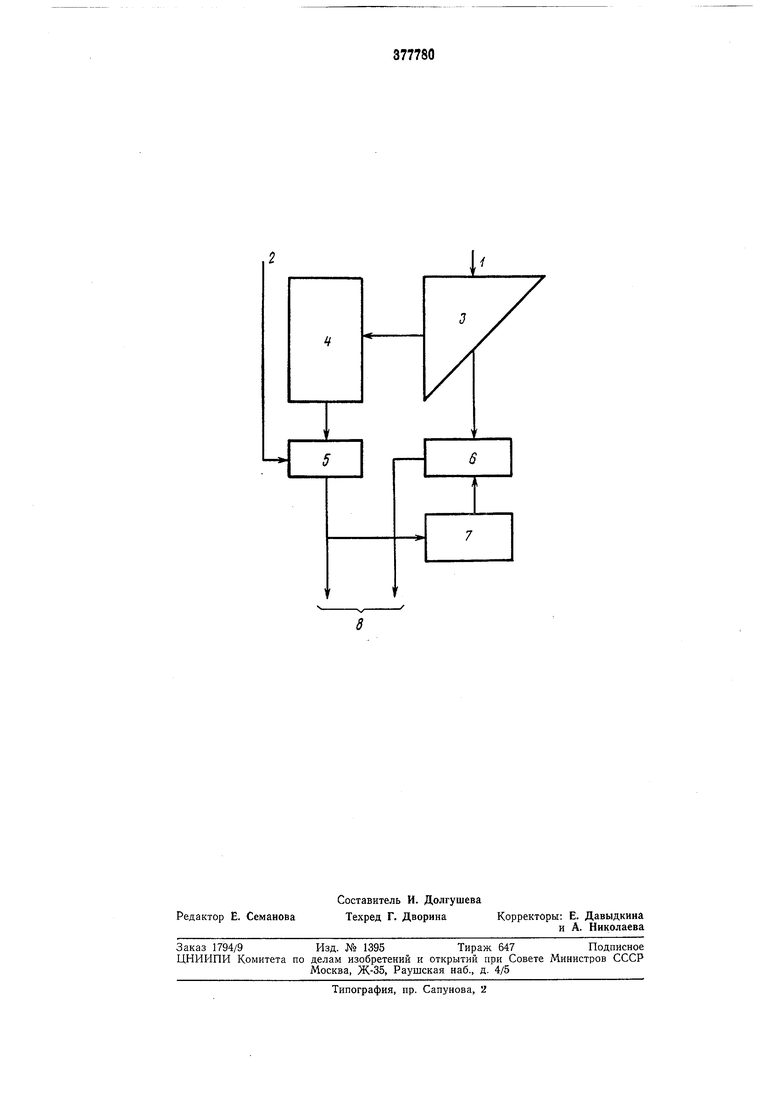

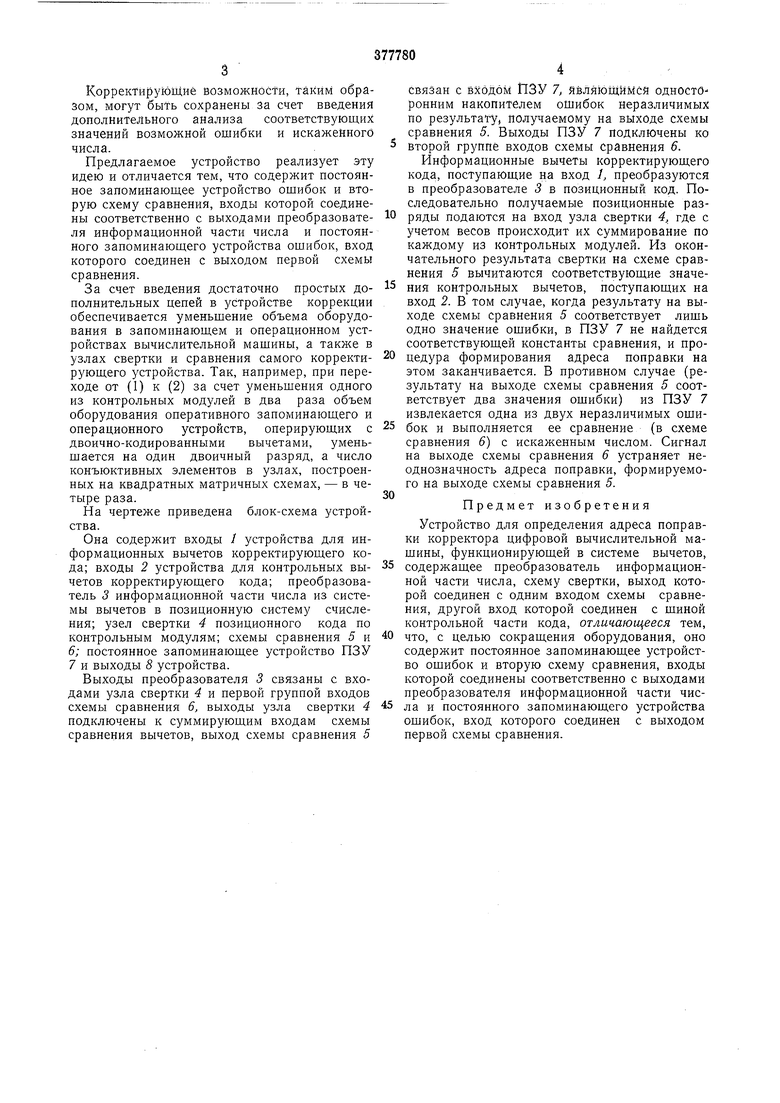

На чертеже приведена блок-схема устройства.

Она содержит входы / устройства для информационных вычетов корректирующего кода; входы 2 устройства для контрольных вычетов корректирующего кода; преобразователь 3 информационной части числа из системы вычетов в позиционную систему счисления; узел свертки 4 позиционного кода по контрольным модулям; схемы сравнения 5 и 6; постоянное запоминающее устройство ПЗУ 7 и выходы S устройства.

Выходы преобразователя 3 связаны с входами узла свертки 4 и первой группой входов схемы сравнения 6, выходы узла свертки 4 подключены к суммирующим входам схемы сравнения вычетов, выход схемы сравнения 5

связан с входом ПЗУ 7, Являющимся односторонним накопителем ощибок неразличимых по результату, получаемому на выходе схемы сравнения 5. Выходы ПЗУ 7 подключены ко 5 второй группе входов схемы сравнения 6.

Информационные вычеты корректирующего кода, поступающие на вход /, преобразуются в преобразователе 3 в позиционный код. Последовательно получаемые позиционные разряды подаются на вход узла свертки 4, где с учетом весов происходит их суммирование по каждому из контрольных модулей. Из окончательного результата свертки на схеме сравнения 5 вычитаются соответствующие значения контрольных вычетов, поступающих на вход 2. В том случае, когда результату на выходе схемы сравнения 5 соответствует лищь одно значение ощибки, в ПЗУ 7 не найдется соответствующей константы сравнения, и процедура формирования адреса поправки на этом заканчивается. В противном случае (результату на выходе схемы сравнения 5 соответствует два значения ощибки) из ПЗУ 7 извлекается одна из двух неразличимых ощи5 бок и выполняется ее сравнение (в схеме сравнения 6) с искаженным числом. Сигнал на выходе схемы сравнения 6 устраняет неоднозначность адреса поправки, формируемого на выходе схемы сравнения 5.

Предмет изобретения

Устройство для определения адреса поправки корректора цифровой вычислительной мащины, функционирующей в системе вычетов,

5 содержащее преобразователь информационной части числа, схему свертки, выход которой соединен с одним входом схемы сравнения, другой вход которой соединен с щиной контрольной части кода, отличающееся тем,

0 что, с целью сокращения оборудования, оно содержит постоянное запоминающее устройство ощибок и вторую схему сравнения, входы которой соединены соответственно с выходами преобразователя информационной части числа и постоянного запоминающего устройства ощибок, вход которого соединен с выходом первой схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU960823A1 |

| Запоминающее устройство с исправлением модульных ошибок | 1985 |

|

SU1302327A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1970 |

|

SU273281A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОБНАРУЖЕНИЯ, ЛОКАЛИЗАЦИИ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2301442C2 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с исправлениемОшибОК | 1979 |

|

SU842979A1 |

| Запоминающее устройство с обнаружением наиболее вероятных ошибок | 1983 |

|

SU1149313A1 |

Авторы

Даты

1973-01-01—Публикация