Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть иснользовано для самоконтроля запоминающих устройств путем обнаружения модульных однонаправленных ощибок в двух модулях памяти и исправления модульных однонаправленных ощибок в одном модуле памяти.

Целью изобретения является повыщение достоверности контроля.

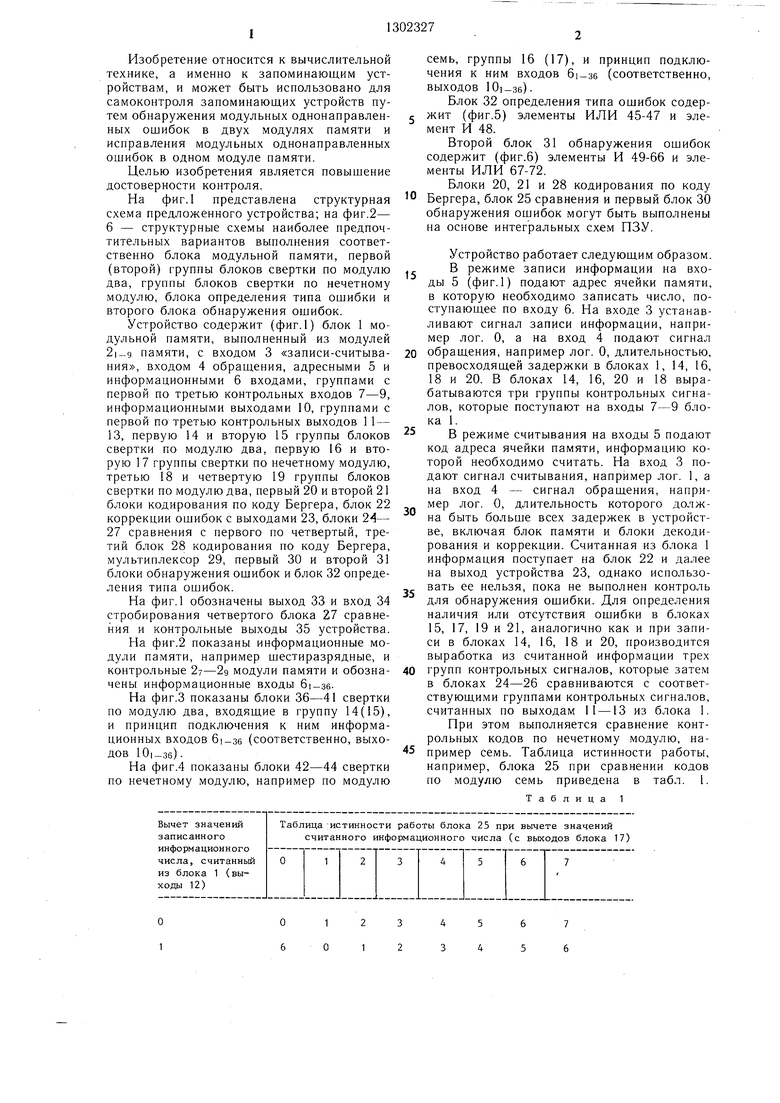

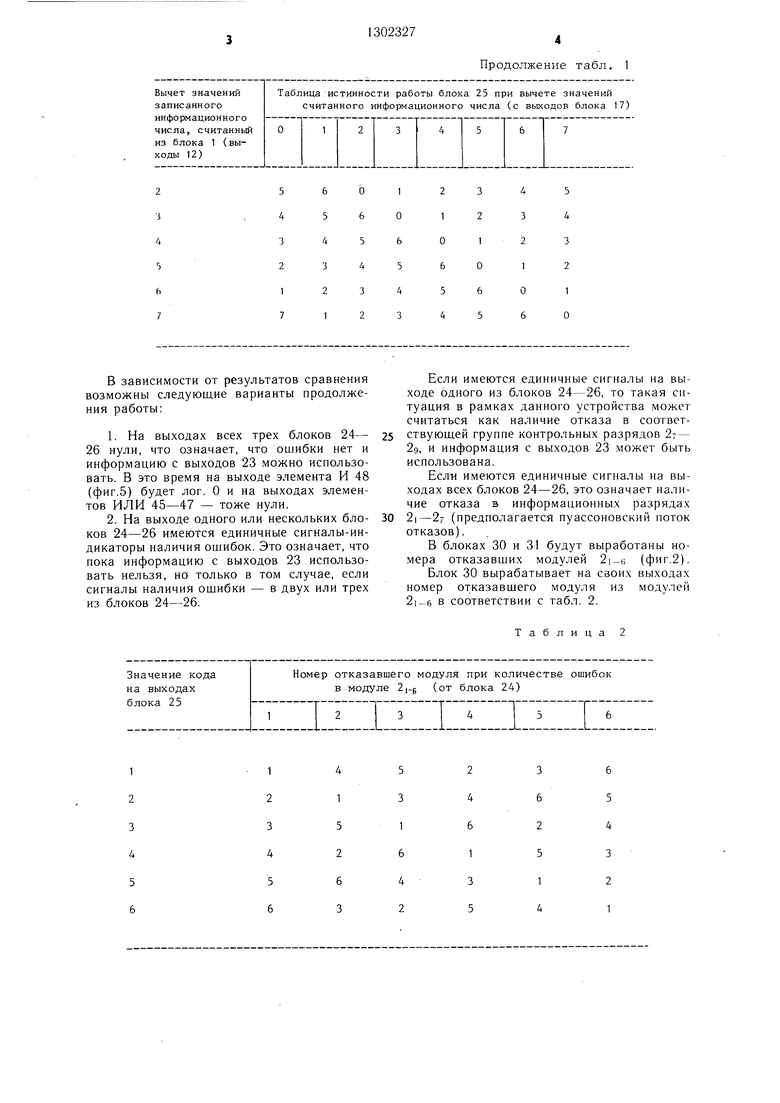

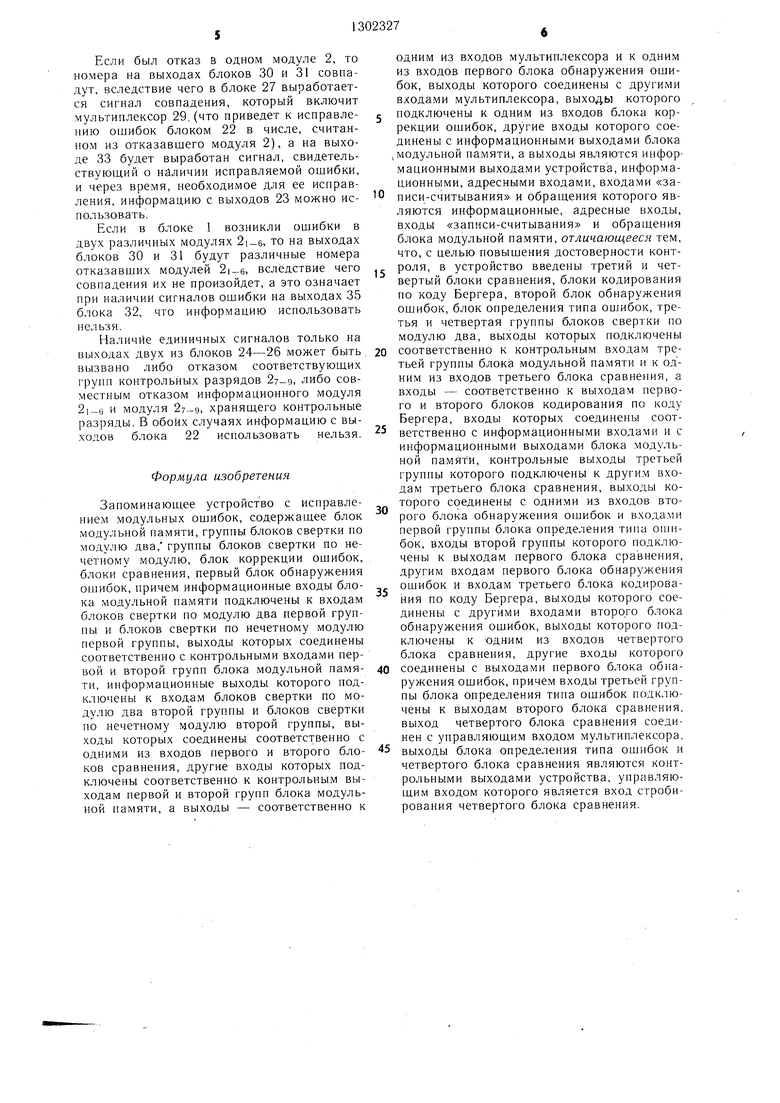

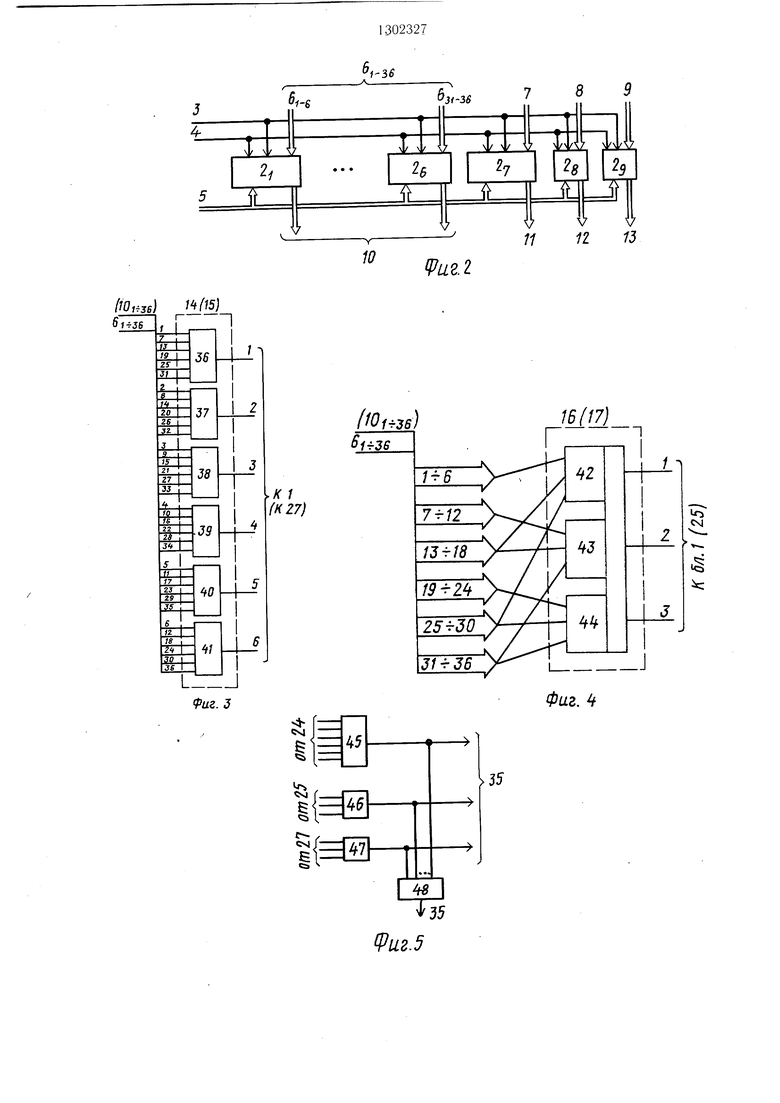

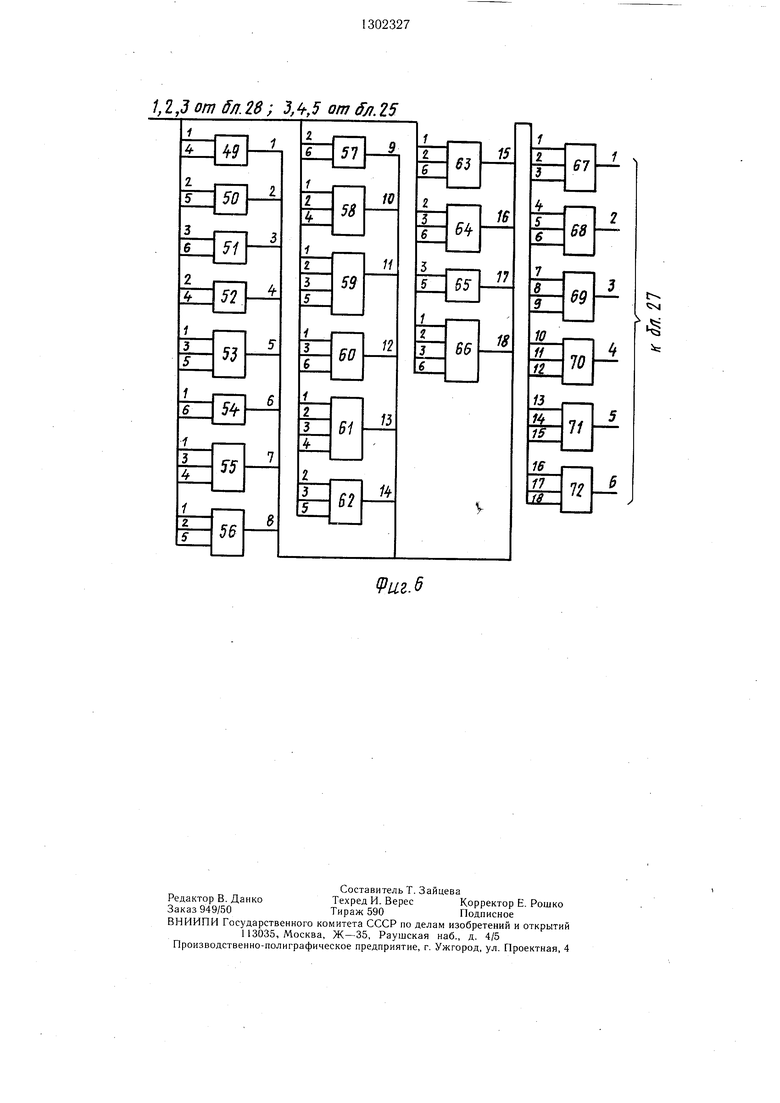

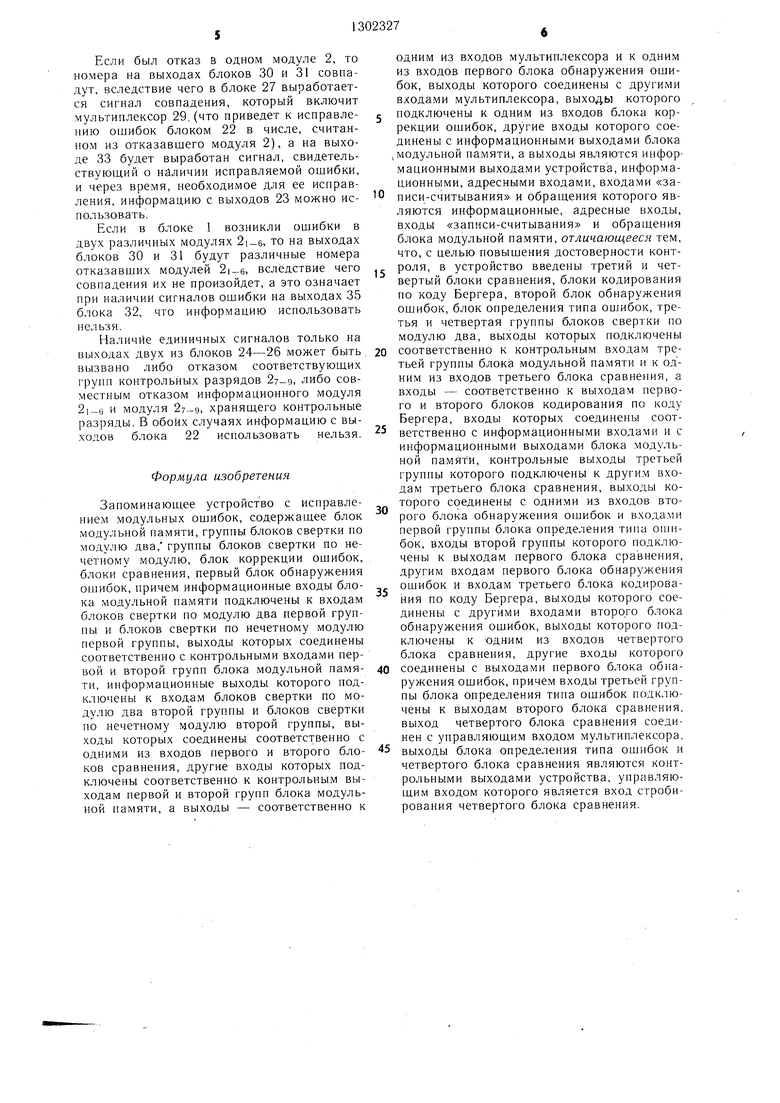

На фиг.1 представлена структурная схема предложенного устройства; на фиг.2- 6 - структурные схемы наиболее предпочтительных вариантов выполнения соответственно блока модульной памяти, первой (второй) группы блоков свертки по модулю два, группы блоков свертки по нечетному модулю, блока определения типа ошибки и второго блока обнаружения ощибок.

Устройство содержит (фиг.1) блок 1 модульной памяти, выполненный из модулей памяти, с входом 3 «записи-считывания, входом 4 обращения, адресными 5 и информационными 6 входами, группами с первой по третью контрольных входов 7-9, информационными выходами 10, группами с первой по третью контрольных выходов 11 - 13, первую 14 и вторую 15 группы блоков свертки по модулю два, первую 16 и вторую 17 группы свертки по нечетному модулю, третью 18 и четвертую 19 группы блоков свертки по модулю два, первый 20 и второй 21 блоки кодирования по коду Бергера, блок 22 коррекции ощибок с выходами 23, блоки 24- 27 сравнения с первого по четвертый, третий блок 28 кодирования по коду Бергера, мультиплексор 29, первый 30 и второй 31 блоки обнаружения ощибок и блок 32 определения типа ощибок.

На фиг.1 обозначены выход 33 и вход 34 стробирования четвертого блока 27 сравнения и контрольные выходы 35 устройства.

На фиг.2 показаны информационные модули памяти, например щестиразрядные, и контрольные модули памяти и обозначены информационные входы Gi-se.

На фиг.З показаны блоки 36-41 свертки по модулю два, входящие в группу 14(15), и принцип подключения к ним информационных входов (соответственно, выходов ).

На фиг.4 показаны блоки 42-44 свертки по нечетному модулю, например по модулю

01234567 60123456

семь, группы 16 (17), и принцип подключения к ним входов (соответственно, выходов lOi-se).

Блок 32 определения типа ощибок содер- жит (фиг.5) элементы ИЛИ 45-47 и элемент И 48.

Второй блок 31 обнаружения ощибок содержит (фиг.6) элементы И 49-66 и элементы ИЛИ 67-72.

Блоки 20, 21 и 28 кодирования по коду Бергера, блок 25 сравнения и первый блок 30 обнаружения ощибок могут быть выполнены на основе интегральных схем ПЗУ.

5

0

Устройство работает следующим образом. В режиме записи информации на входы 5 (фиг.1) подают адрес ячейки памяти, в которую необходимо записать число, поступающее по входу 6. На входе 3 устанавливают сигнал записи информации, например лог. О, а на вход 4 подают сигнал

0 обращения, например лог. О, длительностью, превосходящей задержки в блоках 1, 14, 16, 18 и 20. В блоках 14, 16, 20 и 18 вырабатываются три группы контрольных сигналов, которые поступают на входы 7-9 блока 1.

В режиме считывания на входы 5 подают код адреса ячейки памяти, информацию которой необходимо считать. На вход 3 подают сигнал считывания, например лог. 1, а на вход 4 - сигнал обращения, например лог. О, длительность которого должна быть больще всех задержек в устройстве, включая блок памяти и блоки декодирования и коррекции. Считанная из блока 1 информация поступает на блок 22 и далее на выход устройства 23, однако использовать ее нельзя, пока не выполнен контроль для обнаружения ощибки. Для определения наличия или отсутствия ощибки в блоках 15, 17, 19 и 21, аналогично как и при записи в блоках 14, 16, 18 и 20, производится выработка из считанной информации трех

0 групп контрольных сигналов, которые затем в блоках 24-26 сравниваются с соответствующими группами контрольных сигналов, считанных по выходам 11 -13 из блока 1. При этом выполняется сравнение контрольных кодов по нечетному модулю, на5 пример семь. Таблица истинности работы, например, блока 25 при сравнении кодов по модулю семь приведена в табл. 1.

Таблица 1

В зависимости от результатов сравнения возможны следующие варианты продолжения работы:

1.На выходах всех трех блоков 24- 26 нули, что означает, что ошибки нет и информацию с выходов 23 можно использовать. В это время на выходе элемента И 48 (фиг.5) будет лог. О и на выходах элементов ИЛИ 45-47 - тоже нули.

2.На выходе одного или нескольких блоков 24-26 имеются единичные сигналы-индикаторы наличия ошибок. Это означает, что пока информацию с выходов 23 использовать нельзя, но только в том случае, если сигналы наличия ошибки - в двух или трех из блоков 24-26.

Продолжение табл.

Если имеются единичные сигналы на выходе одного из блоков 24-26, то такая ситуация в рамках данного устройства может считаться как наличие отказа в соответ- ствуюш,ей группе контрольных разрядов 2-- 29, и информация с выходов 23 может быть использована.

Если имеются единичные сигналы на выходах всех блоков 24-26, это означает наличие отказа в информационных разрядах 2|-2 (предполагается пуассоновский поток отказов).

В блоках 30 и 31 будут выработаны номера отказавших модулей (фиг.2).

Блок 30 вырабатывает на своих выходах номер отказавшего модуля из модулей в соответствии с табл. 2.

Таблица 2

Если был отказ в одном модуле 2, то номера на выходах блоков 30 и 31 совпадут, вследствие чего в блоке 27 выработается сигнал совпадения, который включит мультиплексор 29. (что приведет к исправлению ошибок блоком 22 в числе, считанном из отказавшего модуля 2), а на выходе 33 будет выработан сигнал, свидетельствующий о наличии исправляемой ошибки, и через время, необходимое для ее исправления, информацию с выходов 23 можно использовать.

Если в блоке 1 возникли ошибки в двух различных модулях , то на выходах блоков 30 и 31 будут различные номера отказавших модулей , вследствие чего совпадения их не произойдет, а это означает при наличии сигналов ошибки на выходах 35 блока 32, что информацию использовать нельзя.

Наличие единичных сигналов только на выходах двух из блоков 24-26 может быть вызвано либо отказом соответствуюш,их групп контрольных разрядов 27-9, либо совместным отказом информационного модуля 21-6 и модуля 27-9, храняплего контрольные разряды. В обоих случаях информацию с выходов блока 22 использовать нельзя.

Формула изобретения

Запоминающее устройство с исправлением модульных ошибок, содержащее блок модульной памяти, группы блоков свертки по модулю два, группы блоков свертки по нечетному модулю, блок коррекции ошибок, блоки сравнения, первый блок обнаружения опшбок, причем информационные входы блока модульной памяти подключены к входам блоков свертки по модулю два первой группы и блоков свертки по нечетному модулю первой группы, выходы которых соединены соответственно с контрольными входами первой и второй групп блока модульной памяти, информационные выходы которого подключены к входам блоков свертки по модулю два второй группы и блоков свертки по нечетному модулю второй группы, выходы которых соединены соответственно с одними из входов первого и второго блоков сравнения, другие входы которых подключены соответственно к контрольным выходам первой и второй групп блока модульной памяти, а выходы - соответственно к

одним из входов мультиплексора и к одним из входов первого блока обнаружения ошибок, выходы которого соединены с другими входами мультиплексора, выхо4,ы которого

подключены к одним из входов блока коррекции ошибок, другие входы которого соединены с информационными выходами блока , модульной памяти, а выходы являются информационными выходами устройства, информационными, адресными входами, входами «записи-считывания и обращения которого являются информационные, адресные входы, входы «записи-считывания и обращения блока модульной памяти, отличающееся тем, что, с целью повышения достоверности конт роля, в устройство введены третий и четвертый блоки сравнения, блоки кодирования по коду Бергера, второй блок обнаружения ошибок, блок определения типа ошибок, третья и четвертая группы блоков свертки по модулю два, выходы которых подключены

0 соответственно к контрольным входам третьей группы блока модульной памяти и к од - ним из входов третьего блока сравнения, а входы - соответственно к выходам первого и второго блоков кодирования по коду Бергера, входы которых соединены соответственно с информационными входами и с информационными выходами блока модульной памяти, контрольные выходы третьей группы которого подключены к други.м входам третьего блока сравнения, выходы ко- торого соединены с одними из входов второго блока обнаружения ошибок и входами первой группы блока определения типа OIHH- бок, входы второй группы которого подключены к выходам первого блока сравнения, другим входам первого блока обнаружения

ошибок и входам третьего блока кодирования по коду Бергера, выходы которого соединены с другими входами второ.го блока обнаружения ошибок, выходы которого подключены к ОДНИМ из входов четвертого блока сравнения, другие входы которого

0 соединены с выходами первого блока обнаружения ошибок, причем входы третьей группы блока определения типа ошибок подключены к выходам второго блока сравнения, выход четвертого блока сравнения соединен с управляющим входом мультиплексора,

5 выходы блока определения типа ошибок и четвертого блока сравнения являются контрольными выходами устройства, управляющим входом которого является вход строби- рования четвертого блока сравнения.

/-е

(Ю,,зе) 1(15)

б,.3i-36

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением и исправлением модульных ошибок | 1985 |

|

SU1304080A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1986 |

|

SU1322377A1 |

| Запоминающее устройство с обнаружением модульных ошибок | 1985 |

|

SU1302328A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

Изобретение относится к вычислительной технике и может быть использовано для самоконтроля запоминающих устройств путем обнаружения модульных однонаправленных ошибок в двух модулях памяти и исправления таких ошибок в одном модуле памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит блок 1 модульной памяти, выполненный из информационных 2|-б и контрольных 27-9 модулей памяти, группы 14, 15, т 18, 19 блоков свертки по модулю два, группы 16, 17 блоков свертки по нечетному модулю, например модулю семь, блоки 20, 21, 28 кодирования по коду Бергера, блок 22 коррекции ошибок, блоки 24-27 сравнения, мультиплексор 29, блоки 30, 31 обнаружения ошибок и блок 32 определения типа ошибок. При записи в блоках 16, 14, 18, 20 формируется контрольный код, который записывается в контрольные модули памяти одновременно с информацией. При считывании в блоках 15, 17, 19, 21 также формируется контрольный код,который сравнивается с кодом, сформированным при записи. По результатам сравнения определяется наличие опт- бок в двух модулях памяти, в блоках 30, 31 вырабатываются коды номеров отказавншх модулей, блок 32 вырабатывает сигнал некорректируемой ошибки и сигнал для коррекции информации при ошибках в одном модуле памяти. Коррекция информации выполняется в блоке 22 путем инвертирования информации в соответствующих разрядах. 6 ил, 2 табл. СО о 00 ьо

К 1 (К 27)

)

f(iZ. 3

и I

Фаг. Ч

J5

4«

35

Vuz.S

1,1,J от 5л. 28; J,,5 от л. 15

(Puz.5

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU875465A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-30—Подача