Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано для повышения надёжности запоминающих устройств, построенных на интегральных микросхемах памяти.

Целью изобретения является повыщение надежности устройства.

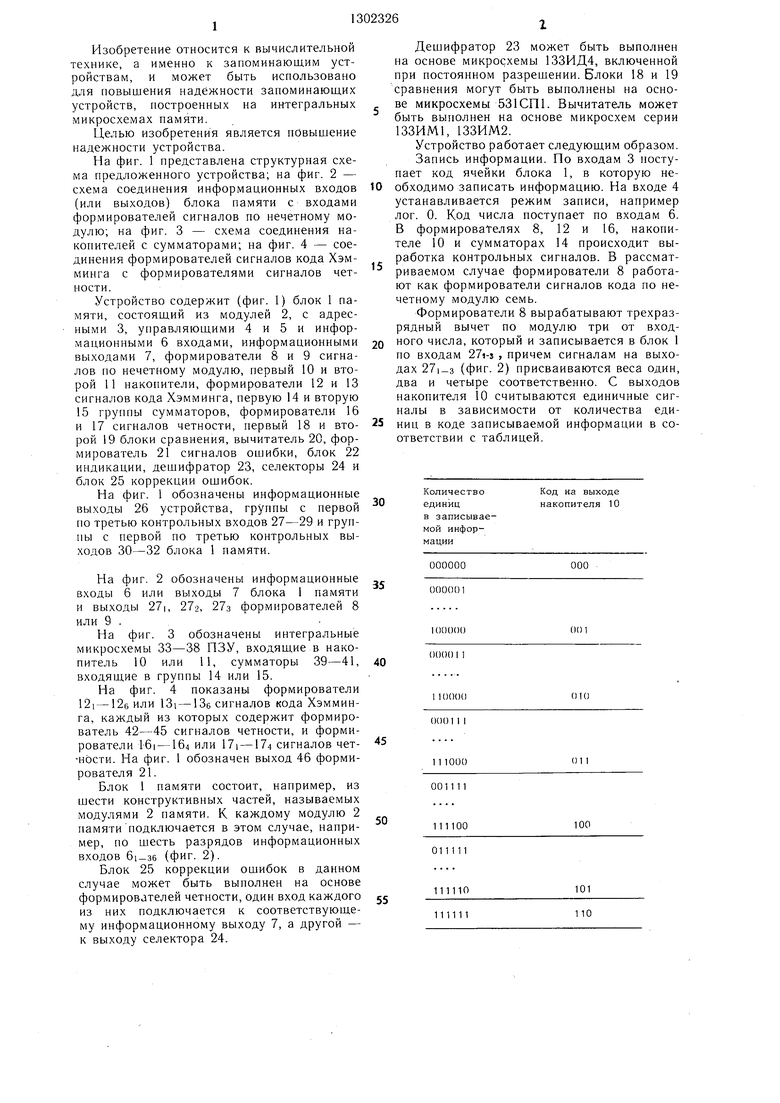

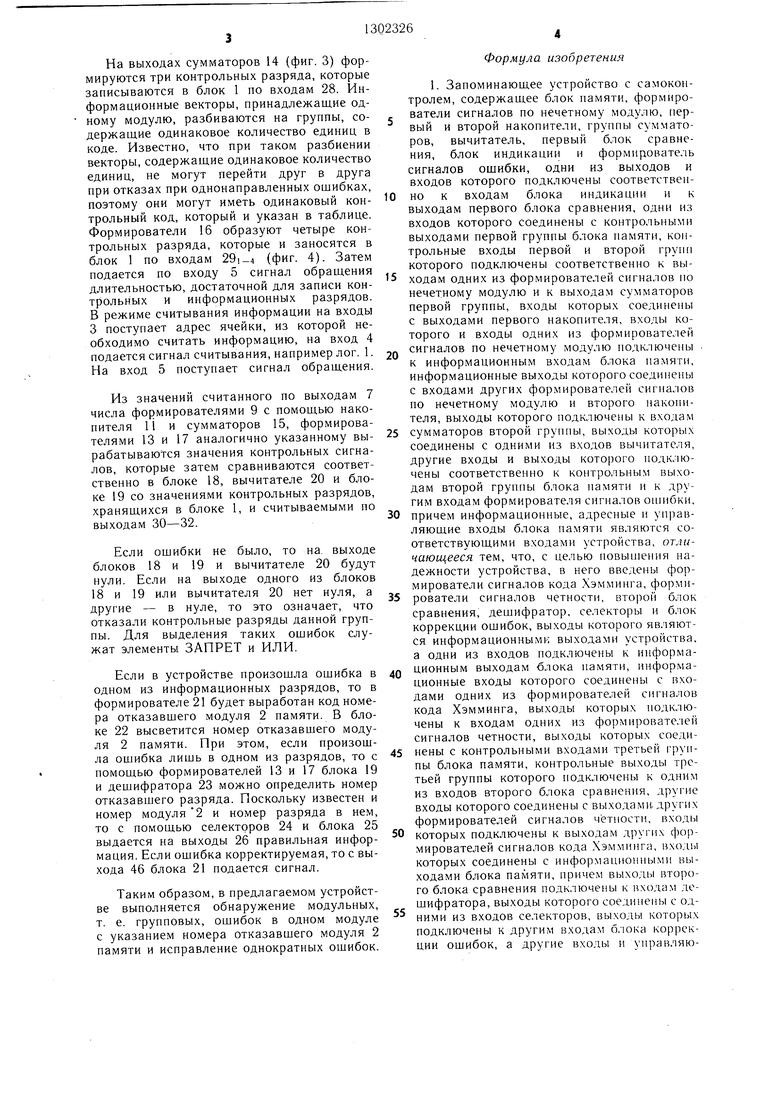

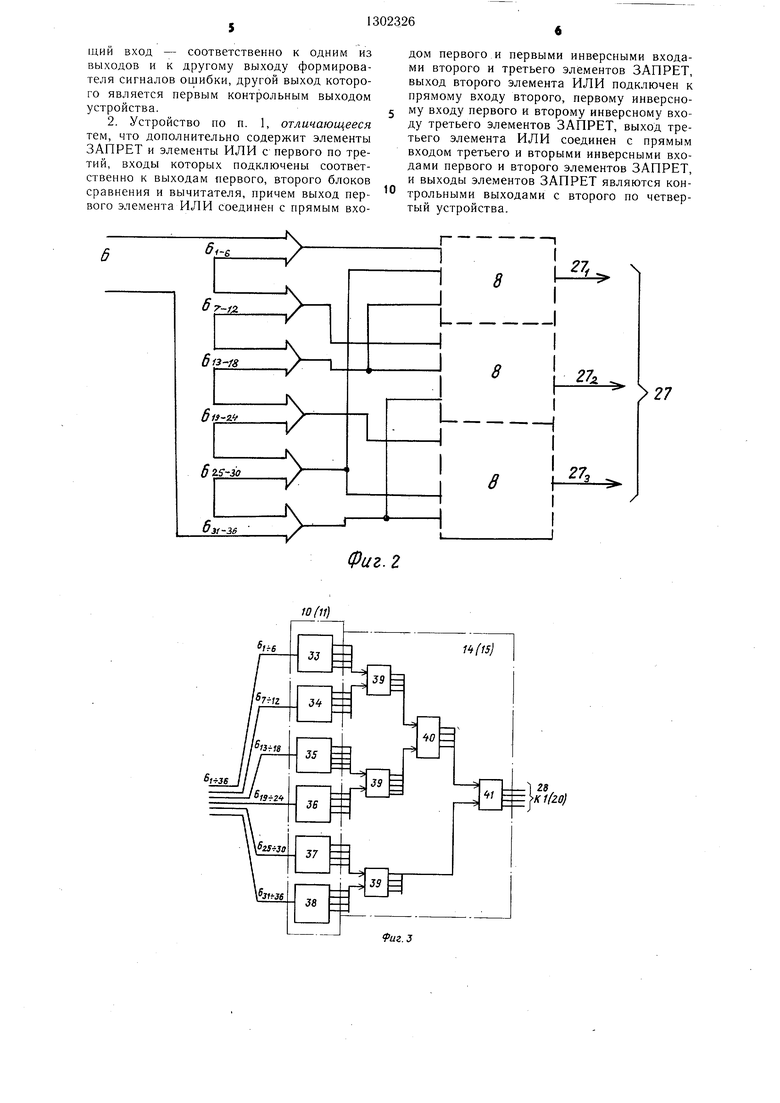

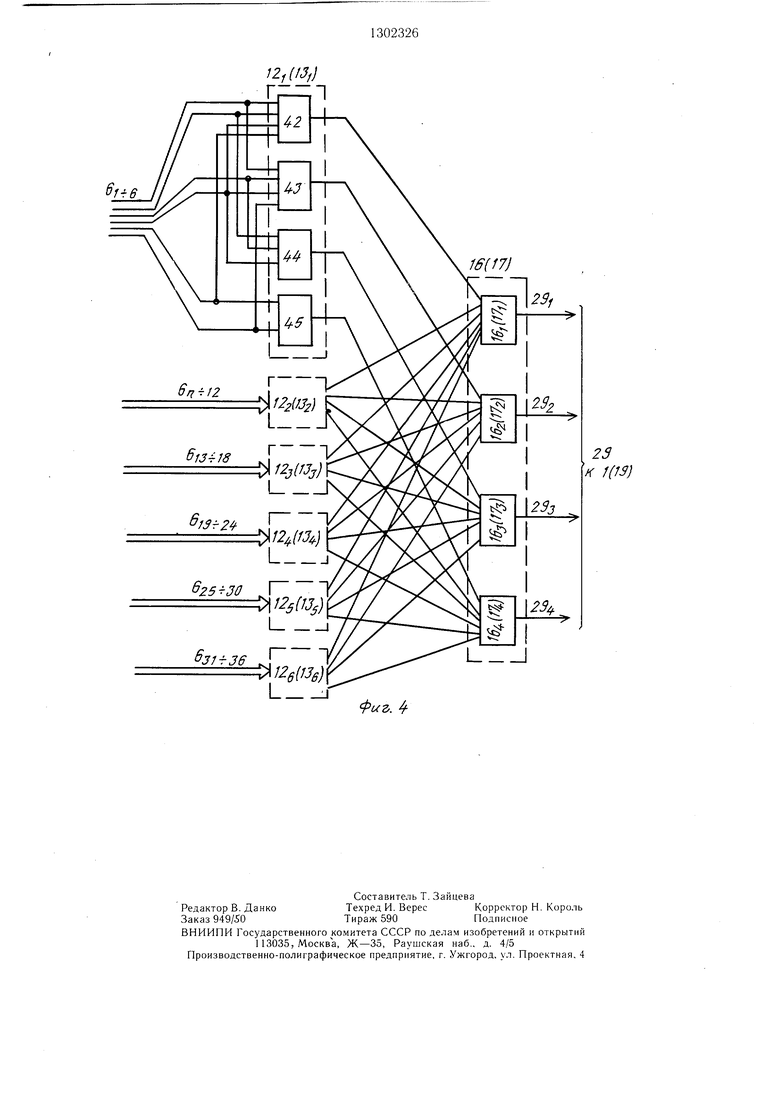

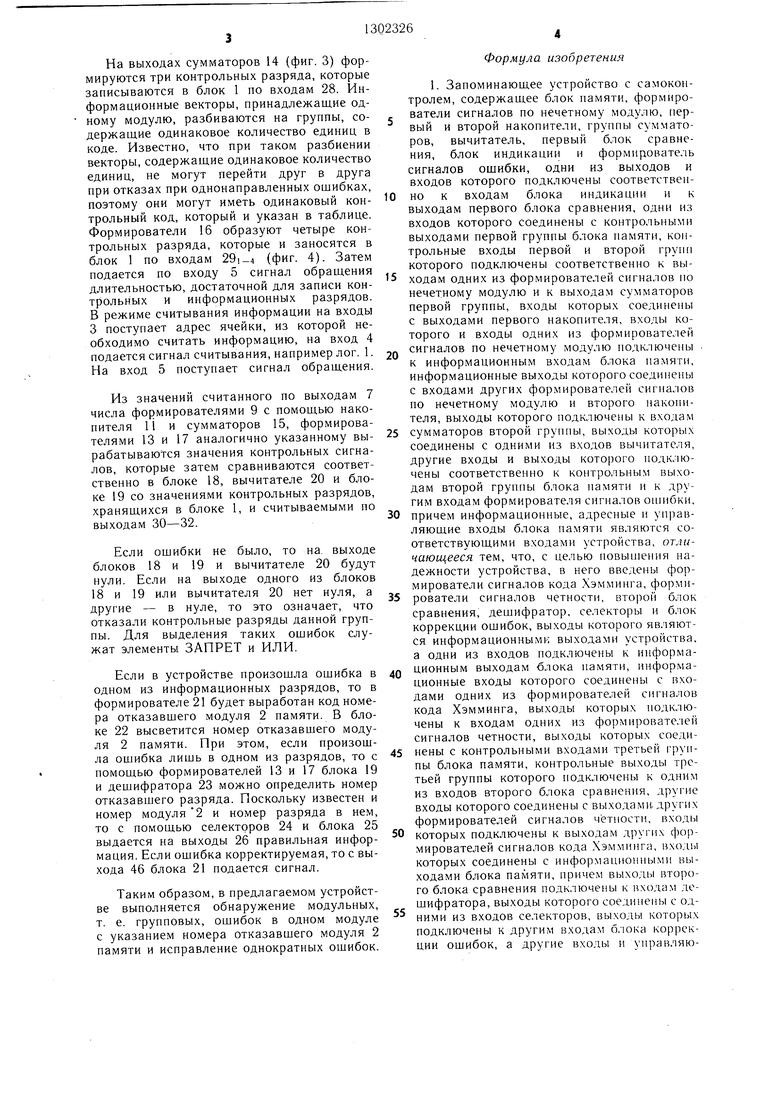

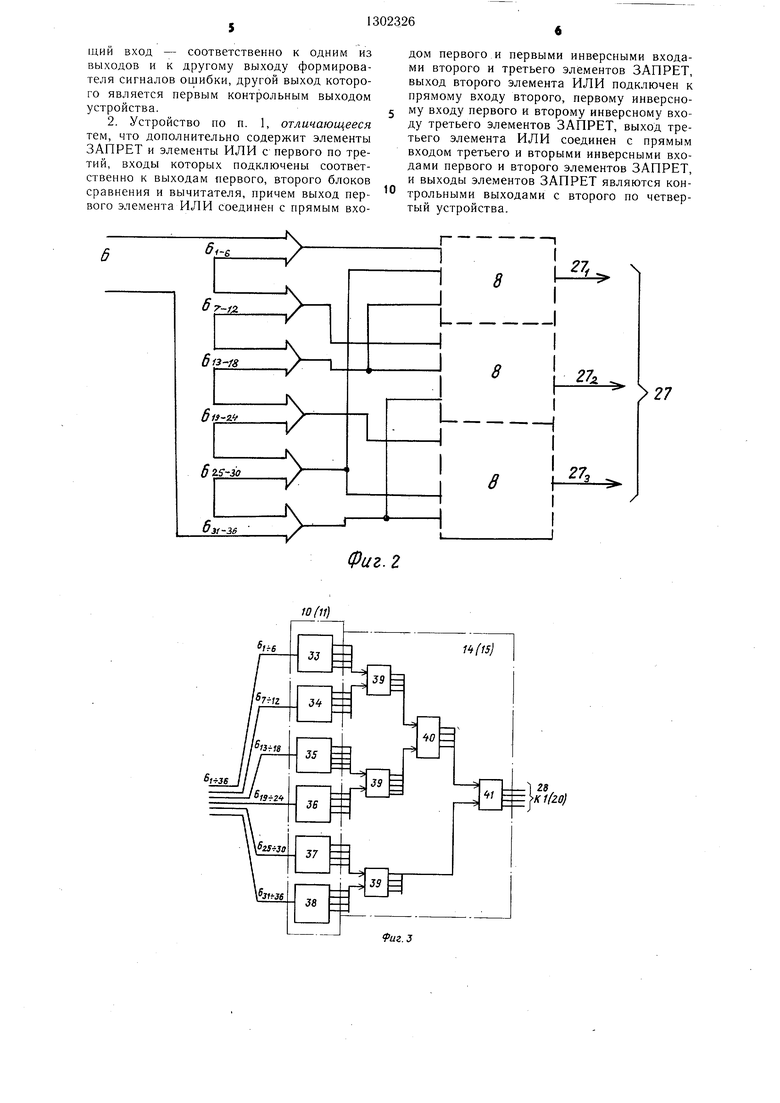

На фиг. 1 представлена структурная схема предложенного устройства; на фиг. 2 - схема соединения информационных входов (или выходов) блока памяти с входами формирователей сигналов по нечетному модулю; на фиг. 3 - схема соединения накопителей с сумматорами; на фиг. 4 - соединения формирователей сигналов кода Хэм- минга с ({зормирователями сигналов четности.

Устройство содержит (фиг. 1) блок 1 памяти, состоящий из модулей 2, с адресными 3, управляющими 4 и 5 и информационными 6 входами, информационными выходами 7, формирователи 8 и 9 сигналов по нечетному модулю, первый 10 и второй 11 накопители, формирователи 12 и 13 сигналов кода Хэмминга, первую 14 и вторую 15 группы сумматоров, формирователи 16 и 17 сигналов четности, первый 18 и второй 19 блоки сравнения, вычитатель 20, формирователь 21 сигналов ощибки, блок 22 индикации, дешифратор 23, селекторы 24 и блок 25 коррекции ощибок.

На фиг. 1 обозначены информационные выходы 26 устройства, группы с первой по третью контрольных входов 27-29 и группы с первой по третью контрольных выходов 30-32 блока 1 памяти.

На фиг. 2 обозначены информационные входы 6 или выходы 7 блока 1 памяти и выходы 27|, 27-2, 27з формирователей 8 или 9 .

На фиг. 3 обозначены интегральные микросхемы 33-38 ПЗУ, входящие в накопитель 10 или 11, сумматоры 39-41, входящие в группы 14 или 15.

На фиг. 4 показаны формирователи 12i-12б или 13i-13б сигналов кода Хэмминга, каждый из которых содержит формирователь 42-45 сигналов четности, и формирователи 16| - 1б4 или 17i -174 сигналов чет- пости. На фиг. 1 обозначен выход 46 формирователя 21.

Блок 1 памяти состоит, например, из щести конструктивных частей, называемых модулями 2 памяти. К каждому модулю 2 памяти подключается в этом случае, например, по шесть разрядов информационных входов (фиг. 2).

Блок 25 коррекции ошибок в данном случае может быть выполнен на основе формирователей четности, один вход каждого из них подключается к соответствующему информационному выходу 7, а другой - к выходу селектора 24.

Дешифратор 23 может быть выполнен на основе микросхемы 133ИД4, включенной при постоянном разрещении. Блоки 18 и 19 сравнения могут быть выполнены на осно- ве микросхемы 531СП1. Вычитатель может быть выполнен на основе микросхем серии 133ИМ1, 133ИМ2.

Устройство работает следующим образом.

Запись информации. По входам 3 поступает код ячейки блока 1, в которую не- обходимо записать информацию. На входе 4 устанавливается режим записи, например лог. 0. Код числа поступает по входам 6. В формирователях 8, 12 и 16, накопителе 10 и сумматорах 14 происходит выработка контрольных сигналов. В рассматриваемом случае формирователи 8 работают как формирователи сигналов кода по нечетному модулю семь.

Формирователи 8 вырабатывают трехразрядный вычет по модулю три от входного числа, который и записывается в блок 1 по входам 27i-s , причем сигналам на выходах (фиг. 2) присваиваются веса один, два и четыре соответственно. С выходов накопителя 10 считываются единичные сигналы в зависимости от количества единиц в коде записываемой информации в соответствии с таблицей.

5

0

5

Количество единиц в записываемой информации

Код на выходе накопителя 10

000000

000

35

000001

ЮОООО

001

40

OOOOI1

На выходах сумматоров 14 (фиг. 3) формируются три контрольных разряда, которые записываются в блок 1 по входам 28. Информационные векторы, принадлежащие одному модулю, разбиваются на группы, содержащие одинаковое количество единиц в коде. Известно, что при таком разбиении векторы, содержащие одинаковое количество единиц, не могут перейти друг в друга при отказах при однонаправленных ощибках, поэтому они могут иметь одинаковый контрольный код, который и указан в таблице. Формирователи 16 образуют четыре контрольных разряда, которые и заносятся в блок 1 по входам (фиг. 4). Затем подается по входу 5 сигнал обращения длительностью, достаточной для записи контрольных и информационных разрядов. В режиме считывания информации на входы 3 поступает адрес ячейки, из которой необходимо считать информацию, на вход 4 подается сигнал считывания, например лог. 1. На вход 5 поступает сигнал обращения.

Из значений считанного по выходам 7 числа формирователями 9 с помощью накопителя И и сумматоров 15, формирователями 13 и 17 аналогично указанному вырабатываются значения контрольных сигналов, которые затем сравниваются соответственно в блоке 18, вычитателе 20 и блоке 19 со значениями контрольных разрядов, хранящихся в блоке 1, и считываемыми по выходам 30-32.

Если ощибки не было, то на. выходе блоков 18 и 19 и вычитателе 20 будут нули. Если на выходе одного из блоков 18 и 19 или вычитателя 20 нет нуля, а другие - в нуле, то это означает, что отказали контрольные разряды данной группы. Для выделения таких ошибок служат элементы ЗАПРЕТ и ИЛИ.

Если в устройстве произощла ощибка в одном из информационных разрядов, то в формирователе 21 будет выработан код номера отказавщего модуля 2 памяти. В блоке 22 высветится номер отказавщего модуля 2 памяти. При этом, если произощла ошибка лишь в одном из разрядов, то с помощью формирователей 13 и 17 блока 19 и дещифратора 23 можно определить номер отказавщего разряда. Поскольку известен и номер модуля 2 и номер разряда в нем, то с помощью селекторов 24 и блока 25 выдается на выходы 26 правильная информация. Если ощибка корректируемая, то с выхода 46 блока 21 подается сигнал.

Таким образом, в предлагаемом устройстве выполняется обнаружение модульных, т. е. групповых, ощибок в одном модуле с указанием номера отказавщего модуля 2 памяти и исправление однократных ошибок.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее блок памяти, формирователи сигналов по нечетному модулю, первый и второй накопители, группы сумматоров, вычитатель, первый блок сравнения, блок индикации и формирователь сигналов ошибки, одни из выходов и входов которого подключены соответственно к входам блока индикации и к выходам первого блока сравнения, одни из входов которого соединены с контрольными выходами первой группы блока памяти, контрольные входы первой и второй групп которого подключены соответственно к выходам одних из формирователей сигналов по нечетному модулю и к выходам сумматоров первой группы, входы которых соединены с выходами первого накопителя, входы которого и входы одних из формирователей

сигналов по нечетному модулю нодключены к информационным входам блока памяти, информационные выходы которого соединены с входами других формирователей сигналов по нечетному модулю и второго накопителя, выходы которого подключены к входам

сумматоров второй группы, выходы которых соединены с одними из входов вычитателя, другие входы и выходы которого подключены соответственно к контрольным выходам второй группы блока памяти и к другим входам формирователя сигналов ошибки,

причем информационные, адресные и управляющие входы блока памяти являются соответствующими входами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены формирователи сигналов кода Хэмминга, формирователи сигналов четности, второй блок сравнения, дешифратор, селекторы и б.чок коррекции ошибок, выходы которого являются информационными выходами устройства. а одни из входов подключены к информационным выходам блока памяти, информационные входы которого соединены с входами одних из формирователей сигна.чов кода Хэмминга, выходы которых подключены к входам одних из формирователей сигналов четности, выходы которых соедииены с контрольными входами третьей группы блока памяти, контрольные выходы третьей группы которого подключены к одним из входов второго блока сравнения, другие входы которого соединены с выходами, других формирователей сигналов четности, входы

которых подключены к выходам других формирователей сигналов кода Хэмминга, входы которых соединены с информационными выходами блока памяти, причем выходы второго блока сравнения подключены к входам дешифратора, выходы которого соединены с одними из входов селекторов, выходы которых подключены к другим Е ходам б. юка коррекции ошибок, а другие входы уиравляю

щии вход - соответственно к одним из выходов и к другому выходу формирователя сигналов ошибки, другой выход которого является первым контрольным выходом устройства.

2. Устройство по п. 1, отличающееся тем, что дополнительно содержит элементы ЗАПРЕТ и элементы ИЛИ с первого по третий, входы которых подключены соответственно к выходам первого, второго блоков сравнения и вычитателя, причем выход первого элемента ИЛИ соединен с прямым вхо6.,

6 3-fs

ди246 5 3t.

30

дом первого и первыми инверсными входами второго и третьего элементов ЗАПРЕТ, выход второго элемента ИЛИ подключен к прямому входу второго, первому инверсному входу первого и второму инверсному входу третьего элементов ЗАПРЕТ, выход третьего элемента ИЛИ соединен с прямым входом третьего и вторыми инверсными входами первого и второго элементов ЗАПРЕТ, и выходы элементов ЗАПРЕТ являются контрольными выходами с второго по четвертый устройства.

I

8

27.

27

8

27,

б,,.

3(-3в

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с авто-НОМНыМ КОНТРОлЕМ | 1979 |

|

SU809403A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

Изобретение относится к вычислительной технике и может быть применено в запоминающих устройствах, выполненных из интегральных микросхем памяти. Целью изобретения является повышение надежности устройства. Устройство содержит блок 1 памяти, выполненный из модулей 2 памяти. Фиг.1 например из интегральных микросхем памяти, формирователи 8, 9 сигналов но нечетному модулю, два накопителя 10, 11, формирователи 12, 13 сигналов кода Хэмминга, две группы сумматоров 14, 15, формирователи 16, 17 сигналов четности, два блока 18, 19 сравнения, вычитатель 20, формирователь 21 сигналов ошибки, дешифратор 23, селекторы 24, блок 25 коррекции ошибок и блок 22 индикации. Устройство обеспечивает обнаружение модульных, т. е. групповых, ошибок в одном модуле с указанием в блоке индикации номера отказавшего модуля и исправление однократных ошибок путем сравнения контрольных сигналов, формируемых при записи информации и записываемых в блок памяти, с контрольными сигналами, формируемыми аналогичным способом из считанной информации 1 з.п. ф-лы, 4 ил., 1 табл. (Л со о tsD ОО ьэ Oi

6,,,

1(15)

0

Z8

К 1(2.0)

fuz.

Ф22{и2}

Dl )

6ig

)3г2

ШЩ J

2з(Щ

6з1-г36

2e(J3s)

§

23з

I

фиг .

| Запоминающее устройство с автономным контролем | 1980 |

|

SU881877A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-07—Публикация

1985-12-16—Подача