Изобретение относится к области вычислительной техники и может быть применено для обнаружения одиночных оплибок при передаче информации в цифровых машинах.

Известно устройство для контроля на четность передачи цифровой информации от одного устройства в вычислительной машине к другому, содержащее регистр и логические схемы «И и «ИЛИ.

К недостаткам устройств контроля данного типа относится довольно значительный объем необходимого для контроля оборудования.

Целью предлагае.мого изобретения является сокращение необходимого оборудования и упрощение схемы контроля информации на четность. Согласно изобретению поставленная цель достигается определением логически четного числа единиц, записанных в контролируемом регистре.

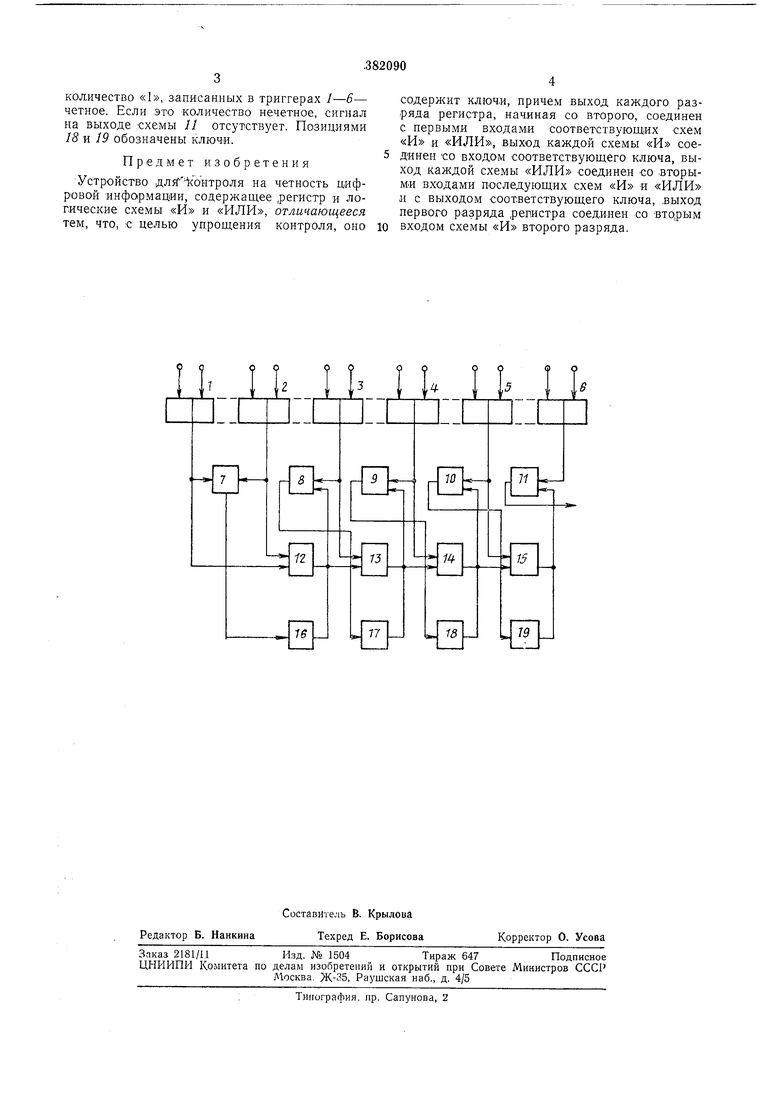

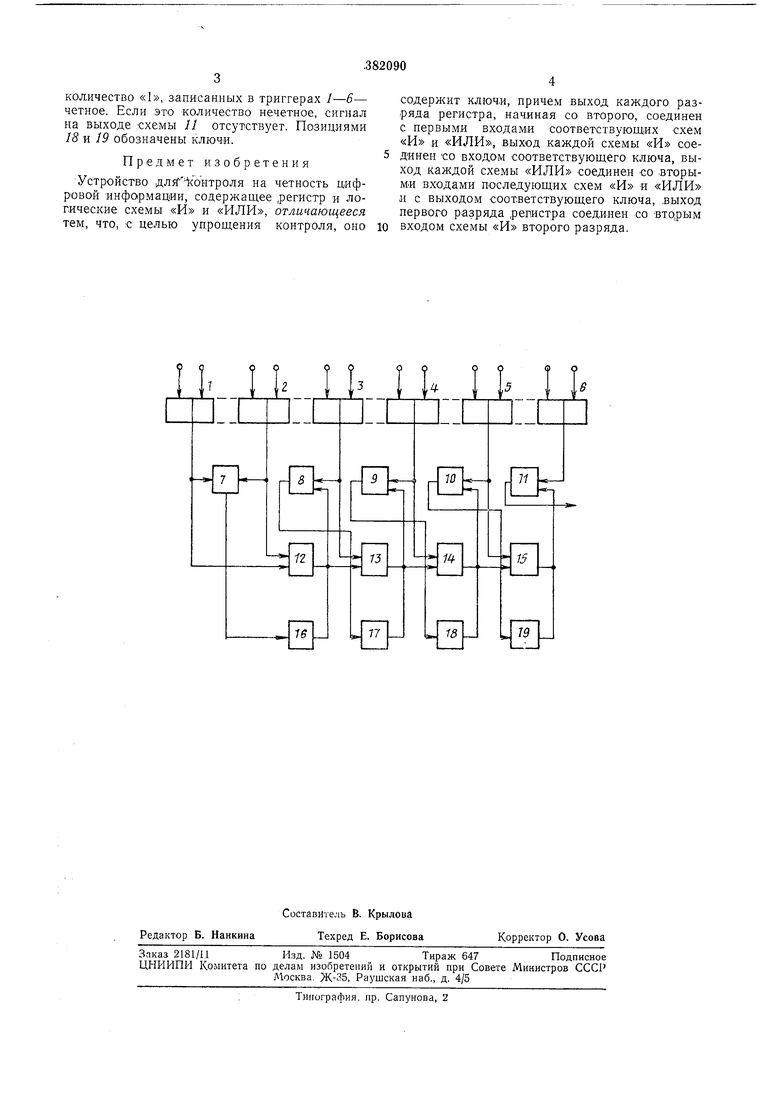

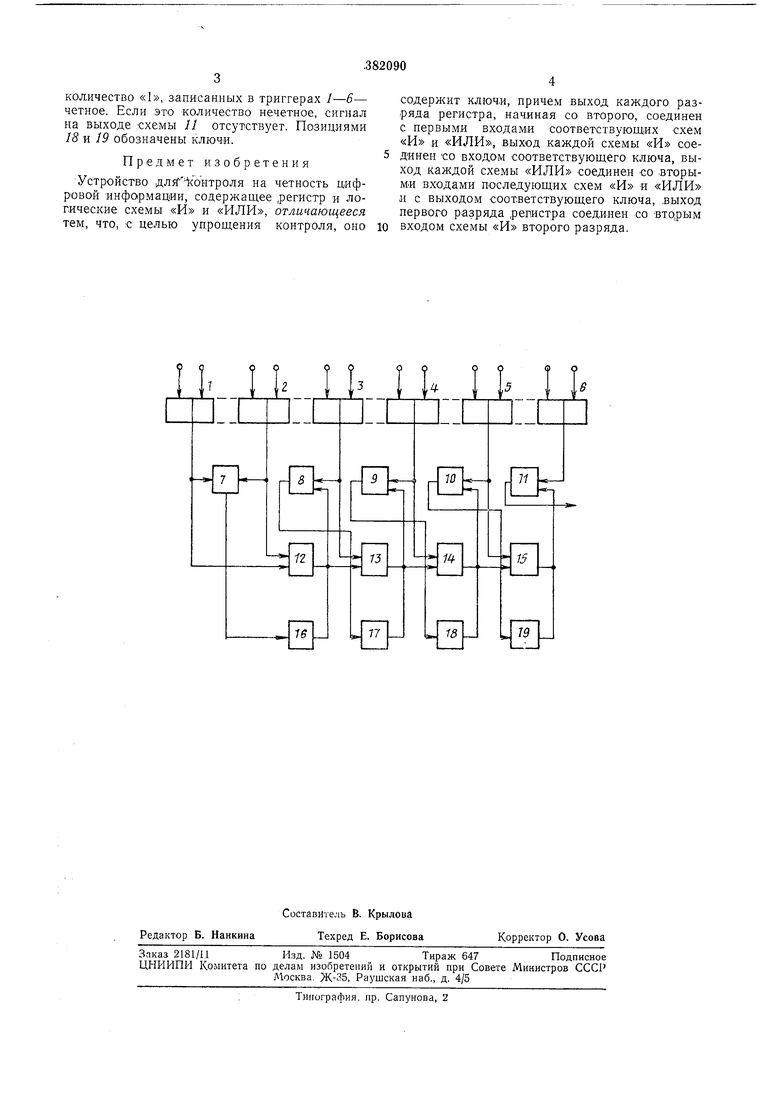

Для этого выход каждого разряда регистра, начиная со второго, соединен с первыми входами соответствующих схем «И и «ИЛИ, выход каждой схемы «И соединен со входом соответствующего ключа, выход каждой схемы «ИЛИ соединен со вторыми в.ходами последующих схем «И и «ИЛИ ,и с выходом соответствующего ключа, выход первого разряда регистра соединен со вторым входом схемы «И второго разряда.

Схема предлагаемого устройства изображена на чертеже.

Выходные сигналы с триггеров /-5 регистра, информация в котором контролируется, я

триггера 6 контрольного разряда поступают на входы схем «И 7-// и входы схем «ИЛИ 12-15. Совпадение сигналов «1 на какой-либо схеме «И шунтирует выход соответствующей схемы «ИЛИ. Так, если в триггерах / и 2 регистра записаны сигналы «1, то схема «И 7 вырабатывает сигнал совпадения, который открывает ключ 16, выход которого соединен с выходом схемы «ИЛИ 12, и шунтирует выход схемы 12, запрещая прохождение сигнала «1 с выхода схемы 12 на входы схем «И 8 и «ИЛИ 13. В том случае, если на схему «И 7 поступает один сигнал «1 (с триггера / или триггера 2 регистра), на выходе с.хемы «ИЛИ 12 сигнал «1 не

шунтируется (так как ключ 16 закрыт) и поступает на входы схем 8 и 13. Пр.и этом сигнал с выхода с.хемы 13 поступит на входы схем 9 и 14 только в том случае, если в триггере 3 записан сигнал «О. Если в триггере 3

записан сигнал «1, схема «И 5 вырабатывает сигнал совпадения, который зашунтирует открытым ключом 17 выход схемы «ИЛИ 13 и т. д. Иа выходе схемы «И // появляется сигнал только в случае совпадения сигналов

с выхода схемы «ИЛИ 15 и триггера 6, если

количество «1, записанных в триггерах 1-6- четное. Если это количество нечетное, сигнал на выходе схемы 11 отсутствует. Позициями 18 и 19 обозначены ключи.

Предмет изобретения

Устройство длй1 онтроля на четность цифровой информации, содержащее регистр и логические схемы «И и «ИЛИ, отличающееся тем, что, с целью уцрощения контроля, оно

содержит ключ.и, нричем выход каждого разряда регистра, начиная со второго, соединен с первыми входами соответствующих схем «И и «ИЛИ, выход каждой схемы «И соединен СО входом соответствующего ключа, выход каждой схемы «ИЛИ соединен со -вторыми входами последующих схем «И и «ИЛИ и с выходом соответствующего ключа, БЫХОД первого разряда регистра соединен со вторым входом схемы «И второго разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор команд | 1973 |

|

SU467466A1 |

| Устройство для декодирования фазоманипулированного кода | 1989 |

|

SU1633494A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1972 |

|

SU330554A1 |

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

| Устройство для контроля работы технологического оборудования | 1982 |

|

SU1084846A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

о .«с00. - 0000

1 1 . 1 If 11 1 . .IF i ,н.

Авторы

Даты

1973-01-01—Публикация