1

Известно запоминающее устройство (ЗУ), содержащее регистр адреса, выходы которого через дещифраторы, адреса подключены ко входам накопителей, выходы которых подсоединены к соответствующим регистрам слова, схему равенства кодов, входы которой подключены к выходам регистров слова, а выход - к одному входу схемы «И, другой вход которой подключен к блоку управления, а выход - к одному из регистров слова, схему «ИЛИ, группы схем «И по количеству накопителей и выходной регистр.

Недостатком известного устройства является то, что при наличии отказов в одноименных запоминающих ячейках накопителей не происходит выдачи информации. Это снижает надежность и эффективность известного ЗУ.

Описываемое ЗУ отличается от известного тем, что оно содержит дополнительные регистры слова по количеству накопителей, входы которых подключены к выходам соответствующих основных регистров слова, схемы поразрядной проверки по количеству накопителей, одни входы которых подсоединены к выходам соответствующих основных регистров слова, другие-к выходам дополнительных регистров слова, а выходы - к управляющим входам групп схем «И, информационные входы которых подключены к блоку управления, а выходы - ко входам соответствующих основных

регистров слова, выходы которых через схему «ИЛИ подсоединены к выходному регистру.

Это позволяет повысить надежность устройства.

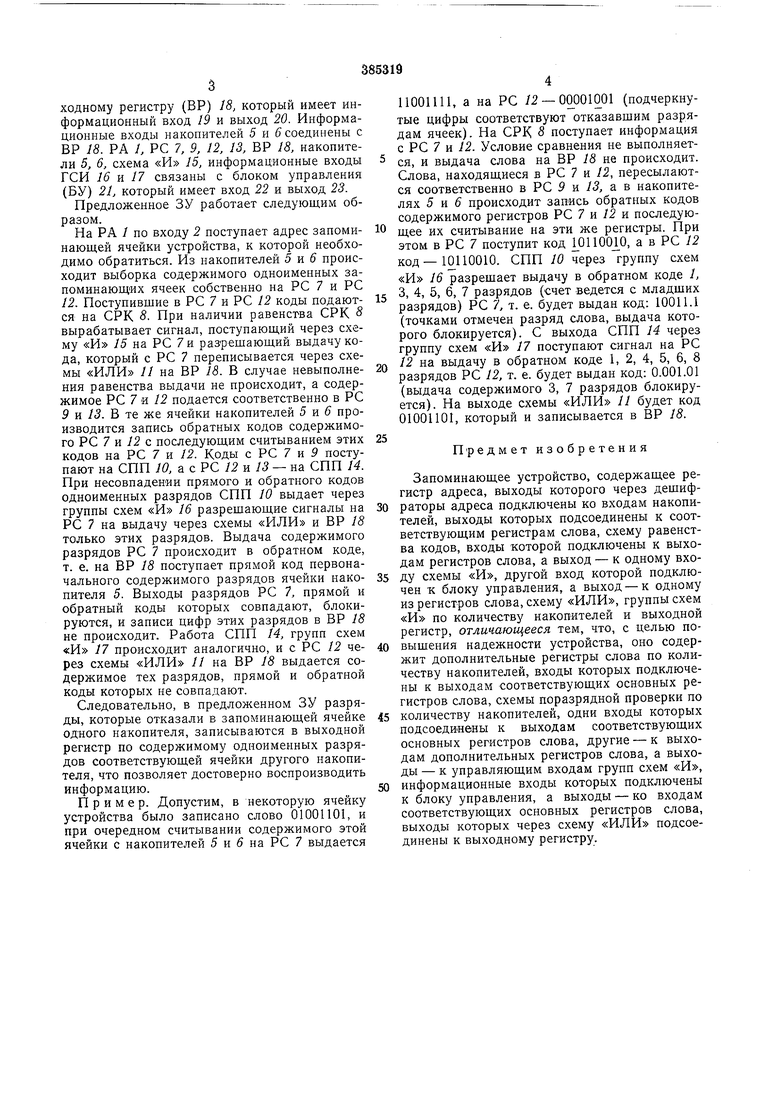

На чертеже дана блок-схема предложенного ЗУ, содержащего, например, два накопителя.

ЗУ содержит регистр адреса (РА) / с информационным входом 2. Выход регистра РА

У связан через дешифратор адреса (ДА) 3 и 4 соответственно с накопителями 5 и 6. Накопитель 5 соединен с основным регистром слова (PC) 7, один выход которого связан со схемой равенства кодов (СРК) 8, дополнительным PC

Р и схемой поразрядной нроверки (СПП) 10, а другой - со схемами «ИЛИ //. Другой накопитель б соединен с основным PC 12, один выход которого подключен к СРК 8, дополнительному PC 13 и СПП 14, а другой - к схемам «ИЛИ //. Схема CPKS через схему «И 15 соединена с PC 7. Выход СПП 10 связан с выходом PC 9, а выход СПП 10 - с управляющими входами групп схем «И 16 выходы которых соединены с управляющими входами PC

7. PC 13 соединен с СПП 14, выходы которой подключены к управляющим входам групп схем «И 17, выходы которых связаны с управляющими выходами PC 12. Выход схем «ИЛИ // подключен к выходному регистру

PC 12. Выход схем «ИЛИ // подключен к выходному регистру (ВР) 18, который имеет информационный вход 19 и выход 20. Информационные входы накопителей 5 и 5 соединены с ВР 18. РА 1, PC 7, 9, 12, 13, ВР 18, накопители 5, 6, схема «И 15, информационные входы геи 16 и 17 связаны с блоком управления (БУ) 21, который имеет вход 22 и выход 23.

Предложенное ЗУ работает следующим образом.

На РА / по входу 2 поступает адрес запоминающей ячейки устройства, к которой необходимо обратиться. Из накопителей 5 и 5 происходит выборка содержимого одноименных запоминающих ячеек собственно на PC 7 и PC 12. Поступивщие в PC 7 и PC 12 коды подаются на СРК 8. При наличии равенства СРК вырабатывает сигнал, поступающий через схему «И 15 на PC 7 и разрешающий выдачу кода, который с PC 7 переписывается через схемы «ИЛИ //на ВР 18. В случае невыполнения равенства выдачи не происходит, а содержимое PC 7 и 12 подается соответственно в PC 9 и /5. В те же ячейки накопителей 5 и б производится запись обратных кодов содержимого PC 7 и /2 с последующим считыванием этих кодов на PC 7 и 12. Коды с PC 7 и 9 поступают на СПП 10, а с PC /2 и /5 - на СПП 14. При несовпадении прямого и обратного кодов одноименных разрядов СПП 10 выдает через группы схем «И 16 разрешающие сигналы на PC 7 на выдачу через схемы «ИЛИ и ВР 18 только этих разрядов. Выдача содержимого разрядов PC 7 происходит в обратном коде, т. е. на ВР 18 поступает прямой код первоначального содержимого разрядов ячейки накопителя 5. Выходы разрядов PC 7, прямой и обратный коды которых совпадают, блокируются, и записи цифр этих разрядов в ВР 18 не происходит. Работа СПП 14, групп схем «И 17 происходит аналогично, и с PC 12 через схемы «ИЛИ // на ВР 18 выдается содержимое тех разрядов, прямой и обратной коды которых не совпадают.

Следовательно, в предложенном ЗУ разряды, которые отказали в запоминающей ячейке одного накопителя, записываются в выходной регистр по содержимому одноименных разрядов соответствующей ячейки другого накопителя, что позволяет достоверно воспроизводить информацию.

Пример. Допустим, в некоторую ячейку устройства было записано слово 01001101, и при очередном считывании содержимого этой ячейки с накопителей 5 и б на PC 7 выдается

11001111, а на PC /2 -ООООЮО (подчеркнутые цифры соответствуют отказавщим разрядам ячеек). На СРК| 8 поступает информация с PC 7 и 12. Условие сравнения не выполняется, и выдача слова на ВР 18 не происходит. Слова, находящиеся в PC 7 и 12, пересылаются соответственно в PC 9 и , а в накопителях 5 и б происходит запись обратных кодов содержимого регистров PC 7 и /2 и последующее их считывание на эти же регистры. При этом в PC 7 поступит код H}1100J 0, а в PC 12 код-1 110010. СПП 10 через группу схем «И 16 разрешает выдачу в обратном коде /,

3, 4, 5, 6, 7 разрядов (счет ведется с младщих разрядов) PC 7, т. е. будет выдан код: 10011.1 (точками отмечен разряд слова, выдача которого блокируется). С выхода СПП 14 через группу схем «И 17 поступают сигнал на PC

12 на выдачу в обратном коде 1, 2, 4, 5, 6, 8 разрядов PC 12, т. е. будет выдан код: 0.001.01 (выдача содержимого 3, 7 разрядов блокируется). На выходе схемы «ИЛИ // будет код 01001101, который и записывается в ВР 13.

Предмет изобретения

Запоминающее устройство, содержащее регистр адреса, выходы которого через дешифраторы адреса подключены ко входам накопителей, выходы которых подсоединены к соответствующим регистрам слова, схему равенства кодов, входы которой подключены к выходам регистров слова, а выход - к одному вхоДУ схемы «И, другой вход которой подключен к блоку управления, а выход - к одному из регистров слова, схему «ИЛИ, группы схем «И по количеству накопителей и выходной регистр, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительные регистры слова по количеству накопителей, входы которых подключены к выходам соответствующих основных регистров слова, схемы поразрядной проверки по

количеству накопителей, одни входы которых подсоединены к выходам соответствующих основных регистров слова, другие - к выходам дополнительных регистров слова, а выходы - к управляющим входам групп схем «И,

информационные входы которых подключены к блоку управления, а выходы - ко входам соответствующих основных регистров слова, выходы которых через схему «ИЛИ подсоединены к выходному регистру.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО:1 Т 5•..:' 'Уу | 1973 |

|

SU436388A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368647A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| УСТРОЙСТВО для РАСПРЕДЕЛЕНИЯ ПАМЯТИ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1971 |

|

SU318948A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

Авторы

Даты

1973-01-01—Публикация