(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

изрегистров сдвига, первые входы -хчемсптов ИЛИ первой группы подключены к выходам другого регистра сдвига, вторые входы - к выходам выходного регистра слова, третьи входы: - к выходам основных регистров слова, выходы 6vTOKOB поразрядного контроля через элементы ИЛИ четвертой группы соединены с одними управляющими входами коммутаторов и регистров сдвига, другие управляюихие входы которых подключены к выходам дешифратора.

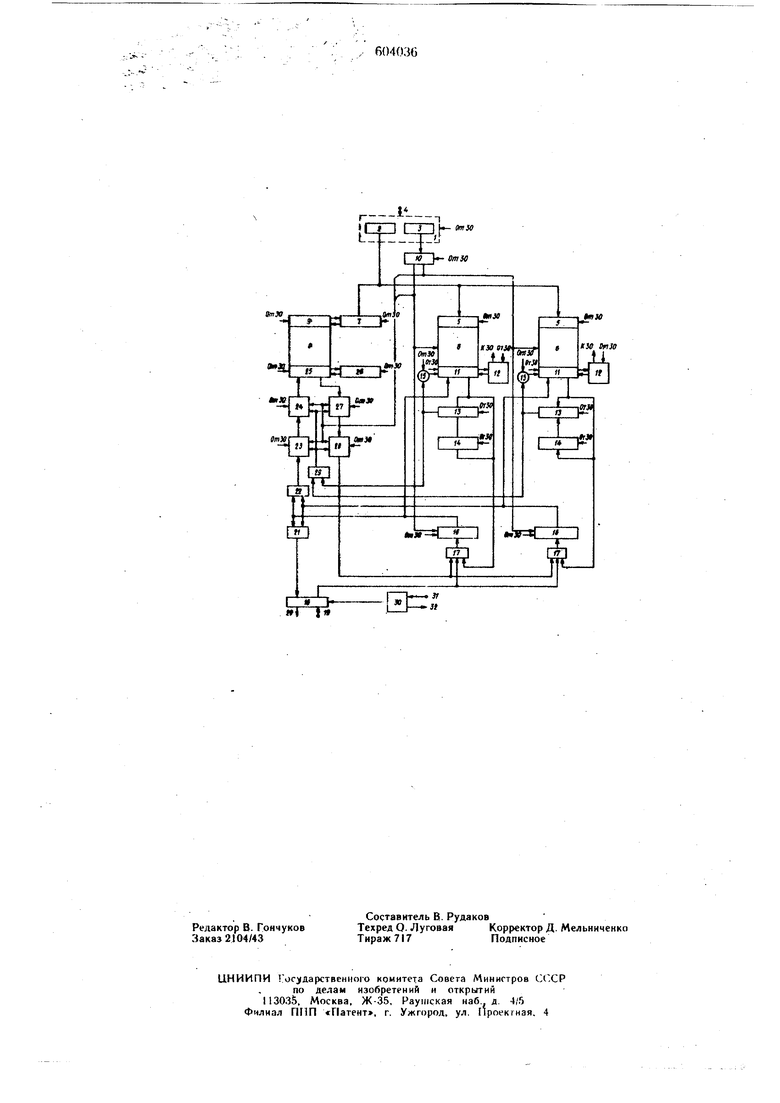

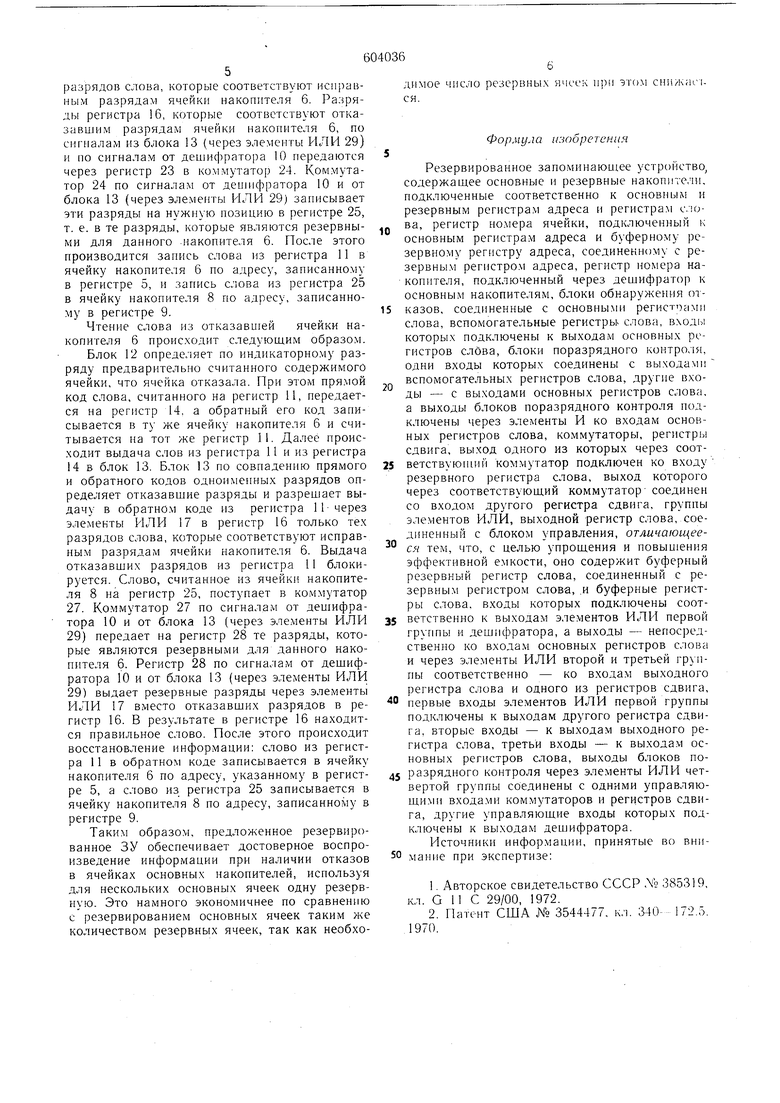

На чертеже показана структурная схема предложенного ЗУ.

Оно содержит регистр 1 адреса, состояп1ий из регистра 2 номера ячейки и регистра 3 номера накопителя. Регистр 1 имеет информационный вход 4. Регистр 2 подключен к основным регистрам адреса 5 основных накопителей 6 и к буферному резервно.му регистру адреса 7 резервного накопителя 8. Регистр 7 связан с резервным регистром адреса 9 накопителя 8. Регистр 3 через дешифратор 10 соединен с накопителями 6. Предположим, что емкость основного накопит.еля 6 или резервного накопителя 8 равна шестнадцати восьмиразрядным информационным словам. В ячейках накопителя 6 возможнь, например, отказы кратности 1:4. Следовательно, необходимо резервировать четыре разряда для каждой ячейки всех накопителей 6. Очевидно, что в данном примере для резервирования двух накопителей 6 указанной емкости достаточно использовать один накопитель 8 такой же емкости. В первой половине всех ячеек накопителя 8 будут находиться резервные разряды одноименных ячеек первого накопителя 6, а во второй половине всех ячеек накопителя 8 - резервные разряды одноименных ячеек второго накопителя 6. Основные регистры слова 11 соединены с соответствующими блоками 12 обнаружения отказов накопителей 6. Выходы регистров 11 подключены непосредственно к одним входам соответствующих блоков 13 поразрядного контроля и через вспомогательные регистры слова 14 - к другим входам блоков 13, выходы блоков 13 связаны через соответствующие элементы И 15 с регистрами 11. Входы буферных регистров слова 16 соединены непосредственно с выходами дешифратора 10 и через соответствующие элементы ИЛИ 17 первой группы - с выходами регистров 11 и с выходным регистром слова 18, имеющим вход 19 и выход 20. Выходы регистров 16 связаны непосредственно с регистрами И и через элементы ИЛИ второй группы 21 - с регистром. 18. Выходы регистров 16 подключены через элементы ИЛИ третьей группы. 22, сдвиговый регистр 23 и коммутатор 24 ко входу резервного регистра слова 25 накопителя 8. Регистр 25 соединен с буферным резервным регистром слова 26 накопителя 8. Выход регистрй 25 подключен через ком.мутатор 27, сдвиговый регистр 28, соответствующие элементы ИЛИ 17 ковходам регистров 16. Управляющие входы регистров сдвига 23 и 28 подключены к выходам дещифратора 10 и через элементы ИЛИ четвертой

группы 29 - к выходам блоков 13. Управляющие входы коммутаторов 24 и 27 связаны с выходами дeuJифpaтopa 10 и через элементы ИЛИ 29 - с выходами блоков 13. Блок управления 30, имеющий вход 31 и выход 32, под ключей к регистру 1, регистрам 5, регистру 9, дешифратору 10, регистрам 11, блокам 12, блокам 13, регистрам 14, элементам И 15, регистрам 16, регистру 18, регистрам 23 и 28, коммутаторам 24 и 27, регистру 25 и регисто рам 7 и 26.

Предложенное резервированное ЗУ работает следующим образом.

По входу 4 поступает адрес ячейки, который записывается в регистр Г, причем .младИ1ие разряды адреса записываются в регистр 3, 5 а старщие разряды адреса - в регистр 2. По содержимому регистра 3 через дешифратор 10 выбирается накопитель 6, к которому будет происходить обращение. Пре.шоложи.м, что обращение производится к первому накопителю 6. 0 Принцип работы одинаков при обращении к любо.му из накопителей 6.

Итак, при обращении к накопителю 6 содержимое регистра 2 поступает на регистр 7 и на регистр 5 накопителя 6, а на регистр 16 поступает слово с регистра 18 через элемен5 ты или 17 (при записи) или ничего не поступает (при чтении). При обращении к накопителю 6 всегда производится предварительное чтение, а затем запись любого нового слова, либо считанного слова (для восстановления). Q Предварительно чтение производится для определения того, является ли ячейка исправной или отказавщей. Блок 12 в регистре 11 анализирует специальный индикаторный разряд (или группу разрядов), указывающих на наличие или отсутствие отказов в ячейке, и выдает соответствующий сигнал в блок 30. Установка индикаторных разрядов в соответствующее состояние может осуществляться, например, предварительно при контроле исправности ячеек. При обнаружении отказавшей ячейки адрес из регистра 7 поступает в регистр 9 и считывается содержимое соответствующей ячейки накопителя 8 на регистр 25.

При записи в исправную ячейку накопителя 6 записываемое слово с регистра 16 посту-, пает на регистр 11 и далее в накопитель 6, 5 а при чтении из исправной ячейки считанное слово поступает с регистра 11 в накопитель 6 (для восстановления) и через элементы ИЛИ 17 регистр 16, элементы ИЛИ 21 - на регистр 18. Запись слова в отказавшую ячейку накопителя 6 происходит следующим образом.

Блок 12 определяет по индикаторному разряду предварительно считанного содержимого ячейки, что ячейка отказала. При этом прямой код слова, считанного на регистр 11, передается на регистр 14, а обратный. код его записывается в ту же ячейку накопителя 6 и считывается на тот же регистр 11. Затем происходит выдача слов из регистров И и 14 в блок 13. Блок 13 по совпадению прямого . и обратного кодов одноименных разрядов определяет отказавшие разряды и разрешает выдачу из регистра 16 в регистр 11 только тех

разрядов слова, которые соответствуют исправным разрядам ячейки накопителя 6. Разряды регистра 16, которые соответствуют отказавшим разрядам ячейки накопителя 6, по сигиалам из блока 13 (через элементы ИЛИ 29) и но сигналам от дешифратора 10 передаются через регистр 23 в коммутатор 24. Коммутатор 24 по сигналам от депн|фратора 10 и от блока 13 (через элементы ИЛИ 29) записывает эти разряды на нужную позицию в регистре 25, т. е. в те разряды, которые являются резервными для данного накопителя 6. После этого производится запись слова из регистра 11 в ячейку накопителя 6 по адресу, записанному в регистре 5, и запись слова из регистра 25 в ячейку накопителя 8 по адресу, записанному в регистре 9.

Чтение слова из отказавшей ячейки накопителя 6 происходит следуюш,им образом.

Блок 12 определяет по индикаторному разряду предварительно считанного содержимого ячейки, что ячейка отказала. Ири этом пря.мой код слова, считанного на регистр И, передается на регистр 14. а обратный его код записывается в ту же ячейку накопителя 6 и считывается на тот же регистр 11. Далее происходит выдача слов из регистра 11 и из регистра 14 в блок 13. Блок 13 по совпадению прямого и обратного кодов одноименных разрядов определяет отказавшие разряды и разрешает выдачу в обратно.м коде из регистра 11 через элементы ИЛИ 17 в регистр 16 только тех разрядов слова, которые соответствуют исправным разрядам ячейки накопителя 6. Выдача отказавших разрядов из регистра 11 блокируется. Слово, считанное из ячейки накопителя 8 на регистр 25, поступает в коммутатор 27. Ко.ммутатор 27 по сигналам от дешифратора 10 и от блока 13 (через элементы ИЛИ 29) передает на регистр 28 те разряды, которые являются резервными для данного накопителя 6. Регистр 28 по сигналам от дешифратора 10 и от блока 13 (через элементы ИЛИ 29) выдает резервные разряды через элементы ИЛИ 17 вместо отказавших разрядов в регистр 16. В результате в регистре 16 находится правильное слово. После этого происходит восстановление информации: слово из регистра 1 1 в обратном коде записывается в ячейку накопителя 6 по адресу, указанному в регистре 5, а слово из регистра 25 записывается в ячейку накопителя 8 по адресу, записанному в регистре 9.

Таким образом, предложенное резервированное ЗУ обеспечивает достоверное воспроизведение информации при наличии отказов в ячейках основных накопителей, используя для нескольких основных ячеек одну резервную. Это намного экономичнее по сравнению с резервированием основных ячеек таким же количеством резервных ячеек, так как необходимое число резервных ячеек и)и этом С1 ижа1|ся.

Форму,la изобретения

Резервированное запоминающее устройство, содержашее основные и резервные накопители, подключенные соответственно к основным и резервным регистра.м адреса н регистрам с.юва, регистр номера ячейки, подключенный к основным регистра.м адреса и буферному резервному регистру адреса, соединенному с резервны.м регнстро.м адреса, регистр номера накопителя, подключенный через дешифратор к основным накопителям, блоки обнаружения отказов, соединенные с основными регистрами слова, вспомогательные регистры- слова, входы которых подключены к выходам основных регистров слова, блоки поразрядного контроля, одни входы которых соединены с выходами вспомогательных регистров слова, другие входы - с выходами основных регистров слова, а выходы блоков поразрядного контроля подключены через элементы И ко входам основных регистров слова, коммутаторы, регистры сдвига, выход одного из которых через соответствуюпшй коммутатор подключен ко входу резервного регистра CvioBa, выход которого через соответствуюший коммутатор- соединен со входом другого регистра сдвига, группы элементов ИЛИ, выходной регистр слова, соединенный с блоком управления, отличающееся тем, что, с целью упрощения и повышения эффективной емкости, оно содержит буферный резервный регистр слова, соединенный с резервным регистром слова, .и буферные регистры слова, входы которых подключены соответственно к выходам элементов ИЛИ первой группы и дешифратора, а выходы - непосредственно ко входам основных регистров слова и через элементы ИЛИ второй и третьей группы соответственно - ко входам выходного регистра слова и одного из регистров сдвига,

О первые входы элементов ИЛИ первой группы подключены к выходам другого регистра сдвига, вторые входы - к выходам выходного регистра слова, третьи входы - к выхода.м основных регистров слова, выходы блоков поразрядного контроля через элементы ИЛИ четвертой группы соединены с одними управляющими входами коммутаторов и регистров сдвига, другие управляющие входы которых подключены к выходам дешифратора.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР .У 385319, кл. G И С 29/00, 1972.

2.Патент США № 3544477, кл. 340- 172.5. 1970.

ИтК

a-i

r

(WJff

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1975 |

|

SU619966A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

Авторы

Даты

1978-04-25—Публикация

1976-01-16—Подача