1

Изобретение относится к области запоминающих устройств (ЗУ).

Известно ЗУ, содержащее накопитель, адресные входы которого подключены к блоку управления, а разрядные выходы и входы- к регистру и через первый блок схем «ИЛИ - к блоку кодирования соответственно, блок декодирования, один из входов которого подсоединен к выходу второго блока схем «ИЛИ, блоки схем «И, схему сравнения.

Недостатком известного ЗУ является то, что в нем при увеличении эффективной емкости снижается устойчивость памяти к отказам в ячейках накопителя и, наоборот, при повышении устойчивости памяти к отказам в ячейках накопителя уменьшается эффективная емкость.

Предложенное ЗУ отличается от известного тем, что оно содержит схему определения кратности отказа, вход которой подключен к одному из выходов блока декодирования, а выход - к одному из входов схемы сравнения, регистр силы корректирующего кода, вход которого подсоединен к выходу схемы сравнения, а выход - к другим входам блока декодирования, схемы сравнения и входу блока кодирования, триггер, входы которого подсоединены к другому выходу блока декодирования, к выходу блока управления соответственно, а выходы - к управляющим входам блоков схем «И, информационные входы которых подключены к выходам регистра, а выходы- ко входам второго блока схем «ИЛИ.

Эти отличия позволяют повысить надежность работы и увеличить эффективную емкость устройства.

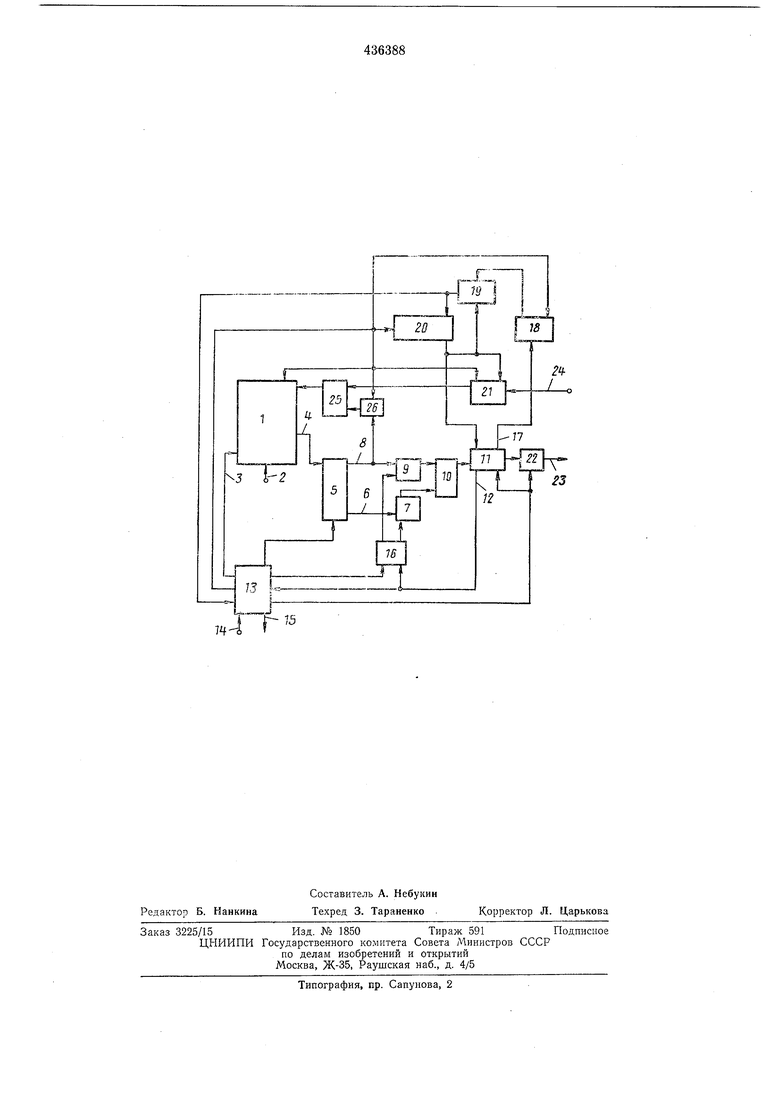

На чертеже изобрал ена блок-схема предложенного ЗУ.

ЗУ содержит накопитель 1 с информационным входом 2 и управляющим входом 3. Разрядный выход 4 -накопителя соединен со входом регистра 5. Прямой выход 6 регистра 5 через блок схем «И 7, а инверсный выход 8 регистра 5 через блок схем «И 9 связаны со входами блока схем «ИЛИ 10, выход которого соединен с кодовым входом блока декодирования И. Управляющий выход 12 блока 11 связан с блоком управления (БУ) 13, имеющим вход 14 и выход 15, и со входом установки, например, в «1 триггера 16. Соответственно выход «О триггера соединен с управляющим входом блока схем «И 7, а выход «1 триггера - с управляющим входом блока схем «И 9. Управляющий выход 17 блока декодирования 11 связан со входом схемы 18 определения кратности отказа, выход которой соединен с одним из входов схемы сравнения 19. Выход схемы 19 связан с

блоком управления 13 и со входом регистра «ИЛИ 20 корректирующего кода, выход которого соединен с другим входом схемы сравнения 19 и с управляющими входами блока Пи блока кодирования 21. Информационный выход блока 11 связан через блок схем «И 22 с информационным выходом 23 устройства. Информационный вход 24 устройства соединен с информационным входом блока кодирования 21. Кодовый выход последнего связан с одним входом блока схем «ИЛИ 25, с другим входом которого через блок схем «И 26 соединен инверсный выход 8 регистра 5, а выход блока 25 связан с разрядным входом наконителя 1. Накопитель, регистры 5, 20, блоки 11 и 21, вход установки в «О триггера 16, схема 18, управляющие входы блоков 22, 26 соединены с БУ 13.

Предложенное ЗУ работает следующим образом.

Регистр 20 корректирующего кода, управляющий блоками 11 и 21, настраивается путем записи в него соответствующего слова на код, сила которого определяется максимальной кратностью имеющих место в ячейках наконителя 1 отказов (под силой п корректирующего кода подразумевается его способность обнаруживать ошибки кратности от 1 до я включительно). Настройка регистра 20 происходит следующим образом.

В начале работы устройства, когда отказы в ячейках накопителя 1 отсутствуют, регистр 20 настраивается на код, исправляющая способность которого равна, например, k. По мере накопления в ячейках накопителя возникающих в разные моменты времени отказов кратности, например, s (s), кратность имеющих место в некоторых из этих ячеек отказов может достигнуть величины k. При этом сила используемого корректирующего кода с помощью регистра 20 устанавливается равной + s при той же исправляющей способности, равной k. В случае обнаружения в какой-нибудь ячейке накопителя 1 отказа кратности {k + s}, что возможно, когда в ячейке, содержащей й-кратный отказ, произойдет отказ кратности S, регистр 20 перестраивается на код с силой (k+2s), затем при обнаружении отказа кратности (k + Qs) -на код с силой (k + 3s) и так до (). Исправляющая способность корректирующего кода все время остается постоянной н равной k.

В исходном состоянии триггер 16 сигналом с блока управления 13 устанавливается в«О. На вход 2 накопителя подается адрес ячейки накопителя, к которой необходимо обратиться.

При записи информационное слово по входу 24 поступает в блок кодирования 21, с выхода которого кодовое слово через блок схем «ИЛИ 25 записывается в накопитель 1.

При считывании кодовое слово из накопителя 1 поступает в регистр 5, а с прямого выхода 6 регистра 5 через блок схем «И 7 и блок схем «ИЛИ 10 - в блок 11. Блок 11 декодирует кодовое слово, определяет наличие

или отсутствие неисправимой ошибки в нем, выдавая в соответствии с этим по управляющему выходу 12 сигнал в БУ 13 и управляя триггером 16, а также определяет кратность имеющей место ошибки (исправимой или неисправимой), информация о чем поступает по управляющему выходу 17 в схему 18 (в качестве последней может быть использован, например, накапливающий сумматор).

Если неисправимая ошибка отсутствует, триггер 16 остается в состоянии «О. Информационное слово с выхода блока 11 через блок схем «И 22 поступает на выход 23. При наличии неисправимой ощибки триггер

16 сигналом с управляющего выхода 12 блока И устанавливается в «1, подключая инверсный выход 8 регистра 5. При этом информационное слово на выход 23 не поступает, а обратный код содержащегося в регистре 5

кодового слова с инверсного выхода 8 через блоки 26 и 25 записывается в ту же ячейку накопителя 1. Далее производится считывание записанного в накопитель кодового слова и запись его в регистр 5. Обратный код нового содержимого регистра 5 поступает с инверсного выхода 8 через блок схем «И 9 и блок схем «ИЛИ 10 в блок 11. Блок 11 декодирует кодовое слово, выдавая через блок 22 на выход 23 правильное информационное слово,

и определяет кратность возможно имеющей место (исправимой) ошибки, информация о которой поступает по управляющему выходу 17 в схему 18 и суммируется с прежним содержимым этой схемы.

По окончании считывания (как при наличии, так и при отсутствии неисправимой ошибки) содержимое схемы 18, представляющее собой величину кратности имеющего место в ячейке накопителя 1 отказа, сравнивается схемой 19 с содержимым регистра 20.

Если схема 19 определит равенство крагности имеющего место отказа и силы используемого кода, вся информация из накопителя 1 выводится, схема сравнения 19 обеспечивает

перестройку регистра 20 и блоков 11 и 21 на код, сила которого на s единиц выше силы прежнего используемого кода, далее осуществляется ввод информации в накопитель 1. Если кратность отказа будет не равна

(меньще) силы используемого кода, указанные операции: вывод информации из накопителя 1, перестройка регистра 20 и блоков 11 и 21, ввод информации в накопитель - не производятся, и устройство продолжает использовать код прежней силы.

Для иллюстрации работы предложенного ЗУ рассмотрим пример.

Предположим, ЗУ использует код, исправляющий одиночную ошибку, например код

Хэмминга. Пусть в некоторую ячейку накопителя 1 было записано кодовое слово 01001010... (многоточием обозначены контрольные разряды), а в результате имеющего место в ней одиночного отказа кодовое слово,

считываемое на регистр 5, имеет вид

11001010... (в подчеркнутом разряде произошло искажепие информации, вызвавшее возникновение одиночной ои 1ибки, обнаруживаемой и исправляемой корректирующим кодом). Одиночная ошибка будет исправлена и на выходе 23 получим правильное информационное слово 01001010, а схема 19 обеспечит перестройку регистра 20 на код, исправляющий одиночную и обнаруживающий двойную ошибку, например код Хэмминга.

Пусть в той же ячейке накопителя 1 в результате возникновения еще одного одиночного отказа содержится двойной отказ, а кодовое слово, считываемое на регистр 5, имеет вид 11101010... (в подчеркнутых разрядах произошло искажение информации, вызвавшее возникновение двойной ошибки, обнаруживаемой, по пе исправляемой корректирующим кодом). Блок 11, обнаружив двойную ошибку, устанавливает триггер 16 в «1 и выдает в схему 18 информацию о двойной ошибке. Затем осуществляется запись в ту же ячейку накопителя 1 обратного кода содержимого регистра 5 и последующее его считывание на этот же регистр. В результате в регистре будет записап код 10110101... В блок И поступает обратный код нового содержимого регистра 5, т. е. 01001010..., ошибка в котором отсутствует, и, следовательно, на выходе 23 будет получено правильпое информационное слово 01001010. Схема 19 обеспечит перестройку регистра 20 на код, исправляющий одиночную и обнаруживающий тройную ошибку.

Пусть в той же ячейке накопителя 1 в результате возникновения еще одного одиночного отказа содержится тройной отказ, а кодовое слово, считываемое на регистр 5, имеет вид 11111010... (в подчеркнутых разрядах произошло искажение информации, вызвавшее возникновение тройной ошибки, обнаруживаемой, но не исправляемой корректирующим кодом). После обпаружения блоком 11 тройной ошибки при исправлении ее по мере преобразования информации получаем коды, аналогичные полученным при двойном отказе. Кроме того, возможен случай, когда при тройном отказе имеет место двойная ошибка, например при записи в рассматриваемую ячейку накопителя 1 кодового слова 01011010... Кодовое слово, содержащееся в ячейке накопителя и считываемое на регистр 5, будет иметь вид 11111010... (искажение информации произошло только в двух старших отказавших разрядах, что вызвало возникновение двойной ошибки). Блок 11, обнаружив двойную ошибку, устанавливает триггер 16 в «1 и выдает в схему 18 информацию о двойной ошибке. Затем осуществляется запись в ту же ячейку накопителя 1 обратного кода содержимого регистра 5 и последующее его считывание на этот же регистр. В результате в

регистре 5 записан код 10110101... В блок 11 поступает обратный код нового содержимого регистра 5, т. е. 01001010..., в котором имеет место одиночная ошибка, исправляемая блоком 11, и, следовательно, на выходе 23 получим правильное информационное слово 01011010. Информация об одиночной ошибке поступит из блока 11 в схему 18 и просуммируется с содерж ащейся в этой схеме

информацией о двойной ошибке, в результате чего в схеме 18 будет находиться информация об имеющем место в ячейке накопителя 1 тройном отказе. Таким образом, предложенное ЗУ позволяет, используя коды, исправляющие ошибки кратности 1-k и обнаруживающие ошибки кратности (k+, (k+) - (), (+1) - (2Й-Ы), исправлять ошибки кратности соответственно 1 - (k ), 1 - ( + 2), ....

1 - (), что дает возможность увеличить эффективную емкость, обеспечивая ту же устойчивость памяти к отказам в ячейках накопителя, что и коды, исправляющие ошибки кратности соответственно 1 - (fe+ 1), 1 - (-f2),

. . ., 1 - (2Й+1). В то же время, сохранив эффективную емкость, которая имела место при использовании кодов, исправляющих ошибки кратности 1 -(-Ы), 1 -(fe + 2), . . ., 1 -(2/г+ + 1), можпо, применяя коды, исправляющие

и обнаруживающие ошибки за счет того, что они обладают меньшей информационной избыточностью, повысить устойчивость памяти к отказам в ячейках накопителя.

35

Предмет изобретения

Запоминающее устройство, содержащее накопитель, адресные входы которого подключены к блоку управления, а разрядные входы

и выходы - к регистру и через первый блок схем «ИЛП - к блоку кодирования соответственно, блок декодирования, один из входов которого подсоединен к выходу второго блока схем «ИЛИ, блоки схем «И, схему сравнения, отличающееся тем, что, с целью повышения надежности работы и увеличения эффективной емкости устройства, оно содерЛСит схему определения кратности отказа, вход которой подключен к одному из выходов

блока декодирования, а выход - к одному из входов схемы сравнения, регистр силы корректирующего кода, вход которого подсоединен к выходу схемы сравнения, а выход - к другим входам блока декодирования, схемы

сравнения и входу блока кодирования, триггер, входы которого подсоединены к другому выходу блока декодирования и выходу блока управления соответственно, а выходы - к управляющим входам блоков схемы «И, информационные входы которых подключены к выходам регистра, а выходы - ко входам второго блока схем «ИЛИ.

ih- 1

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1973 |

|

SU452037A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU444250A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 1971 |

|

SU429424A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

Авторы

Даты

1974-07-15—Публикация

1973-02-09—Подача