1

Изобретение относится к области вычислительной техники и может быть использовано .при работе цифровых вычислительных компдегКсов в системах управления и моделирования :различных процессов, требующих обеспечения .вычислений в большом диапазоне из.менения точности.

Известн© интегрирующее устройство, содер;жащее блок экстраполяции и квантования, : выход и первый вход которого соединены соIответственно с первыми выходом и входом хустрййства, два сумматора, первый регистр частичных сумм, узел .формирования приращения, первые два входа которого подключены ко второму и третьему входам устройства, регистр приращения, вход которого подключен к третьему входу устройства, .а выход соединен с первым входом первого сумматора, преобразователь кода, два входа которого подключены соответственно к выходу узла формирования приращения и четвертому входу устройства, а выход соединен с первым входом второго сумматора, первый регистр подынтегральной функции, первые вход и выход которого подключены соответственно к третьему входу и второму выходу устройства, первый элемент «И, первый вход которого подключен к пятому входу устройства, а выход соединен с первым входом первого элеjMeHTH «ИЛИ, второй вход которого подключен к выходу второго элемента «И, два входа которого подключены соответственно к выходу первого сумматора и щестому входу устройства, третий элемент «И, входы которого

подключены к выходу второго сумматора и седьмому входу устройства, а выход соединен со вторым входом блока экстраполяции и квантования, четвертый элемент «И, входы которого подключены к выходу второго сумматора и восьмому входу устройства, а выход соединен с входом первого регистра частичных сумм.

В известном устройстве для обеспечения требуемого диапазона точности вычислений

формат регистров интегрирующего устройства выбирается, исходя из верхнего предела точности. При этом при выполнении вычислений с более низкой точностью время выполнения операций интегрирования, определяемое длительностыо вычислений при наибольшем количестве разрядов, оказывается завышенным. Целью изобретения является увеличение быстродействия и расширения класса решаемых задач.

Поставленная цель достигается тем, что устройство содержит второй регистр частичных сумм, второй регистр подынтегральной функции, первый вход и выход которого подключены к третьему входу и второму выходу устройства, первый и второй дополнительные

элементы «И, первые входы которых подключены соответственно к выходам первого и второго регистров подынтегральной функции, а вторые входы подключены соответственно к девятому и десятому входам устройства, первый дополнительный элемент «ИЛИ, входы которого подключены к выходам первого и второго дополнительных элементов «И, а выход соединен со вторым входом первого сумматора, третьим входом узла формирования приращения н вторым входом первого элемента «И, третий и четвертый дополнительные элементы «И, первые входы которых подключены соответственно к девятому и десятому входам устройства, вторые входы соединены с выходом первого элемента «ИЛИ, а выходы подключены соответственно ко вторым входам первого и второго регистров подынтегральной функции, пятый и шестой дополнительные элементы «И, первые входы которых подключены соответственно к выходам первого и второго регистров частичных сумм, вторые входы подключены к одиннадцатому входу устройства, выход пятого элемента «И соединен со входом второго регистра частичных сумм, седьмой дополнительный элемент «И, два входа которого подключены соответственно к выходу первого регистра частичных сумм и к двенадцатому входу устройства, второй дополнительный элемент «ИЛИ, два входа которого иодключепы соответственно к выходам шестого и седьмого дополнительных элементов «И, а выход соединен со вторым входом второго сумматора.

При этом формат регистров интегрирующего устройства и ячеек запоминающего устройства выбирается, исходя из разрядности чисел при короткой разрядной сетке, а для обеспечения вычислений над числами, имеющими удвоенную разрядную сетку, хранение информации в запоминающем устройстве осуществляется в двух ячейках.

Примененне предлагаемого устройства позволяет сократить время выполнения операций нитегрирования и оборудования запоминающего устройства при короткой разрядной сетке п обеспечить возмол ность выполнений вычислений над числами, имеющими короткую и задвоенную разрядную сетку.

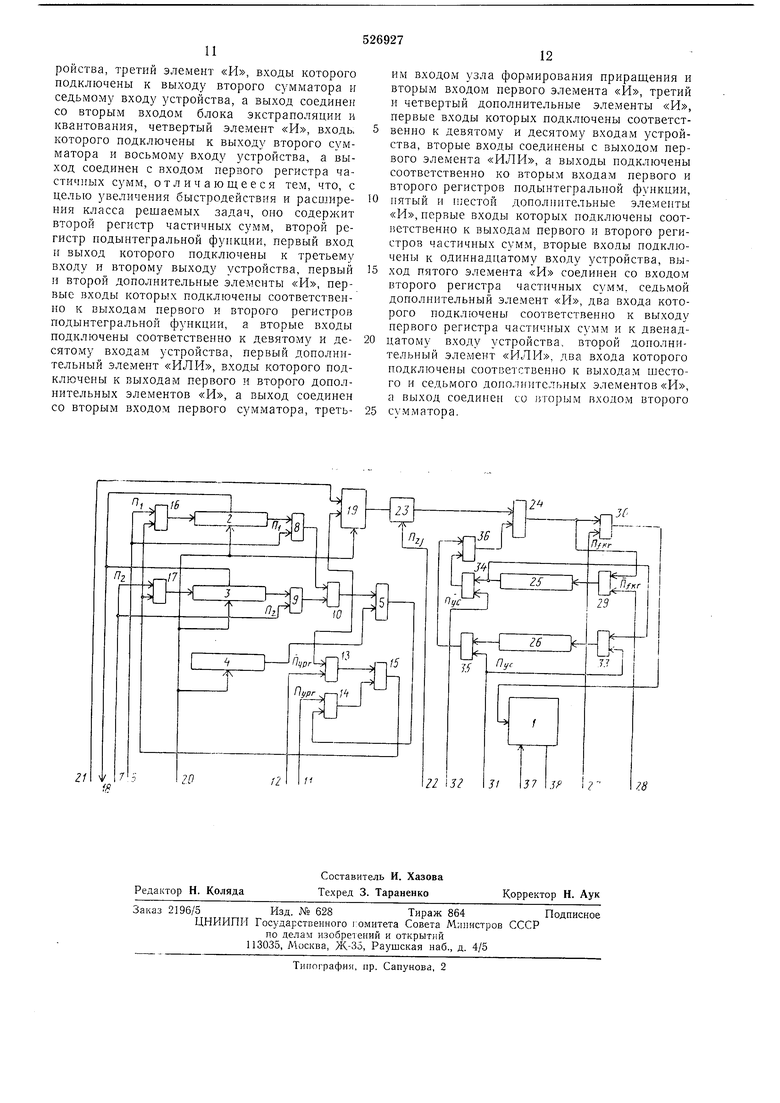

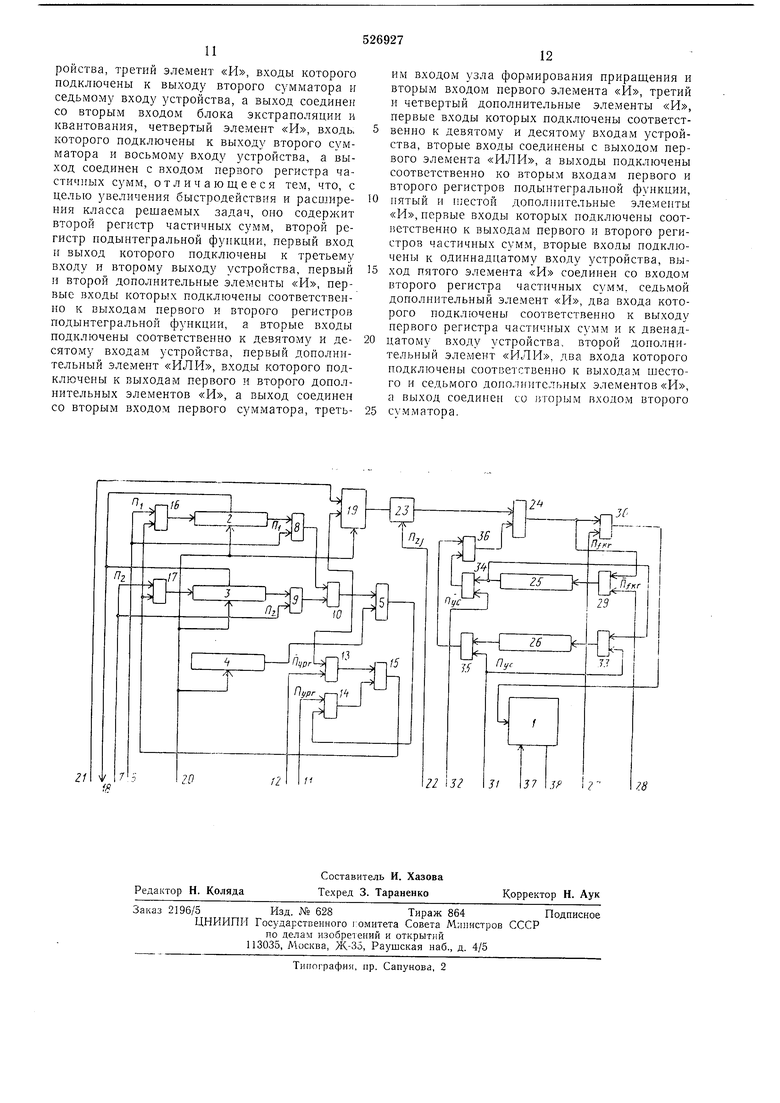

На чертеже представлена блок-схема интегрирующего устройства цифровой интегрирующей мащины последовательного типа.

Интегрирующее устройство (ИУ) содержит блок 1 экстраполяции и квантования; первый регистр 2 подынтегральной функции при короткой разрядной сетке или младших разрядов подынтегральной функции при удвоенной разрядной сетке; второй регистр 3 подынтегральной функции для хранения старших разрядов при удвоенной разрядной сетке; регистр 4 приращения подынтегральной функции; первый двухвходовый сумматор 5 для формирования новых значений ординат подынтегральной функции; девятый вход 6, по которому в ИУ из устройства управления (УУ)

поступает признак Пь имеющий единичное значение в режиме вычислений с короткой разрядной сеткой и и при прохождении младших разрядов подынтегральной функции при удвоенной разрядной сетке; десятый вход 7, по которому в ИУ из УУ поступает признак И2, имеющий единичное значение в режиме вычислений с удвоенной разрядной сеткой при прохождении старших разрядов подынтегральной функции; первый дополнительный элемент «И 8, обеспечивающий прохождение подынтегральной функции с выхода первого регистра 2 подынтегральной функции при наличии признака П, второй дополнительный элемент

«И 9, обеспечивающий прохождение подынтегральной функции с выхода второго регистра 3 подынтегральной функции при наличии признака Па; первый дополнительный элемент «ИЛИ 10, обеспечивающий прохождение подынтегральной функции в режимах короткой и удвоенной разрядной сетки на вход первого сумматора 5; шестой вход 11, по которому в ИУ из УУ поступает признак Пург формирования нового значения подынтегральной функции; пятый вход 12, по которому в ИУ из УУ поступает инверсия признака Tlypr формирования нового значения подынтегральной функции; первый элемент «И 13, предназначенный для переписи в первый и

второй регистры 2, 3 подынтегральной функции неизменного значения подынтегральной функции при отсутствии признака Пург, второй элемент «И 14, обеспечивающий прохождение в первый и второй регистры 2, 3

подынтегральной функции нового значения подынтегральной функции при наличии признака Пур,.; первый элемент «ИЛИ 15, управляющий прохождением нового или неизменного значений подынтегральной функции;

третий дополнительный элемент «И 16, пропускающий при наличии признака Yli в первый регистр 2 подынтегральной функции подынтегральную функцию при короткой разрядной сетке или ее младщие разряды при

удвоенной разрядной сетке; четвертый дополнительный элемент «И 17, пропускающий при наличии признака Ylz во второй регистр 3 подынтегральной функции старшие разряды подынтегральной функции при удвоенной

разрядной сетке; второй выход 18, по которому из первого и второго регистров 2, 3 ИУ в запоминающее устройство (ЗУ) поступает новое или неизменное значение нодынтегральной функции; узел формирования приращения интеграла 19; третий вход 20, по которому из блока хранения подынтегральной функции ЗУ поступают приращения подынтегральной функции и подынтегральная функция, вычисленная в предыдущем шаге интегрирования, в

регистры 2, 3, 4 п узел формирования нрнращения интеграла 19; второй вход 21, по которому в узел формирования приращ,ения интеграла 19 из блока хранения переменной интегрирования ЗУ поступают прираш,ения переменной интегрирования; четвертый вход 22,

по которому в ИУ из УУ поступает признак инверсии знака приращения интеграла П,;; преобразователь кода 23, обеспечивающий инверсию знака приращения интеграла при налнчии признака Пг;; второй дву.хвходовый сумматор 24 для формирования частичных сумм неквантованных приращений интегралов; первый регистр 25 частичных сумм неквантованных приращений интегралов при короткой разрядной сетке или старигпх разрядов частичных сумм при удвоенной разрядной сетке; второй регистр 26 частичных сумм для младщих разрядов частичных сумм некваятованных приращений интегралов при удвоенной разрядной сетке; седьмой вход 27, по которому в ИУ из УУ поступает признак окончания формирования переменной И1 тегрирования Пг7,г; восьмой вход 28, по которому в ИУ из УУ поступает инверсия признака окончания формирования переменной литегрирования П/;,г; четвертый элемент «И 29, с помощью которого осуществлгется стирание частичной суммы нриращеипй чнтегралш р. попвом и втором регистрах 25, 26 частичных су,мм по признаку n/ftr окончания формирования прираиений на выходе сумматора 24; третий элемент «И 30, иредна,зна енный для пропускания неквантованного прираш,ения переменной с выхода второго сумматора 24 в блок 1 для экстраполяции и квантования; олиннадпатый вход 31, по которому в ИУ из УУ поступает призиак режима пычнслений с удвоенной разрядной сеткой П-.-г; лпенадиатЕ п вход 32, но которому в ИУ из УУ поступает инверсия признака режи,ма вычнслер)ий с удвоенной разрядной сеткой ГТу,:; пятый дополнительный элемент 33, замыкающий выход первого регистра 25 частичных сумм па вход второго регистра 26 части-пых сумм в режиме вычислений с удвоенной разрядной сеткой (); седьмой дополните,тьпый элемент «И 34, обеспечивающий ппохождение частичных сумм неквантованных прпрлщений интегоа,лов при короткой разрядной сетке (П ); щестой дополнительный элемен г «И 35, обеспечивающий прохождение частичных сумм неквантованных приращений интегралов в режиме вычислений с удвосипой разрядиой сеткой; второй дополнительный элемент «ИЛИ 36, обеспечивающий прохождение частичных сумм неквантовапных приращений интегралов на вход второго сумматора 24; первый вход 37, по которому в блок 1 ИУ из блока хранения квантованных значений приращений и остатков ЗУ поступают приращения переменной и остаток, полученный при квантовании приращения переменной в предыдущем интегрировании; первый выход 38, по которому из блока 1 экстраполяции и кваитовання ИУ в блок храненгя кзантотяаиных значений приращений и остатков ЗУ поступают квантованные и экстраполированные прирап;ет пя и новый остаток квантования.

В предлагаемом интегрирующем устройстве алгоритм функционирования может быть представлен в внде;

П.., еслир,

(/---1)

АУ

ЛК

)

, если р k

П

РГ

дг , если , если f/

15

(f-7) „ (г-7). ДГ ДГ

ДК

(f-a)

7 а-1)

П,, ДГ

а 0, 1,..., т-1; Y,i Пус + ( Yin + Ylri} П,, -f

25

30

35

40

n.A-. + +

, т-т rr ) . ы 1 + Ufkrliy f D -дj7 - -ду-

-П +

OK

ft a-I)

- 1 j ДУh ДК J.,

ДГ

50

П D- rZllILJl L 1 .

+ n,.,VДК + ДЗ L

„.V,U-.)

y5j

.z

ДГ

где Прг, Ид,- - коммутационные признаки выбгфки приращений переменных Ур и У,, в Ком интегрировании;

(i+i - значенне подынтегральной функции Ург в точке (),

Ург(-г) - значеиия младщих N разрядов подыитегральной функции в точке ();

7

(i+i) - значения старших N-j-1 разрядов подынтегральной функции в точке (i+l);

Л - разрядность подынтегральной функции в режиме короткой разрядной сетки без учета знака;

(4i) 9ггг+о

- квантованные нриДГ

ДК

ращения подынтегральной функции и переменной интегрирования соответственно в точке (i+1); ДУ - квант подынтегральной функции;

par (i + 1)

---неквантованное приращение интеграла, вычисленного в г-ом интегрировании в точке (г+1);

V5t,r (г+1)

;L -частичная суммма неквантоДК

ванных приращений интегралов в точке (); )-неквантованное приращение

переменной У/; в точке (i+1); (/41)

-многоразрядное квантованДГ

ное приращение неременной УЬ в точке (/+1);

or.

k (ill)

-остаток квантования пеДГременной УЛ в точке (t+1);

п - количество разрядов приращений в режиме короткой разрядной сетки;

fhr - формула численного интегрирования по Стилтьесу;

V k (М 2)

- квантованное экстранолидк

рованное приращение неременной УН в точке (i+2);

- постоянные коэффициенты, входящие в формулу экстраноляции приращений.

В первом сумматоре 5 вычисляются новые

значения подынтегральных функций Угр(г+1). В узле формирования приращений интегралов 19 по заданной формуле численного интегрирования но Стилтьесу fkr вычисляются приращения интеграла.

({ + 1)

которые при отсутствии приДГ

знака Ягг проходят без изменения через преобразователь кода 23, а при наличии /7zj знак

ri

приращений .( инвертируется в преобразователе кода 23. Во втором сумматоре 24 вычисленное приращение интеграла

(1 + 1)

ДК

суммируется с полученной рапее частичной суммой неквантованных приращений интегралов

VSort

дГ

В блоке 1 осуществляется вычис.тение экстраполированных значений приращений

(r + 2)

квантованных приращении

АК

OY ()

k(i-,i)

остатка

ДК

Суммирование приращений интегралов поеле интегрирования позволит упростить структуру блока суммирования приращений но сравнению со структурой блока суммирования на входе интегратора. Одновременно повыщается точность вычислений и упрощается программа рещения.

Рассмотрим вычислительный процесс выполнения одной операции интегрирования в (t-|-l)-ом щаге рещения.

Выполнение онерации начинается после поступления из запоминающего устройства по

V pr{/M)

третьему входу 20 приращения

ДГ

vi-.

В регистр приращений 4, P-(-c;-i) |Q,QJ

..., m-1)

в узел формирования приращений интеграла 19, подынтегральной функции Ургг при короткой разрядной сетке или младших разрядов подынтегральной функции Ургг при удвоенной разрядной сетке в первый регистр 2 подынтегральной функции, старщих разрядов подынтегральной функции Ургг Цри удвоенной разрядной сетке во второй регистр 3 подынтегральной функции, по второму входу 21 приращений

УПГ

ЧГ(1-г1--) (

(, 1,..., те -1)

ДГ

в узле формирования приращений интеграла 19. Кроме того, при выполнении экстраполяции и квантования по первому входу 37 в блок 1 экстраполяции и квантования из запоминающего устройства поступает остаток

и приращения ill ((-у,о,1 ...,

).

После занесения в интегрирующее устройство необходимой для начала вычислений информации значение ординаты при короткой разрядной сетке или младщие разряды ординаты при удвоенной разрядной сетке при наличии признака П на девятом входе 6 через первый дополнительный элемент «И 8 и первый дополнительный элемент «ИЛИ 10 поступают па второй вход первого сумматора 5 с выхода первого регистра 2 подынтегральной

функции. Старшие разряды ординаты при вычислениях с удвоенной разрядной сеткой поступают на второй вход первого сумматора 5 с выхода второго регистра 3 подынтегральной функции при наличии признака П2 на десятом входе 7 через второй дополнительный элемент «И 9, первый дополнительный элемент «ИЛИ 10. Одновременно на первый вход первого сумматора 5 поступает приращение (fTl) из регистра приращения 4. С выхода первого сумматора 5 новое значение подынтегральной функции направляется в узел формирования приращения интеграла 19 и при наличии признака формирования нового значения подынтегральной функции Пург на шестом входе 11 записывается в первый регистр 2 подынтегральной функции через второй элемент «И 14,первый элемент «ИЛИ 15, третий дополнительный элемент «И 16 при наличии признака HI на девятом входе 6 или во второй регистр 3 подынтегральной функции через второй элемент «И 14, первый элемент «ИЛИ 15,четвертый дополнительный элемент «И 17 при наличии признака Пз на десятом входе 7. В случае наличия инверсии признака Пург на пятом входе 12 неизменные разряды подынтегральной функции с выхода первого дополнительного элемента «ИЛИ 10 переписываются в первый регистр 2 подынтегральной функции через первый элемент «И 13, первый элемент «ИЛИ 15 и третий дополнительный элемент «И 16 при наличии признака П на девятом входе 6 или во второй регистр 3 подынтегральной функции через первый элемент «И 13, первый элемент «ИЛИ 15, четвертый дополнительный элемент «И 17 при наличии признака П2 на десятом входе 7. Полученное на выходе узла формирования приращения интеграла 19 приращение 5одг{г-(1) умножается в преобразователе кода 23 на коэффициент (-1) i , и величина )(t4 1) .(-1) с выхода последнего направляется на первый вход второго сумматора 24, складывается с накопленной в предыдущих операциях суммой неквантованных приращений интегралов, поступающей на второй вход второго сумматора 24 с выхода первого регистра 25 частичных сумм при наличии инверсии признака удвоенной разрядной сетПус на двенадцатом входе 32 через седьмой дополнительный элемент «И 34, второй дополнительный элемент «ИЛИ 36 или с выхода второго регистра 26 частичных сумм при наличии признака удвоенной разрядной сетки Пус на одиннадцатом входе 31 через шестой донолнительный элемент «И 35, второй дополнительный элемент «ИЛИ 36,. При вычислениях в режиме удвоенной разрядной сетки () содержимое первого регистра 25 частичных сумм через пятый дополнительный элемент «И 33 переписывается во второй регистр 26 частичных сумм. При наличии инверсии признака окончания формирования переменной интегрирования на восьмом входе 28 сумма выхода второго сумматора 24 через четвертый элемент «И 29 проходит в первый регистр 25 частичных сумм, а через него и пятый дополнительный элемент «И 33 при удвоенной разрядной сетке {Пус 1) во второй регистр 26 частичных сумм и запоминается до следующей операции интегрирования. При наличии признака П/лг окончания формирования переменной интегрирования на седьмом входе 27 величина с выхода второго сумматора 24 через третий логический элемент «И 30 поступает в блок 1 экстраполяции и квантования. После окончания вычислений со второго выхода 18 в ЗУ заносятся значения Ург; при П,, или Ур,-(+1) при Пцр,. 1, поступающие с выходов первого и второго регистров 2 и 3 подынтегральной функции, значения при П/;, И V}fe( 5) :постуиающие в ЗУ приращение из блока 1 экстраполяп.ии и квантования с первого выхода 38. После результатов операции из ЗУ выбирается информация, необходимая для вы.полнения следующей операции интегрирования. Выполнение этой операции аналогично предыдущей. Ф о р м у л а и 3 о о р е т е и и я Интегрируюи,1ее устройство интегрирующей машины последовательного типа, содержащее блок экстраполяции и квантования, выход и первый вход которого соединены соответственно с первыми выхо.з,ом и входом стройства, два сумматора, первый регистр частичных сумм, узел формирования приращения, нервые два входа которого подключены ко второму и третьему входам устройства, регистр приращения, вход которого подключен к третьему входу устройства, а выход соединен с первым входом первого сумматора, преобразователь кода, два входа которого подключены соответственно к выходу узла формирования приращения и четвертому входу устройства, а выход соединен с первым входом второго сумматора, первый регистр подынтегральной функции, первые вход и выход которого подключены соответственно к третьему входу и второму выхо.чу устройства, первый элемент «И, первый вход которого подключен к пятому входу устройства, а выход соединен с первым входом первого элемента «ИЛИ, второй вход которого подключен к выходу второго элемента «И, два входа которого подключены соответственно к выходу первого сумматора и шестому входу устройства, третий элемент «И, входы которого подключены к выходу второго сумматора и седьмому входу устройства, а выход соединен со вторым входом блока экстраполяции и квантования, четвертый элемент «И, входь. которого подключены к выходу второго сумматора и восьмому входу устройства, а выход соединен с входом первого регистра частичных сумм, отличающееся тем, что, с целью увеличения быстродействия и расоирепия класса решаемых задач, оно содержит второй регистр частичных сумм, второй регистр подынтегральной функции, первый вход и выход которого подключены к третьему входу и второму выходу устройства, первый и второй дополнительные элементы «И, первые входы которых подключены соответственно к выходам первого и второго регистров подынтегральной функции, а вторые входы подключены соответственно к девятому и десятому входам устройства, первый дополнительный элемент «ИЛИ, входы которого подключены к выходам первого и второго дополнительных элементов «И, а выход соединен со вторым входом первого сумматора, третьим входом узла формирования приращения и вторым входом первого элемента «И, третий и четвертый дополнительные элементы «И, первые входы которых подключены соответственно к девятому и десятому входам устройства, вторые входы соединены с выходом первого элемента «ИЛИ, а выходы подключены соответственно ко вторым входам первого и второго регистров подынтегральной функции, иятый н шестой дополнительные элементы «И, первые входы которых подключены соответственно к выходам первого и второго регистров частичных сумм, вторые входы подкл очены к одиннадцатому входу устройства, выход пятого элемента «И соединен со входом второго регистра частичных сумм, седьмой дополнительный элемент «И, два входа которого подключены соответственно к выходу нервого регистра частичных сумм и к двеиадцатому входу устройства, второй дополнительный элемент «ИЛИ, два входа которого подключены соответственно к выходам шестого н седьмого дополн1ггельных элементов «И, а выход соединен со вторым входом второго сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

-{ti

. I

Авторы

Даты

1976-08-30—Публикация

1974-04-15—Подача