С54) ЦИФРОВОЙ даФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1971 |

|

SU294157A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1973 |

|

SU387395A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Цифровой генератор развертки | 1979 |

|

SU834685A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для вычисления тригонометрических функций синуса и косинуса | 1976 |

|

SU616633A1 |

| Анализатор спектра | 1984 |

|

SU1237987A1 |

| Цифровой вычислитель синуса и косинуса | 1977 |

|

SU682905A1 |

| Частотный преобразователь | 1980 |

|

SU884131A1 |

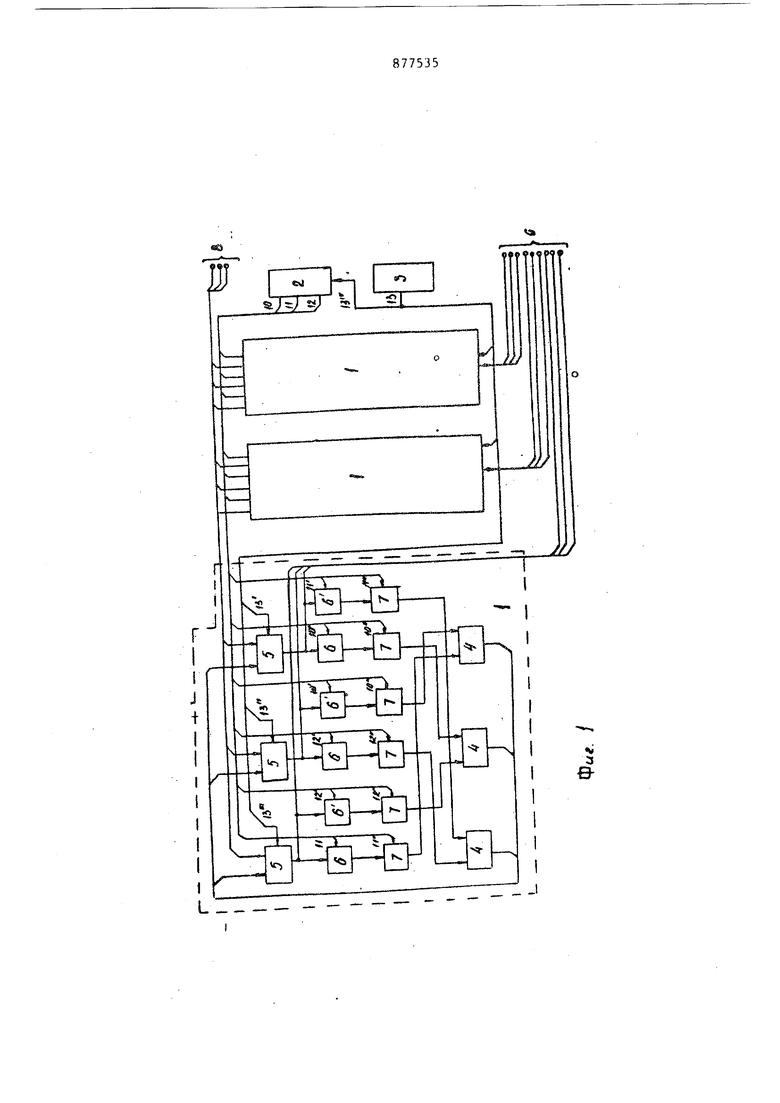

Изобретение относится к BbWHcnH.тельной технике и может быть использовано в навигационной аппаратуре для вычисления направляющих косицусоз, Известен цифровой дифференциальный анализатор СЦЦА) для вычисления направляющих косинусов, содержащий запоминающие ячейки, блоки ввода текущей информации, комбинационные суммат ры, коммутаторы, преобразователи кодов и блоки управления, наборные поля жестко соединены между собой. Указанное устройство характеризуется недостаточной точностью и быстродействием вследствие большого, шага интегрирования, так как направляющие косинусы вычисляются последовательно Наиболее близким по технической сущности к предлагаемому является ВДА, который имеет запоминающие ячейки, подключенные к блоку управления, Первые выходы запоминающих ячеек подкпкмены непосредственно и через преобразователь кодов к соответствующим коммутаторам, а вторые выходы - к первьм входам выходных сумматоров, вторые входы которых соединены с соответствующими комбинационными суммато рами, а выходы - с запоминающими ячейками и шинами вьшода результата 2 J. Известный ЦЦА характеризуется недостаточной точностью вследствие большого шага интегрирования, кроме того, при умножении направлямцего косинуса на приращение независимой переменной не учитывают знак направляющего косинуса , что может привести к неправильному вычислению приращения направляющего косинуса. Цель изобретения - повьшение быстродействия и точности устройства. Поставленная цель дoJ:тигaeтcя тем, что в цифровой дифференциальный анализатор, содержащий блок ввода и распределитель импульсов, при этом выход распределителя импульсов подключен ко входу блока ввода, введены три вычислительных бдока, при этом каждый из/ 3 них содержи ; Ipynny 11реобраг1оиателей прямого кода лополнительны, накапливающие сумматоры, комбинационные сумматоры, две группы коммутаторов, причем первые входы накапливающих сум маторов подключены к выхохам соответствукщих комбинационных сумматоров, первый вход каждого из которых подключен к выходу соответствующих коммутаторов первой группы, вторые входы комбинационных сумматоров подключены к выходам соответствующих ком мутаторов первой группы, первый вход каждого коммутатора соединен с первым входом соответствующего преобразователя прямого кода в дополнительный всех вычислительных блоков, и через шину ввода текущей информации подклю чены к выходам блока ввода, вторые вх ды первого и второго, третьего и четвертого, пятого и шестого преобразова телей прямого кода в дополнительный попарно объединены и подключены к вхо ной шине ввода исходной информации, выход каждого накапливающего сумматора подключен соответственно ко входам первого, третьего и пятого преобразователей прямого кода в дополнительный выходы преобразователей прямого кода в дополнительный подключены к входам соответствующих коммутаторов, вторые входы накапливающих сумматоров всех вычислительных блоков через шину пере дачи управляющей информации подключе ны к выходу распределителя импульсов третьи входы накапливающих сумматоров являются группой входов исходной информации устройства, выходы накаплива кщих сумматоров всех вычислительных блоков являются группой информационных выходов анализатора. Выходы комбинационных блоков соеди нены с первыми входами коммутаторов, вторые входы которых соединены с числ выми разрядами шин ввода текущей информации. Коммутаторы осуществляют пропуск направляющего косинуса на соответствующий комбинационный сумматор если приращение текущей информации равно 1, и не пропускает, если оно равно 0. На фиг. 1 приведена структурная схема устройства; на. фиг. 2 - структурная схема комбинационного блока ЦДЛ. Устройство содержит вычислительный блок 1, блок 2 ввода, блок 3 синх ронизации, комбинационные сумматоры 4, накапливающие сумматоры 5, пре34образователи 6 и 6 прямого кода в дополнительный, коммутаторы 7, щины 8 ввода исходной информации, шины 9 вывода результата решения задачи, ши- ны 10-12 ввода текущей информации, знаковые разряды щин ввода текущей информации, шины 13 передачи управляющей информации, шины 13 передачи управляющей информации на накапливающие сумматоры 5, шины 13 передачи управляющей информации на блок ввода текущей информации 2 , преобразователь 14 кода, элементы НЕ 15 и 16, элементы И 17 и 18, элемент ИЛИ 19 числовые разряды 20 направляющего косинуса, знаковые разряды 20 направляющего косинуса. Вычисление направляющих косинусов производится одновременно в трех однотипкых вычислительных блоках. Приращение независимой переменной поступает в вьиислительные блоки по шинам 1012 от блока 2 ввода текущей информации, который осуществляет преобразование непрерывной величины независимой переменной в цифровой код и выделение приращения этой величины. Накапливающие сумматоры 5 предназначены для об разования новых значений направляющих косинусов, хранения их в течение шага интегрирования и выдачи их по сигналу блока управления. Преобразователи 6 и 6 предназначены для преобразования прямого кода направляющего косинуса в дополнительный. Причем преобразователи 6 осуществляют это преобразование, если знак направляющего косинуса и знак приращения независимой переменной отличается друг от друга, а блоки 6 - наоборот, когда знаки совпадают. Управление преобразователями кода осуществляется груп - пой элементов И, ИЛИ, НЕ, которые анализируют знаки сомножителей. Так, если знаки совпадают, то в блоках 6 на входе ZQ преобразователя кода устанавливается О, а на входе ZQ- I , в блоке б , наоборот, на ZQ- 1 , а на ZQ-O, и наоборот, если знаки не совпадают, Блок 3 управления предназначен для управления вводом информации из бло - ка 2 ввода текущей информации по шинам 13 передачи управляющей информации, работой накапливающих сумматоров 5 и выдачей результатов вычисле НИИ из вычислительных блоков 1 по щинам 13 -13 . Основная функция блока 3 управления заключается в выработке синхронизирующих управляющих сиг5палин i подачи их но тикам 1J переда чи упранлиюшей ииформзш(Н. Устройство работает с чедующим образом. Перед шагом интегрирования по сигналу, поступающему из блока управления на вход блока ввода текущей информации, на шинах 10-12 устанавливаются до конца шага интегрирова - НИН новые значения приращений независиной переменной, причем на шине 10 устанавливается Ф, на шине 1 1 на шике 1 2 -ufa. Эти шины соединены с соответствующими входами комбинационных блоков и коммутаторов образом, что на комбинационных блоках устанавливается знак п JИpaщeний неза висимых переменных, а на входах коммутаторов их численные значения. По сигналу с блока 3 управления по даваемые по шинам 13-13 направляюище кос}1нусы с накапливающего сумматора 5 подаются на вход вычислительного блока и на входы преобразователей 6 и 6 , через которые они, в зависимости от своего знака и знака не зависимой переменной, проходят либо прямым, либо дополнительным кодом на коммутаторы 7, через которые они про ходят на вход соответствующего комби нациоуиюго сумматора 4, если прираще ние независимой переменной равно I, и не проходят, если оно равно 0. На комбинационн1 1х сумматорах 4 в соответствии с алгоритмом образуется приращение направляюи|;их .косинусов, которые поступают на входы накаплива щих ciMMaTopoB 5 и, складываясь со старыми значениями направляющих коси нусов, образуют новые значения. После этого блок 3 управления выдает управлмющий сигнал на образование -новых приращени) независимой переменной бло ком 2. После этого процесс интегрировани повторяется. Таким образом в предлагаемом ЦЦА быстродействие увеличивается в 3V1 раз где И- разрядность кода, по сравнению с известным. Увеличение точности при этом можн оценить следующим образом.. Максимальную погрешность метода можно определить как тш- t где К - число iiiaroii интегрирования; :.6 & - величина приращения иапраиляюшего косинуса; ut- величина шага интегрирования, Следовательно, отношение f v,v l/A-tNa jvix -( - j VMQXt Y характеризует увеличение точности в ЗИраз. Кроме того, неучет знака направляющего косинуса в известном устройстве может привести к значительной погрешности что устраняется в предлагаемом устройстве. Формула изобретения Цифровой дифференциальный анализатор, содержащий блок ввода н распредетитель импульсов, при этом выход расаределителя импульсов подключен ко входу блока ввода, отличающий с я тем, что, с целью повышения быстродействия и точности, в него введены три вычислительных блока, при этом из них содержит группу преобразователей прямого кода в дополнительный, накапливающие сумматоры, комбинационные сумматоры, две группы коммутаторов, причем первые входы накапливающих сумматоров подключены к вы ходам соответствующих комбинационных сумматоров, первый вход каждого нз которых подключен к вьсходу соответствуюш x коммутаторов первой группы, вторые входы комбинационных сумматоров подключены к выходам соответствующих коммутаторов первой группы, первый вход каждого коммутатора соединен с первым входом соответствующего преобразователя прямого кода в дополнительный всех вычислительных блоковой через шину ввода текущей информации подключены к вь ходам блока ввода, вторые входы первого и второго, третьего ичетвертого, пятого и шестого преобразователей прямого кода в дополнительный попарно объединены и подключены к входной шине ввода исходной информации, выход каждого накапливающего сумматора подключен соответственно ко входам первого, третьего и пятого преобразователей прямого кода в дополнительный выходы преобразователей прямого кода в дополнительный подключены к входам соответствующих коммутаторов, вторые входы накапливающих с -1маторов всех вычислительных блоков

через шину передачи управляющей информации подключены к выходу распределителя импульсов, третьи входы накапли- . вающих сумматоров являются группой входов исходной информации устройства, выходы накашшваюпщх сумматоров всех вычислительных блоков являются группой информационных выходов анализатора..

Источники информации, принятые во внимание при экспертизе

тотип).

«а

Г

77

&

Ч)

J

г

J i

(

М/

N

3

еL1

Авторы

Даты

1981-10-30—Публикация

1979-12-25—Подача