1

Изобретение относится к области вычислительной техники и может использоваться для создания мультивибраторов, генераторов последовательности импульсов, триггеров с несколькими устойчивыми состояниями, динамических счетчиков на МДП-структурах (металл-диэлектрик-полупроводник).

Известны инверторы на МДП-транзисторах, содержащие инвертирующий транзистор, затвор которого соединен с входной шиной и затБОром переключающего транзистора пушпульного выходного каскада. В последнем .затвор нагрузочного транзистора подключен к стоку инвертирующего транзистора.

С целью расширения функциональных возможностей инвертора в предлагаемое устройство введен дополнительный транзистор, подключенный затвором к затвору инвертирующего транзистора, а истоком и стоком - соответственно к истоку и затвору нагрузочного транзистора пушпульного выходного каскада.

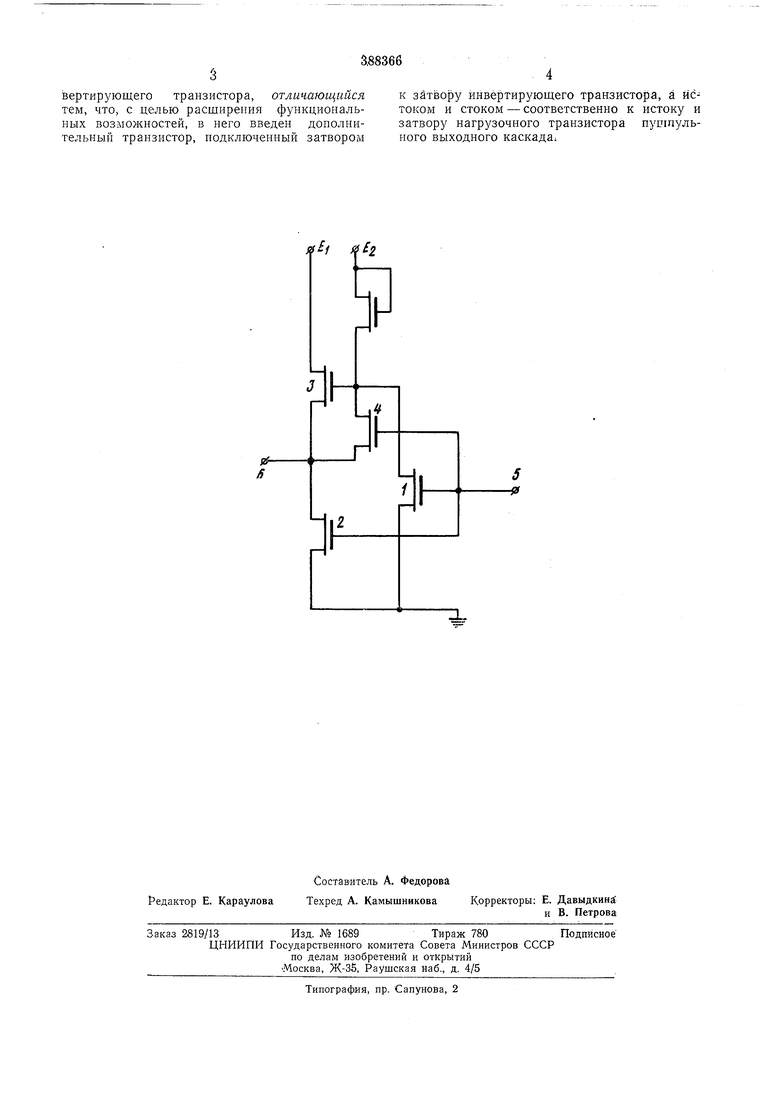

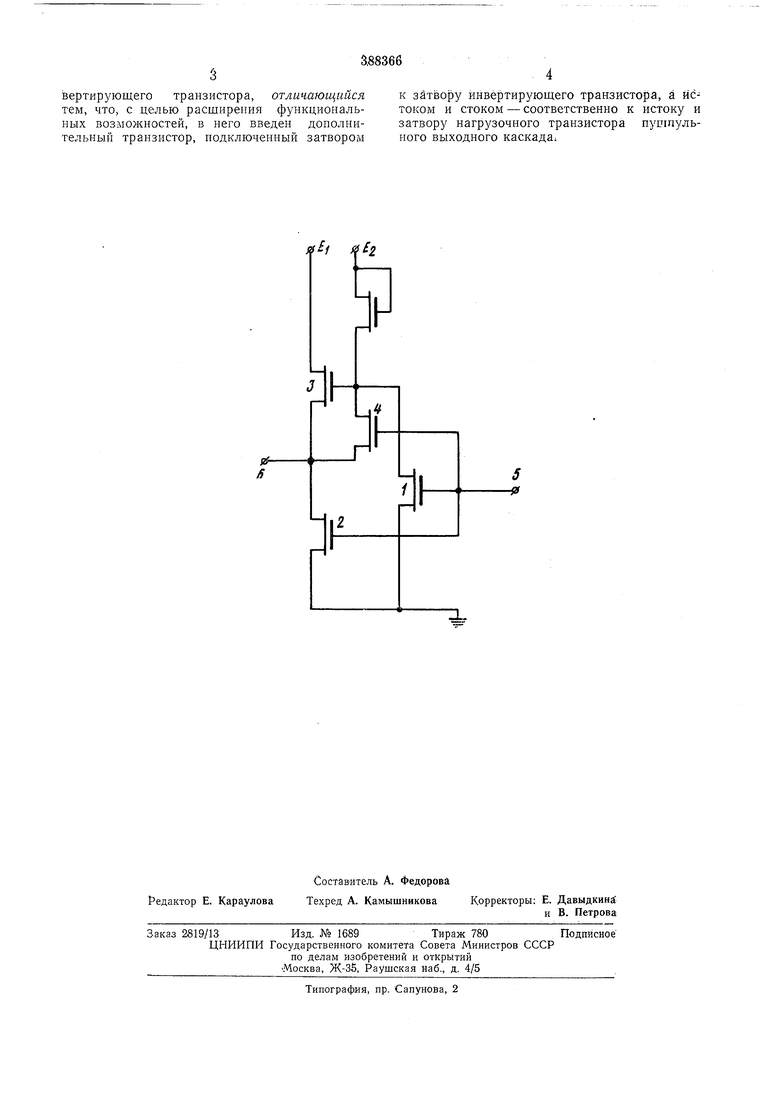

На чертеже представлена схема инвертора на МДП-транзисторах.

Схема содержит инвертирующий транзистор 1, пущиульный выходной каскад, состоящий из переключающего 2 и нагрузочного 3 транзисторов, дополнительный транзистор 4, затвор которого связан с затвором инвертирующего транзистора /, сток подключен к затвору нагрузочного транзистора 3 пушпульного выходного каскада, а исток -к истоку нагрузочного транзистора 3, входную 5 и выходную 6 шины.

Инвертирующий транзистор 1, осуществляя начальное запирание нагрузочного транзистора 3 пущпульного выходного каскада, создает условия включения транзисторов 2 и 4 этим же входным сигналом f/ijx - i и полного запирания транзистора 3 при любом значении напряжения смещения Е.

При напряжении на входе схемы, близком к пороговому, инвертор открыт. Величина тока через транзистор 1 по сравнению с током транзисторов 4 и 2 незначительна, и ею можно пренебречь. При этом малейшее изменение абсолютной величины напряжения на стоке транзистора 2 приводит к полному запиранию транзистора 4 и отпиранию транзистора 3 за счет положительной обратной связи. На выходной шине 6 устанавливается напряжение EI.

Предмет изобретения

Инвертор на МДП-транзисторах, содерн ащий инвертирующий транзистор, затвор которого соединен с входной шиной и затвором переключающего транзистора пущпульного выходного каскада, в котором затвор нагрузочного транзистора подключен к стоку инвертирующего транзистора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен донолнительныр транзистор, нодключенный затвором

к зйтвору инвертирующего транзистора, а истоком и стоком - соответственно к истоку и затвору нагрузочного транзистора пуьчпульного выходного каскада;

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультивибратор на мдп-транзисторах | 1972 |

|

SU440772A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1983 |

|

SU1145467A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Инвертор на МДП-транзисторах | 1982 |

|

SU1128388A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Устройство преобразования уровней напряжения | 1976 |

|

SU558400A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

-(-/ 2

Я

5 -а

Авторы

Даты

1973-01-01—Публикация