четвертого и пятого элементов И, второй вход четвертого элеме-нта li соедииен е четвертым прОМежуточным выходом первой линии задерЖ1КИ, первый гфОмежуточный вход KOTOipoii соединен С четвертой входной шнной, .а нятый промежуточный выход соединен с первым входом шестого элемента И, выход которого подключен к входу элемента задержки, а второй вход соединен со вторым промежуточным входом первой линии задержкн и выходом пятого элемента И, второй вход которого соединен с промежуточным выxoдoiм второй лнннн задержки, иерВый промежуточный вход которой соединен с выходом четвертого элемента И, а второй промежуточный вход подключен к пятой входной шине.

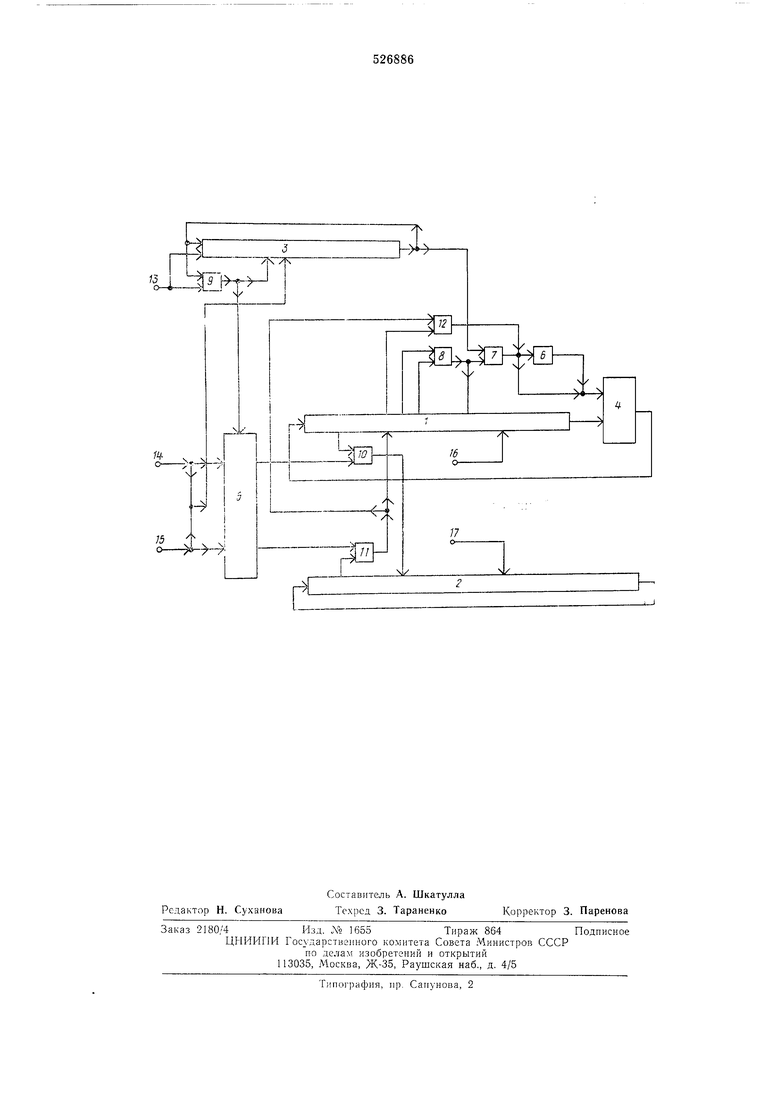

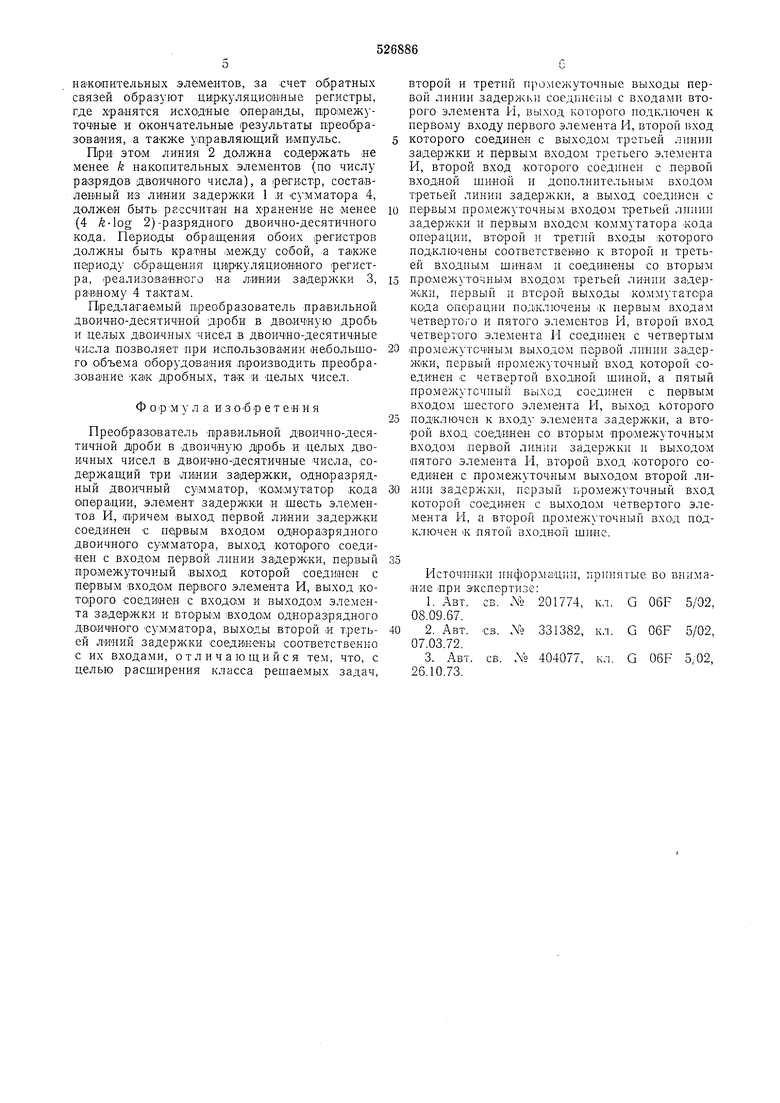

На чертеже ;представле«а бло к- схема преобразователя кодов.

Преобразователь :содержит первую линию задержки 1, вторую линию задержки 2, третью линию задерж ки 3, одноразрядный двоичный сумматор 4, 1коммутатор 5 «ода операции, элемент 6 задержки, первый элемент И 7, второй элемент И 8, третий элемент И 9, четвертый элемент И 10, нятый элемент И 11, шестой элемент И 12, первую входную ниину 13, вторую входную шину 14, третью входную шину 15, четвертую входную шину 16 и пятую входную шину 17.

Преобразование дробных и -целых чисел в устройстве о-суЩбствляется с помощью ,метода сдвига и 1коррекции. В соответствии с этиМ рассмотрим работу у|стройства в двух режимах: 1преобразоваНИе дрОбей и -целых чисел.

Преобразование правильной двоично-десятичной дроби в двоичиую дро.бь. Метод сдвига и «огррекции для это-го -вида -нреоб-разоваяия заключается в том, что мантисса исходной дво ичн-о -десяти и д р о б и -по с л ед о-в а тел bHiO умио-жает-ся иа два (путем сдви-га яа о-дип р-азря-д в стор-о-иу стар1ших ра13ря-до1в) с выделением разрядоВ целой части, фор.М;И1рующих ц-око.мое двоичное число, на-чин-ая со старших раз-рядов. При ЭТ01М те тетрады, которые больше или равны 5, перед сдвигом -кор-ректируются путем .прибавления IK иим 3.

Пр-еобразователь работает следующим образ-ом.

Па линию задержки 1, -о-бразую-щую -е одноразрядным двоичным сумматором 4 циркуляционный регистр, по шине 16 последовательно поступают двоично-десятичные разряды исходной дробн. Одйо-времеппо -по шине 14 в коммутатор 5 ко-да операции и на третью задержки 3, также имеющую обратную связь, поступает вмпульс кода операции, который циркулирует в ней в течение в-сего времени -преобразо-вання, о беепечивая выработку необходимых управляющих импульсов.

Требуемые сдв-иги осуществляются за счет nepecTipoeiHHH управляющего кмпульса в циркуляциони01М регистре и сокра-щення на один такт -периода -его обр-ащения. Это происходит в каждом цикле при поступлении по шине 13 управляющего импульса. В этом случае управляющий импульс, пройдя через элемент i-I 9 и через коммутатор 5, -выделит на элементе 10 очередной ра13ряд целой ча1сти, который перейдет на вторую линию задержки 2. Благодаря наличию обратной связи она образует циркуляцион-ный р-егистр, где и -осуществляется последовательное формирование и Х1ранение искомой двоичной дроби.

К-ор-рекция тетрад выполняется следующим

образом.

Па первом элементе И 7 все тетрады проверяются -на наличие у них разрядов с 1весовы1М коэффициентом р 3 (т. е. тетрады, ра-вные «8 и «9). Элемент И 8 вырабатывает импульсы для тетрад, содержаших числа «5, «6 или «7. Такнм образом, указанные элементы срабатывают во всех случаях, |КОГда зна-чение тетрад не 1меньще 5. При -с -помощью нако-нительного эл-емента 6 вырабатыБается корректирующий 1код ООН (три). Этот код посылается на сумматор 4, где и осуществляется сложение соответствующих тетрад, нуждающих;ся в коррекции:, с кодом коррекции. Этим самым ко.мпенсируется ощибка, которая неизбежна нри -последующем умножении на два дв-оично-десятичных дробей, реализуем-о-м с по-мсщью операции сдвига -на один такт. Преобразование целых двоичных чисел в

двоично-десятичные числа-.

Метод -сдвига и кор.рек-ции для это-го вида преобразования заключается в том, что исходное двоичное число также последовательно умножается на два (путем сдвига iHa один

разряд в сторон}- -ста-рш-их разрядов) с выделением старших разрядов, фор|МИрующих -искомое двоично-десятичное число, начиная со старших разрядов. При этом те тетрады, которые больше или ра.вны 5, также перед сдвигом корректируются путем прибавления IK ним 3.

Работа преаб|р-азователя в это-.м режиме осуществляется следующим образом.

Па линию задержки 2 по шине 17 поступает исходное двоичное число, а по шине 15 - импульс ко-да о-перапии. С элемента 11 импульсами, поступающими с элем-ента 9 через ко.ммутатор 5 кода операции, в каждом цикле с-нимается старщий разряд, который -направляетея для хранвпия в циркуляционный регистр, образованный линией задержки 1 и сумматорОМ 4.

Коррекция -в ра.сематр-иваемом -режиме происходит аналогично режиму преобразования

дробей с той только рав-ницей, что содержимое тетрады, равное 5, опрашивается на элементе И 12.

В обоих рассмотренных режимах полное время преобразования составляет k циклов,

где k - число разрядов двоичного числа.

Каждый из paiccMOTpeBHbix отдельных блоков преобразователя имеет простейщее спроение, требующее 1минималыных аппар-атур-ных затрат. Па-пример, три линии задержки, составленные из последовательно 1соединенных

нзкооительных элементов, за счет обратных связей обр азуют циркуляцисвные регистры, где хранятся исходные олераиды, дромежуточиые и О1ко«чательные результаты преобразования, а та«же управляющий импульс.

При этом линия 2 должНа содержать не менее k накопительных элементов (по числу разрядов двоичного числа), а регистр, составленный из линии задерЖ1КИ: 1 и сумматора 4, должен быть ргсочитан на хранение не менее (4 и-log 2)-разрядного двоично-десятичного кода. Периоды обращения обоих регистров должны быть кратны 1между собой, а та1кже периоду сораще1ния циркуляционного регистра, реализованного на линии задержки 3, равному 4 та.ктам.

Предлагаемый преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа позволяет при использовании небольшого 0 бъема оборудования производить преобразование как дробных, так и целых чисел.

Ф о р м у л а и 3 о б р е т е н и я

Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа, содержащий три линии задержки, одноразрядный двоичный сумматор, жольмутатор кода операции, элемент задержки и шесть элементов И, причем выход первой линии задержки соединен с первым входом одноразрядного двоичного суМ матора, выход которого соединен с входом первой линии задержки, первый промежуточный выход которой соединен с первым входом первого элемента И, выход которого соединен с входом и выходом элемента задержки и вторьгм входо1М одноразрядного двоичного суММатора, выходы второй и третьей линий задержки соединены соответственно с их входами, отличающийся тем, что, с целью расширения класса решаемых задач.

второй и третий промежуточные выходы первой линии задердчкп соединены с входами второго элемента И, выход которого подключен к первому входу первого элемента П, второй вход

которого соединен с выходом третьей линии задержки и первым входом третьего элемента И, второй вход которого соединен с первой входной шиной и дополнительным входом третьей линии задержки, а выход соединен с

первым промежуточным входом третьей линии задержки и первым входом коммутатора кода операции, второй и третий входы iKOTOporo подключены соответственно к второй и третьей входным шина.м и соединены со вторым

про;межуточным входом третьей линии задерЛ4КИ, первый и второй выходы коммутатора кода операции подключены iK первым входам четвертого и пятого элементов И, второй вход четвертого элемента П соединен с четвертым

промежуточным выходом первой линии задержки, первый промежуточный вход которой соединен с четвертой входной шиной, а пятый промежуточный выход соединен с первым входом шестого элемента П, выход которого

подключен к входу элемента задержки, а второй вход соединен со вторым прО межуточным входом первой линии задержки и выходом пятого элемента И, второй вход iKOToporo соединен с промежуточным выходом второй лиНИИ задержки, первый промежуточный вход которой соединен с выходом четвертого элемента И, а второй промелхуточный вход подключен iK пятой ВХОДНО ШИНС.

Источники ииформ.ации, пршгятые во внима1ние при экспертизе:

1. Авт. св. № 201774, кл. G 06F 5/02, 08.09.67.

2. Авт. св. Л1Ь 331382, кл. G 06F 5/02, 07.03.72.

3. Авт. св. Ло 404077, кл. G 06F 5,02, 26.10.73.

Г±:

Авторы

Даты

1976-08-30—Публикация

1974-02-26—Подача