1

Изобретение относится к области автоматики и вычислительной техники и предназначеио для преобразования кодов как правильных и смешанных дробей, так и целых чисел.

Известен преобразователь кодов из двоично-десятичной системы счисления в двоичную, содержащий регистр тетрады, распределитель двоичных разрядов но весам, блок управления, переключатель эквивалентов, блок хранения двоичных эквивалентов десятичных чисел, одноразрядный двоичный сумматор и регистр сдвига.

Предложенное устройство отличается тем, что выход блока хранения двоичных эквивалентов десятичиых чисел соединен со входами линии задержки и первого одноразрядного двоичного сумматора формирователя двоичных эквивалентов десятичных чисел. Выход первого одноразрядного двоичного сумматора соединен со входом второго одноразрядного двоичного сумматора того же формирователя. Входы первого, второго, третьего и четвертого одноразрядных двоичных сумматоров соединены с соответствующими выходами линии задержки того же формирователя. Выходы.линии задержки и всех одноразрядных двоичных сумматоров формирователя двоичных эквивалентов десятичных чисел соединены со входами ключей, вторые входы которых соединены с соответствующими выходами дешифратора. Выходы ключей соединены со входом одноразрядного двоичного сумматора. Это позволяет упростить устройство и повысить его быстродействие.

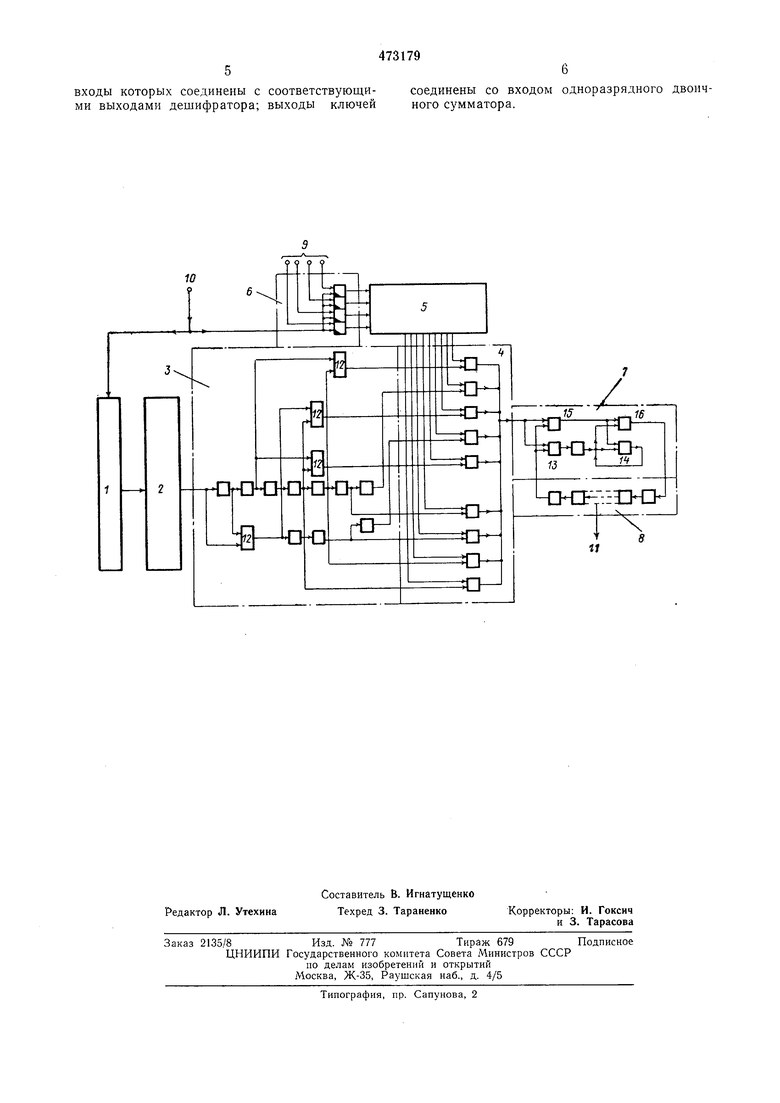

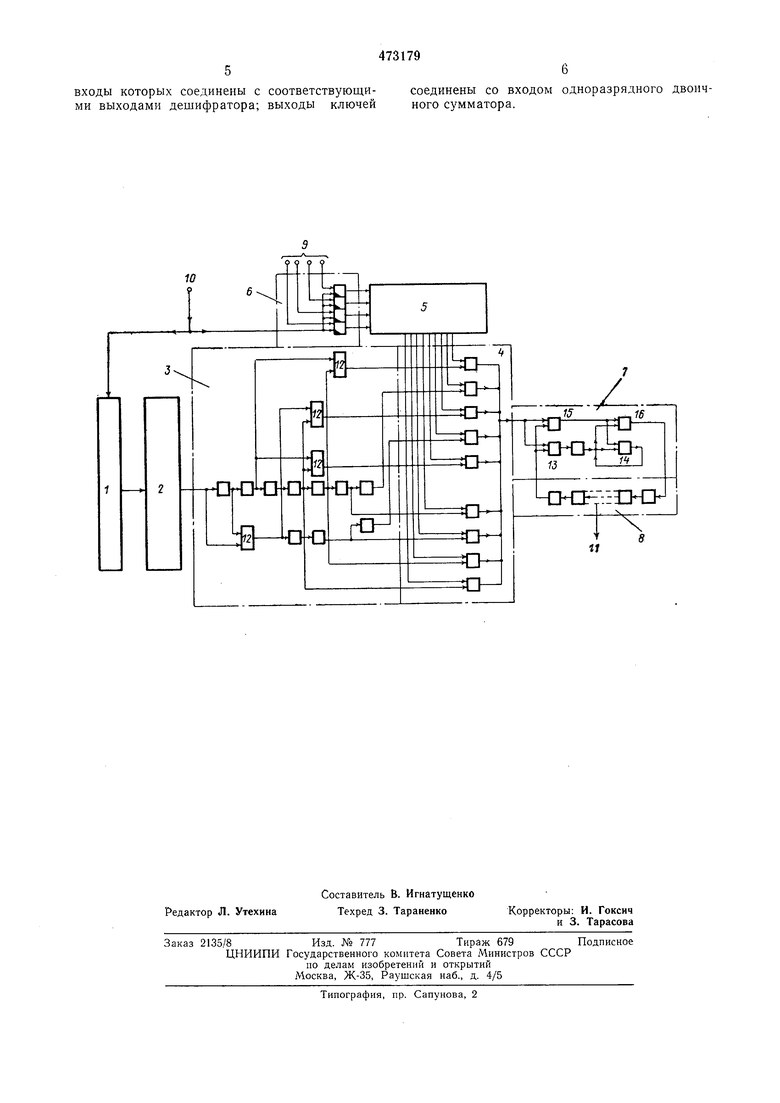

На чертеже изображена схема преобразователя.

Преобразователь содержит переключатель эквивалентов 1; блок хранения 2 двоичных эквивалентов десятичных чисел, содержащий

эквиваленты, вида (10±)э; формирователь 3 двоичных эквивалентов десятичных чисел, вырабатывающийэквивалентывида

(6г-10±)э, имеющий девять выходов по числу десятичных цифр 6,-; ключи 4 по числу десятичных цифр; дешифратор 5 на четыре входа и соответственно на щест1 адцать выходов (из ннх используется девять выходов: &i-bs; регистр тетрады 6, содерл ащпй четыре триггера; одноразрядный двоичный сумматор 7,

регистр сдвига 8, состоящий из накопительных элементов, число которых определяется разрядностью преобразованного двоичного числа; шины 9 иодачи двоично-десятичного разряда и управляющую шипу 10.

Формирователь 3 содержит линию задержки из накопительных элементов и четыре одноразрядных двоичных сумматора 12, схемы которых идентичны схеме сумматора 7. В состав сумматора 7 (и соответственно

сумматоров 12) входят элементы совпадения

13 и 14 и разноименности 15 и 16, а также накопительный элемент.

Преобразование осуществляется с помощью двоичных эквивалентов десятичных чисел в соответствии со следующим выражением:

л- 1&г1о±г,

где Л -искомое двоичное число;

k - номер десятичного разряда; при этом

(k-1); ; 1; О -для целого

числа;

-2; ; - (/г-1); -й-для

правильной дроби;

k k: (k-); ; 1; 0; -1; ....;- (k- 1); - для смещанной дроби;

bi 2; 3; 9 - десятичная цифра;

(di-10±) а -двоичный эквивалент десятичного числа.

Преобразователь работает следующим образом.

По щине 10 с каждым циклом поступает управляющий импульс, осуществляющий сброс триггеров регистра тетрады 6, после чего по щинам 9 поступает двоично-десятичный разряд преобразуемого числа, код которого запоминается на триггерах регистра тетрады 6. Этот код дещифрируется с помощью дещифратора 5, в результате чего на одном из его выходов вырабатываются импульсы, которые подготавливают соответствующий по весу ключ 4. Управляющий импульс для данного разряда k переводит переключатель эквивалентов 1 на считывание из блока 2 двоичного эквивалента (10±)э. Число ячеек блока 2, который в частном случае может быть реализован в виде диодного щифратора, равняется числу преобразуемых десятичных разрядов исходного числа К..

Выбранный двоичный эквивалент (10±)э поступает на вход формирователя 3, с выхода которого снимается полный комплект из девяти эквивалентов для каждого разряда /С. Двоичные эквиваленты (&,-10±)э, у которых bi представляет собой степень числа «2 (т. е. «4 и «8) вырабатываются за счет сдвига исходных эквивалентов (10±)э. Сдвиг на соответствующее число тактов осуществляется с помощью элементов линии задержки формирователя 3 в сторону старших разрядов. Остальные двоичные эквиваленты получаются за счет операций суммирования и сдвигов.

Таким образом, на основе одного эквивалента, хранящегося в блоке 2 (например, десятичного числа «0,1) с помощью формирователя 3 в том же цикле удается получить остальные эквиваленты; «0,2; 0,3; 0,4; 0,5; 0,6; 0,7; 0,8; 0,9. То же самое имеет место и для десятичных чисел «0, «0, «0,0001 и т. д.

В результате этого число циклов преобразования сводится к минимуму, повыщается быстродействие устройства и уменьшаются

аппаратурные затраты. Сформированиые двоичные эквиваленты одновременно поступают на входы соответствующих ключей 4. Однако в каждом цикле подготовленным оказывается лишь один из них в соответствии с кодом тетрады, хранящимся в регистре 6. Поэтому на вход одноразрядного двоичного сумматора 7 поступает только один выбранный эквивалент В. Вместе с регистром сдвига 8 одноразрядный двоичный сумматор 7 образует циркуляционный регистр, служащий .для запоминания кодов.

Вслед за первым десятичным разрядом точно так же за один цикл происходит преобразование следующего и далее любого очередного двоично-десятичного разряда исходного числа. При этом для каждого нового цикла возбуждается соответствующая шина блока 2 и считывается очередной двоичный

эквивалент (10±)э.

Выбранное значение Bi для десятичного разряда К вновь поступает в циркуляционный регистр, где на сумматоре осуществляется сложение с циркулирующим кодом. Так продолжается до тех пор, пока не будут преобразованы все двоично-десятичные разряды исходного числа, и в циркуляционном регистре не сформируется искомое двоичное число, которое снимается с выхода устройства с шины 11.

Предмет изобретения

Универсальный преобразователь двоичнодесятичных чисел в двоичные, содержащий

регистр тетрады и переключатель эквивалентов, входы которых соединены с управляющей щиной, выходы регистра тетрады соединены со входами дешифратора, выходы переключателя эквивалентов соединены со входами

блока хранения двоичных эквивалентов десятичных чисел, одноразрядный двоичный сумматор, выход которого соединен со входом регистра сдвига, выход последнего соединен со входом одноразрядного двоичного сумматора, ключи, формирователь двоичных эквивалентов десятичных чисел, выполненный на одноразрядных двоичных сумматорах и линии задержки, отличающийся тем, что, с целью упрощения устройства и повышения

его быстродействия, выход блока хранения двоичных эквивалентов десятичных чисел соединен со входами линии задержки и первого одноразрядного двоичного сумматора формирователя двоичных эквивалентов десятичных

чисел; выход первого одноразрядного двоичного сумматора соединен со входом второго одноразрядного двоичного сумматора того же формирователя; входы первого, второго, третьего и четвертого одноразрядных двоичных сумматоров соединены с соответствующими выходами линии задержки того же формирователя; выходы линии задержки и всех одноразрядных двоичных сумматоров формирователя двоичных эквивалентов десятичных

чисел соединены со входами ключей, вторые входы которых соединены с соответствующими выходами дешифратора; выходы ключей соединены со входом одноразрядного двончного сумматора.

Авторы

Даты

1975-06-05—Публикация

1973-10-01—Подача