1

Изобретение относится к области цифровой вычислительной техники и предназначено для построения управляющих вычислительных систем.

Известеи парафазиый Д-триггер на МОПтранзисторах с дополнительной симметрией, содержащей инверторы, вентильные МОПтранзисторы и тактирующий и информационный входы триггера.

Однако известный триггер содержит боль пее число транзисторов и имеет двупроводный режим записи информации.

Предлагаемое устройство отличается от известного тем, что нервое гтлечо триггера выполнено на двувходовой схеме , -ко входам которой подключены вентильные транзисторы с дополнительными блокируюишми транзисторами, а второе нлечо триггера вынолнено на инверторе, вход которого непосредственно связан с первым плечом, причем истоки дополнительных блокирующих транзисторов заземлены, исток первого вентильного транзистора соединен со вторым нлечом триггера, стоки и затворы первых вентильного и дополнительного блокирующего транзисторов соединены соответственно с первым входом двувходовой схемы и с истоком второго вентильного транзистора и с тактирующим входом триггера, а стоки и затворы вторых вентильного и дополнительного

блокирующего транзисторов соединены соответственно со вторым входом двувходовой схемы и с информационным входом триггера.

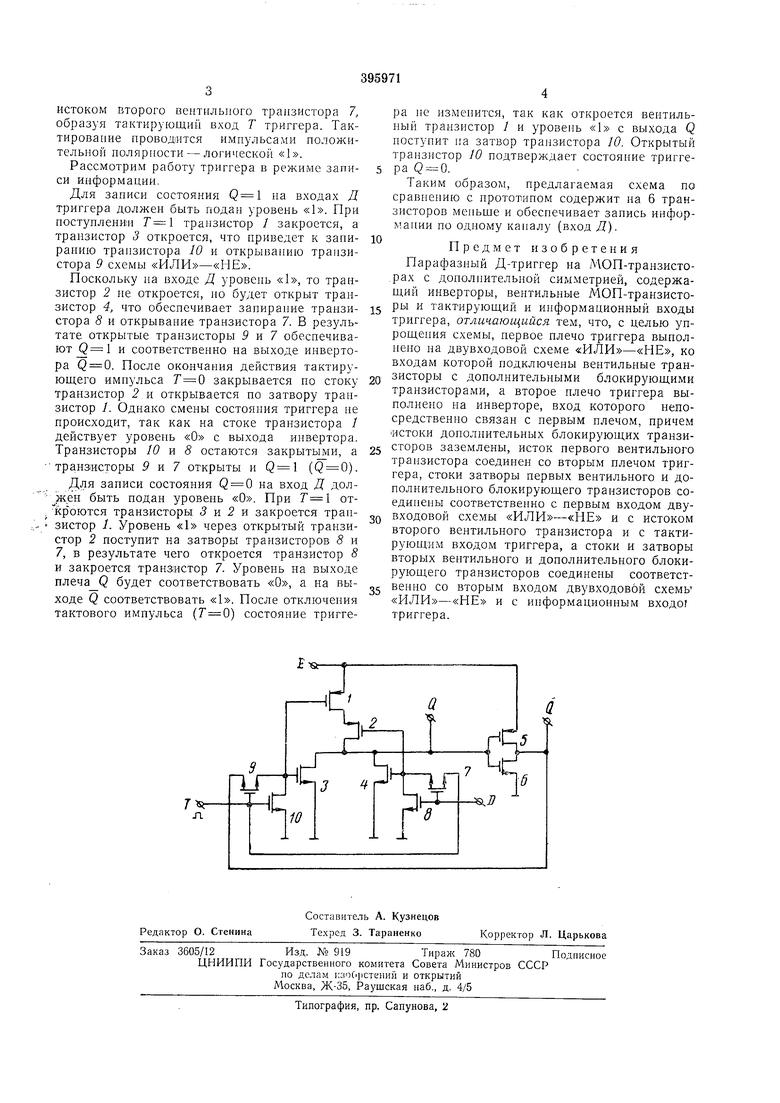

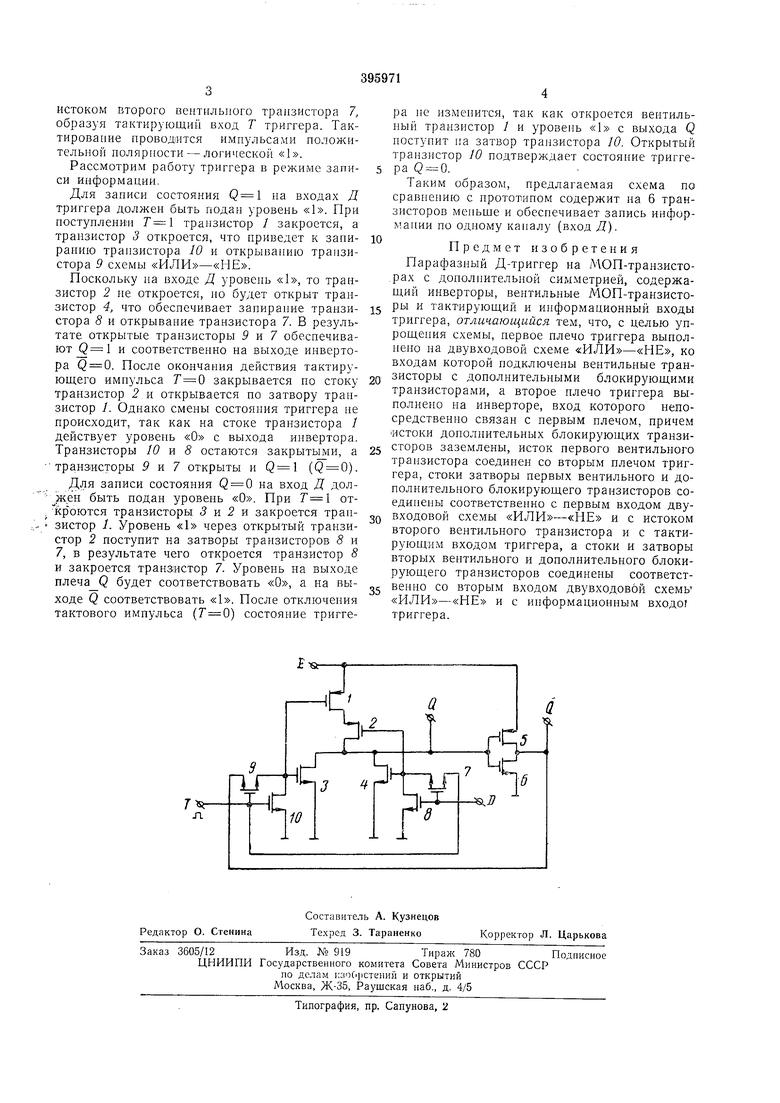

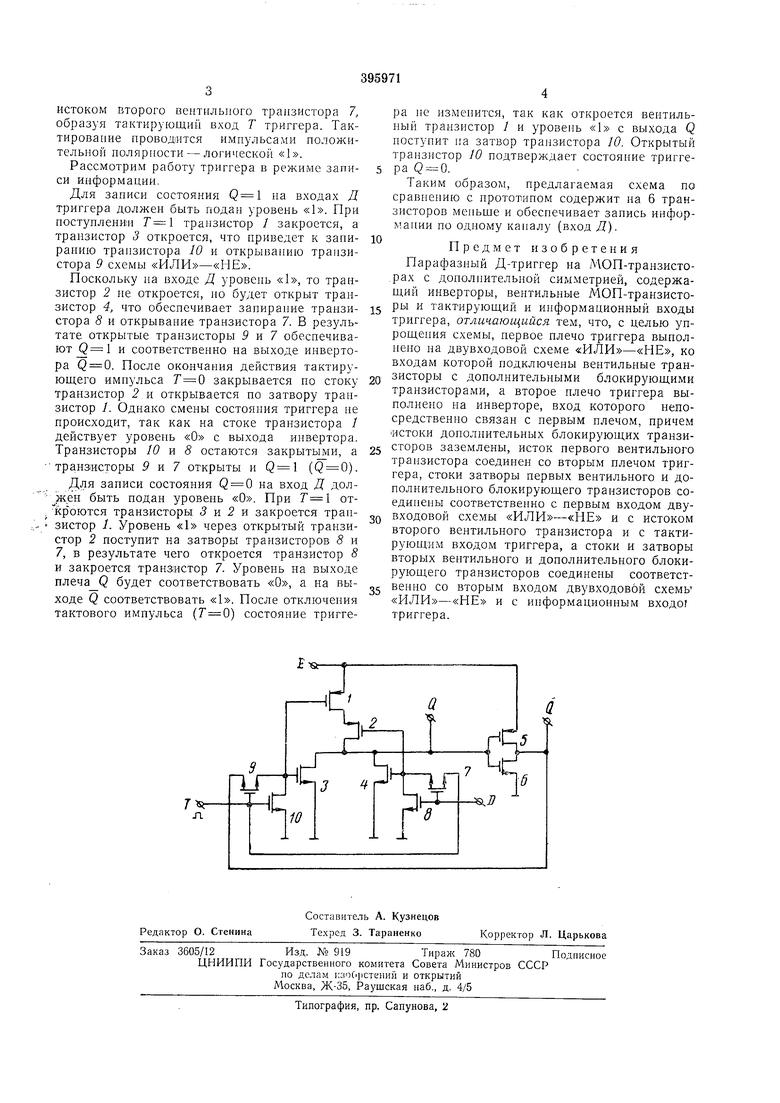

Сущность предложенного устройства поясняется чертежом.

Первое плечо Q триггера вынолпено на двувходовой схеме , ко входам которой подключены вептильные транзисторы ртипа / и 2, имеющие двустороннюю проводимость, с дополнительными блокирующими транзисторами, /г-типа и , а второе плечо Q выполнеио на инверторе (транзистор р-типа 5 и транзистор /г-тииа 6), вход которого непосредственно связан с первым плечом.

Истоки дополнительных блокирующих транзисторов 3 и 4 заземлены, а исток первого веитилыюго транзистора 1 соединен со вторым плечом триггера. Стоки и затворы вторых

вент льного 2 и дополнительного блокирующего 4 транзисторов соединены со вторым входом схемы (объединенные затворы транзисторов р-типа 7 и траизистора /г-типа 8), а их затворы объединены, образуя

инормационный вход Д триггера. Затворы первых веитильиого / и дополнительного блокирующего 3 транзисторов соединены с первым входом схемы (объединенные затворы транзистора р-типа 9 и трапзистора /г-типа /0), а их затворы соединены с

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОФАЗНЫЙ ИНВЕРСНЫЙ Д-ТРИГГЕР | 1973 |

|

SU405167A1 |

| Однофазный инверсный д-триггер | 1976 |

|

SU597068A2 |

| ОДНОТАКТНЫЙ СЧЕТНЫЙ ТРИГГЕР | 1972 |

|

SU326743A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Динамический триггер на моптранзисторах | 1976 |

|

SU657594A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU343308A1 |

| Триггер на МПД-транзисторах | 1984 |

|

SU1223349A2 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Тактируемый @ -триггер | 1984 |

|

SU1226618A1 |

| Счетный триггер | 1983 |

|

SU1088103A1 |

Авторы

Даты

1973-01-01—Публикация