1

Изобретение относится к вычислительной технике и предназначено для управления записью и считыванием информации.

Известные устройства содержат запоминающий блок с регистрами числа и адреса, дешифратор адреса сообщения, постоянный запоминающий блок, счетчик приоретитов, регистры обработки, регистры обмена, дешифраторы конца заголовка и конца сообщения, счетчик каналов, шины номеров каналов, блоки управления и распределения ячеек запоминающего блока и логические элементы.

Однако известные устройства имеют большой объем оборудования и недостаточное быстродействие.

Целью изобретения является сокрашение объема оборудования и повышение быстродействия устройства.

Для этого в устройстве выход постоянного запоминающего блока соединен с п-1 входами регистра адреса, первая кодовая щина канала соединена с первыми входами дешифраторов конца сообщения и конца заголовка, выходами регистров обработки, первым входом блока управления и первым выходом дещифратора адреса сообщения, вторая кодовая шина канала соединена со вторыми входами дешифраторов конца сообщений и конца заголовка, первыми входами третьего, четвертого пятого регистров обработки и дешифратора

адреса сообщения, с выходом регистра числа, второй выход дешифратора адреса сообщения соединен с пятыми входами регистра адреса и блока управления, выход дешифратора конца заголовка соединен с четвертым входом блока управления, первый выход которого соединен с первым входом второго регистра обмена, выход которого соединен с п-ным входом регистра адреса и вторым входом пятого регистра

обработки, выход дешифратора конца сообщения соединен со вторым входом блока управления, второй выход которого соединен с третьим входом пятого регистра обработки, выход которого соединен со входом третьего

элемента ИЛИ и вторым входом второго регистра обработки, третий вход блока управления соединен с выходами элементов ИЛИ, четвертый выход блока управления соединен со входом счетчика приоритетов, выход которого соединен с шестыми входами блока управления и регистра адреса, пятый выход блока управления соединен со счетным входом счетчика каналов, выход которого соединен с четвертым входом регистра адреса и

входом щины номера каналов, первый выход первого регистра обмена соединен со входом блока распределения ячеек запоминающего блока, выход которого соединен с первым входом первого регистра обмена, второй выход

которого соединен со вторыми входами третьего и четвертого регистров обработки, с первым и п-ным входами регистра адреса, выход первого регистра обработки соединен с третьим входом регистра адреса и четвертым входом первого регистра обмена, выход второго регистра обработки соединен со вторым входом регистра адреса, выход третьего регистра обработки соединен с первыми входами первого и второго регистров обработки, со входом первого элемента ИЛИ, со вторым входом первого регистра обмена, четвертый регистр обработки соединен со вторыми входами нервого и второго регистров обработки, со входом второго элемента ИЛИ, с третьим входом первого регистра обмена, второй выход блока управления соединен с третьим входом пятого регистра обработки, четвертый вход которого соединен с третьим выходом блока управления.

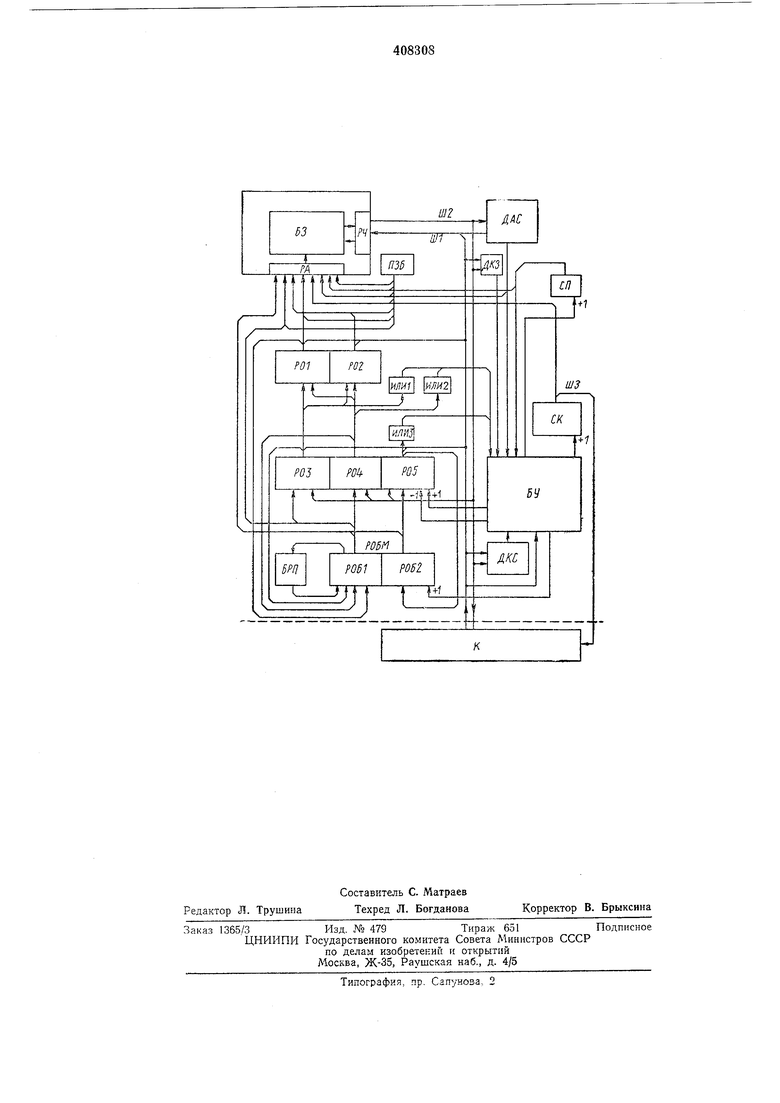

Изобретение пояснено чертежом.

На чертеже приведена функциональная блок-схема устройства.

Устройство для управления накоплением и выборкой информации содержит блок запоминания (БЗ), регистр числа (РЧ), регистр адреса (РА), первую и вторую кодовые шины информации (Ш1) и {Ш2), дешифратор адреса сообщения (ДЛС), постоянный запомипаюш,ий блок (ПЗБ), счетчик приоритетов (СП), элементы ИЛИ/-ИЛИ5, дешифратор конца сообщения (ДКС), дешифратор конца заголовка (ДКЗ), счетчик каналов (С/С), шину номеров каналов (Я/5), блок управления (БУ), блок распределения ячеек запоминающего блока (БРП), каналы (К), регистры обработки (Р01-Р05), соответственно первый, второй регистры обмена РОБМ РОБ1, РОБ2.

Работа устройства заключается в выполнении определенной последовательности следующих тактов.

1.К содержимому счетчика СК добавляется « + 1 из БУ; код номера канала из С/С по щинам подается на каналы, где осупхествляется выборка канала.

2.БУ вырабатывает управляющие сигналы,, по которым суммарный код СК и ячейки блока ПЗБ (константа, определяющая поле размещения фиксирующих ячеек каналов в 63) заносится в РА.

3.По адресу, хранимому в РА, осуществляется чтение с последующей засылкой считанного слова в РОЗ-Р05.

4.Обращение к БРП за кодом свободной зоны, занесение кода свободной зоны из БРП в РОБМ.

5.К содержимому РОБМ добавляется «1 из БУ, затем код РОБМ засылается в РА, по этому адресу в БЗ из выбранного канала ввода записывается ипформационное слово по шинам Ш1 после выдачи в канал из БУ синхроимпульса.

6.Код РОБ заносится в Р02.

7.Код РОБ2 заносится в Р05.

8.Запись содержимого Р01-РОЗ по шинам Ш в БЗ по адресу РА.

9.Установка всех регистров, счетчиков и триггеров за исключением С/С в «О.

10.Код Р05 заносится в РОБ2.

11.Код РОЗ заносится в РОБ1. 12. Установка в «О РОБ2.

13.Код РОБ заносится в Р04.

14.Код РОЗ заносится в Р01.

15.Установка в «О .

16.Занесение в РА суммарного кЪда из Р01 и из соответствующей ячейки ПЗБ.

17.Занесение кода из Р04 в РОБ1.

18.Запись содержимого РО и Р02 по шинам Ш1 в БЗ по адресу РА, причем по щинам Ш}, соответствующим разрядам Р05 заиисывается «О.

19.Занесение кода второй группы Р04 в POL

20.Установка в «О РОЗ.

21.Установка в «О Р04.

22. Установка в «О РО} и Р02.

23.Код адреса размещения фиксированной ячейки адреса заносится из ПЗБ в РА.

24.К содержимому Р05 добавляется «+1.

25.К содержимому РОБ2 добавляется «+1, код РОБ1 и РОБ2 заносится в РА, осуществляется чтение по этому адресу с передачей информации из РЧ в ДЛС.

26.Засылка кода РОБ1 в БРП.

27.Занесение в РА суммарного кода РОБ и кода соответствующей ячейки блока ПЗБ.

28.К содержимому РОБ2 добавляется «+1, код РОБ1 и РОБ2 заносится в РА, по этому адресу записывается из ДЛС информационное слово заголовка сообщений.

29. В РА из соответствующей ячейки блока ПЗБ и из ДЛС заносится код, задающий адрес определенной фиксированной ячейки очереди. 30. Засылка кода РОЗ в Р02.

31. Засылка суммарного кода Р02 и соответствующей ячейки блока ПЗБ в РА.

32.Занесение кода из Р04 в Р02.

33.Код РОБ1-РОБ2 заносится в РА, по этому адресу осуществляется чтение информационного слова с передачей по шинам Ш2 в выбранный канал вывода.

34.Из содержимого Р05 вычитается «-f I.

35.К содержимому счетчика СП добавляется « + 1.

36. Суммарный код счетчиков СП, СК и соответствующей ячейки блока ПЗБ заносится на РА.

37. Код РО1 заносится в РОБ. Последовательность выполнения тактов зависит от следующих условий.

Условие «3 - выбранный канал содержит информацию для ввода или вывода, в зависимости от того, какой выбран канал (ввода или вывода).

Условие «В - наличие «1 в самом старшем разряде С/С.

Условие «К - наличие в информации признака «конца заголовка.

Условие «О - наличие в информации признака «конец сообщения.

Условие «Д - наличие сигнала «Выполнено из ДЛС, указывающего на окончание дешифровки заголовка.

Условие «П - наличие в СП числа, большего, чем выбранное для системы нриоритетов.

Условие «Т - наличие «О в РОЗ.

Условие «С - наличие «О в Р04.

Условие «Р - наличие «О в Р05.

Устройство работает в нескольких режимах.

Режим «Н - (накопление).

Выполняется такт 1, проверяется условие «3, если условие не выполняется, то повторяется такт 1 до выполнения условия «3 или «В (переход в другие режимы работы).

Если условие «3 выполняется, то выполняются такты 2, 3; проверяется условие «Т. Если условие «Т вынолняется, то выполняются такты 4, 5, 6, 7, 2, 8, 9, иначе-проверка условия «С, при выполнении условия «С проверяется условие «Р, при выполнении условия «Р выполняются такты 4, 5, 7, 13, 2, 8, 14, 15, 13, 16, 8 и 9; при невыполнении условия «Р - такты 10, 11, 5, проверка условия «К, при выполнении условия «К - такты 12, 7, 2, 8, 9, иначе - 7, 2, 8, 9.

При выполнении условия «3 и невыполнении условий «Т и «С проверяется условие «Р, если условие «Р выполняется, то - такты 4, 5, 7 и проверка условия «О, если условие «О выполнено, то - такты 2, 18, 19, 13, 11, 20, 21, 16, 8, 6, 622, иначе -- такты 19, 13, 2, 8, 20, 21, 16, 8, 9. При выполнении условия «3 и невыполнении условий «Т, «С, «Р - такты 10, 17, 5, 7, 2, проверка условия «О, если условие «О выполняется, то - такт 18 и переход в режим «Oi, иначе - такты 8 и 9.

Режим (очередь на дешифрацию заголовка).

Выполняются такты 11, 15, 23, 3, проверяется условие «Т, если условие «Т выполняется, то - такты 6, 23, 8 и 9 с переходом к режиму «Oj, иначе проверка условия «С, если условие «С выполняется, то - такты 13, 14, 23, 8, 15, 6, 16, 8, 9 и переход к режиму «Оо, иначе -такты 19, 13, 23, 8, 15, 6, 16, 8, 9 и переход к режиму «02.

Режим (выдача сообщений на дешифрацию).

Выполняются такты 23, 3, проверяется условие «Т, при выполнении условия «Г исполняется такт 1, иначе - проверка условия «Р. При выполнении условия «3 - такты 11, 24, 25, проверка условия «К, если условие «К выполняется, то - такты 9, 1, иначе- такт 25 и проверка условия «К. При невыполнении условия «Р - такт 1.

Режим (очередь на выдачу сообш,ений).

При выполнении условия «В проверяется условие «Д, при невыполнении условия «Д осуществляется переход к режиму «В, иначе-такты 23, 3, 14, 11, 26, 12, 17, 15, 16, 3, 13, 23, 8, 12, 4, 16, 3, 28, проверка условия «К, если условие «К не выполняется, то такт 28

повторяется до выполнения условия «К, если условие «К выполнено, то - такты 29, 3, проверка условия «Т, если условие «Т выполняется, то - такты 29, 8, 5, проверка условия «Д, если условие «Д выполняется, то -такты 4, 16, 13, 27, 8, 24, 16, 8, 15, 28, 29, 3, проверка условия «Т. Если условие «Т выполнено, а условие «С нет, то - такты 16, 3, 22, 10, 19, 16, 3, 7, 16, 8, 9 и переход к режиму «в. При невыполнении условия «Т проверяется выполнение условия «С, если условие «С выполнено, то - такты 13, 30, 29,

8,15, 6, 31, 8, 15, проверка условия иначе-такты 32, 13, 29, 8, 15, 6, 31, 8, 15, проверка условия «Д.

Режим (выдача сообщений). Выполняется такт 1, проверка условия «3, если условие «3 не выполняется, то - проверка условия «Б, если условие «В выполняется, то - такт 1, если условие «В не выполняется, то - переход к режиму «Н. Если условие «3 выполняется, то - такты 2, 3, проверка условия «С, если условие «С выполняется, то - такты 35, 36, 3, проверка условия Т, если условие «Т выполняется, то- такты 9, 35, 36, проверка условия «П, если условие «П выполняется, то - такты 9, 1; иначе - проверка условия «Т. Если условие «Т не выполняется, то - такты 14, 12, 17, 15,

16, 3, 13, 36, 12, 37, 15, 22, 6, 13, 25, 33, 25, 7, 2,8,9,1.

При выполнении условия «3 и невыполнении условия «С - такты 10, 17, 33, проверка условия «К, если условие «К выполняется, то -такты 14, 12, 11, 15, 16, 3, 6, 25, 2, 8,

9,1; иначе - проверка условия если условие «О выполняется, то - такты 12, 22, 14, 11, 26, 12, 17, 15, 16, 3, 34, проверка условия «Р, если условие «Р выполняется, то - такты 12, 17, 19, 15, 2, 8, 26, 12, 16, 3, проверка условия если условие «С выполняется, то - такты 9, 1; иначе - такты 12, 17, 19, 18, 26, 12, 16, 3, проверка условия «Р. Если условие «Р при выполнении условия «О не выполняется, то - такты 16, 8, 9, 1.

Если условие «О не выполняется, то проверяется условие при выполнении условия «Р -такты 32, 12, 11, 15, 16, 3, 6, 25, 2, 8, 9, 1; при невыполнении условия «Р - такты 24, 2,8, 9, 1.

Предмет изобретения

Устройство для управления накоплением и выборкой информации, содержащее запоминающий блок, соединенный с регистрами числа и адреса, дешифратор адреса сообщения, постоянный запоминающий блок, счетчик приоритетов, регистры обработки, регистры обмена, дешифраторы конца заголовка и конца

сообщения, счетчик каналов, каналы, блоки управления и распределения ячеек запоминающего блока и логические элементы, отличающееся тем, что, с целью сокращения объема оборудования и повыщения быстродействия устройства, в нем выход постоянного запоминающего блока соединен с п-1 входами регистра адреса, первая кодовая шина канала соединена с первыми входами дешифраторов конца сообш,ения и конца заголовка, выходами регистров обработки, первым входом блока управления и первым выходом дешифратора адреса сообщения, вторая кодовая шина канала соединена со вторыми входами дешифраторов конца сообщений и конца заголовка, первыми входами третьего, четвертого, пятого регистров обработки и дешифратора адреса сообщения, с выходом регистра числа, второй выход дешифратора адреса сообщения соединен с пятыми входами регистра адреса и блока управления, выход дешифратора конца заголовка соединен с четвертым входом блока управления, первый выход которого соединен с первым входом второго регистра обмена, выход которого соединен с п-пыи входом регистра адреса и вторым входом пятого регистра обработки, выход дешифратора конца сообшения соединен со вторым входом блока управления, второй выход которого соединен с третьим входом пятого регистра обработки, выход которого соединен со входом третьего элемента ИЛИ и вторым входом второго регистра обработки, третий вход блока управления соединен с выходами элементов ИЛИ, четвертый выход блока управления соединен со входом счетчика приоритетов, выход которого соедине 1 с шестыми входами блока управления и регистра адреса, пятый выход блока управления соединен со счетным входом счетчика каналов, выход которого соединен с четвертым входом регистра адреса и входом шины номера каналов, первый выход первого регистра обмена соединен со входом блока распределения ячеек запоминающего блока, выход которого соединен с первым входом первого регистра обмена, второй выход которого соединен со вторыми входами третьего и четвертого регистров обработки, с первым и п-ным входами регистра адреса, выход первого регистра обработки соединен с третьим входом регистра адреса и четвертым входом первого регистра обмена, выход второго регистра обработки соединен со вторым входом регистра адреса, выход третьего регистра обработки соединен с первыми входами первого и второго регистров обработки, со входом первого элемента «ИЛИ, со вторым входом первого регистра обмена, четвертый регистр обработки соединен со вторыми входами первого и второго регистров обработки, со входом второго элемента ИЛИ, с третьим входом первого регистра обмена, второй выход блока управления соединен с третьим входом пятого регистра обработки, четвертый вход которого соединен с третьим входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления записьюи СчиТыВАНиЕМ иНфОРМАции | 1979 |

|

SU809181A2 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| Устройство для контроля схем сравнения | 1984 |

|

SU1228107A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

Авторы

Даты

1973-01-01—Публикация