.(54) ИНТЕГРО-ЛРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU744654A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных комплексах, работающих в системах управления, требующих решения в реаль-5 ном масштабе времени эпизодических (точечных) задач и математических зависимостей с непрерывным характером изменения переменных, описываемых различного вида дифференциальными 0 уравнениями, а также проверки логичес-. :ких условий, формирования управляющих кодов.

Известно интегрирующее устройство Qll, содержащее устройство формиро- 15 вания и хранения выходных приращений, сумматоры, регистр подынтегральной функции, схему умножения, сдвигающий perjicTp, элементы И, ИЛИ.

Быстродействие такого устройства 20 оказывается недостаточным при решении дифференциальных уравнений и математических зависимостей с непрерывным характером изменения переменных.

Из известных устройств наиболее 25 близким по технической сущности к изобретению является устройство РД которое содержит блок интегрирования, состоя1дий из первого регистра подын.тегральной функции, второго регистра 30

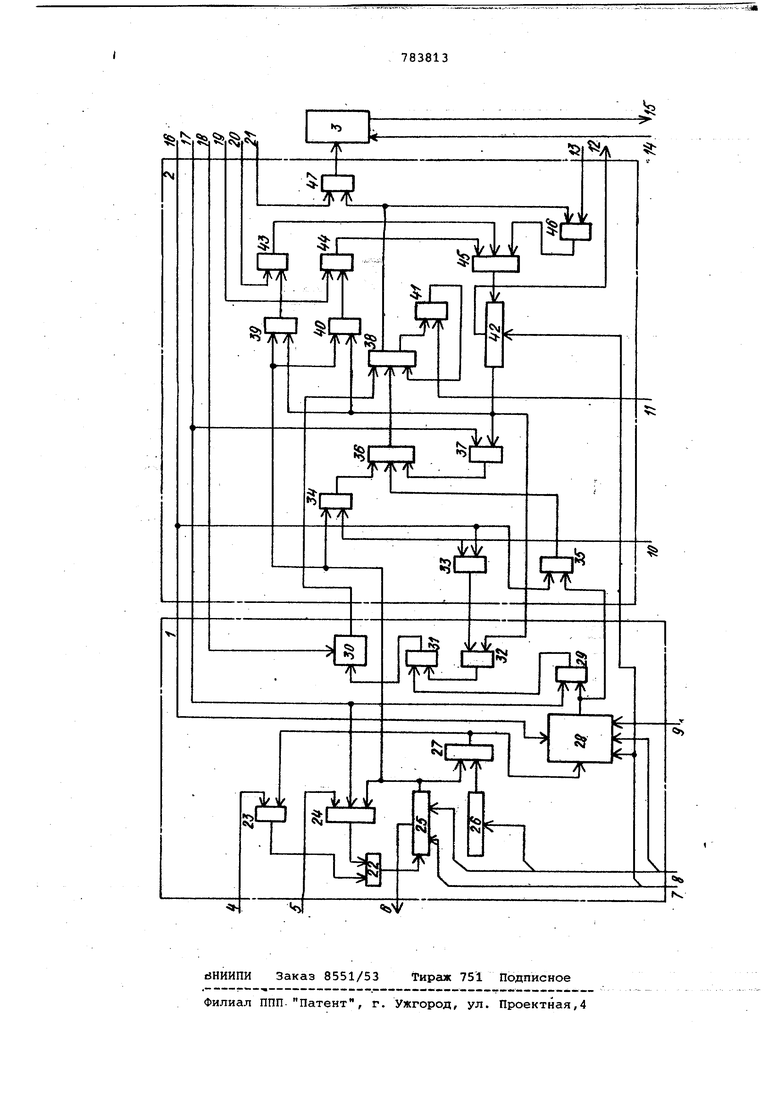

нового приращения подынтегральной функции, формирователя приращения интеграла, преобразователя кода, первого двухвходового сумматора для формирования нового значения подынтегральной функции, первого, второго, третьего и четвертого логических элементов И, первого и второго логического элемента ИЛИ , блок суммирования приращений, состоящий из регистра частичных сумм неквантованных приращений интегралов, второго двухвходового сумматора для формирования частичных сумм неквантованных приращений интегралов, пятого/ шестого, седьмого и восьмого логических элементов И, третьего элемента ИЛИ, блок экстраполяции и квантования, в котором блок интегрирования через блок суммирования приращений соединен с первым входом блока экстС)аполяции и квантования, второй вход которого подключен к восьмому входу устройства, а выход связан с третьим выходом устройства, первые входы первого и второго регистров и первый вход формирователя приращения интеграла соединены с третьим входом устройства, первый выход устройства Соединен со вторым выходом первого регистра, шестой вход устройства соединен со вторым входом формирователя приращения интеграла, третий вход .первого регистра и четвертый вход формирователя приращений - с четвертым входом устройства, второй выход третьего регистра подключен ко второму выходу устройства. В блоке интег рйрования первый выхбд первого регистра подключен ко второму входу первого логического элемента И и к первому входу первого двухвходового сумматора, по второму входу соединенного с выходом второго регистра, а по вйходу подключенного к первому входу втйрог ОЗогйчейкбг6 элёмента второй вход которого соединен с первым входом устройства, а выход - с первым входом первого логического элемента ИЛИ, второй вход которого связан с выходом первого логического элемента И, по первому входу связанного со вторым входом устройства, выход пёрвогр логического элемента ИЛИ соедине со вторым входом первого регистра под ынтегральной функции, одновременно вы ход первого двухвходового сумматора с третьим входом формирователя приращения интеграла. Формирователь приращений --йнтегр-алоВ -ffd-tt/TT&SfSriilfeiy соединен с одиннадцатым входом устрой ства, а по выходу - с первым входом третьего логического элемента И, который по второму входу связан с третьим входом первого логического элемента И, и с десятым входом устройства, а по выходу - с первым входом вто ро лбзгичёскбго элемента ИЛИ, второй . вход которого соединен с выходом четвертого логического элемента И/ Соединенного по первому входу с первым выходом третьего регистра, а по Второ йУ S fffly - с одиннадцатым входомуст ройства. Выход второго логического элемента ИЛИ соединен со вторым входом преобразователя кода, пятый вход устройства - с первым входом преобразователя кода. В блоке суммирования приращения второй вход второго двухвходового сумматора соединен с выходом преобразователя кода блока интегр рования, выходом логического элемента И, второй вход которого связан с один надцатым входом устройства, а выход. соединен с первым входом третьего л6гического элемента ИЛИ, второй вход которого связан с выходом шестого лог.ического элемента И, первый вход которого подключен к десятому вхо ДУ ус;Тр6йства, а второй вход соединей с первым выходом третьего ре гистра чдстичных сумм неквантованных п р5Й1ращёнйй интегралов, втор(5й выход которого подключён ко второму выходу устройства, а вход соединен с выходом восьмого логического элемента И, первый вход которого соединен с выходом второго двухвходового сумматора, второй вход подключен к седьмому Вхо дУ уйтройства. Выход третьего логйчес кого элемента ИЛИ соединен с первым входом второто двухвходового сумматора, выход которого связан с первым входом седьмого логического элемента И, второй вход которого подключен к девятому входу устройства, а выход связан с-первым входом блока экстраполяции и квантования. В данном устройстве вычисление математических зависимостей осуществляется путем интегрирования систем эквивалентных уравнений Шеннона, если вычисления носят непрерывный характер, или с использованием методов вычисления функций в точке при эпизодическом характере вычислений. При вычислении целого ряда зависимостей в точке для повышения скорости к точности вычислений целесообразно использовать аппроксимирующие полимоны, параметры которых защсят от интервала нахождения аргумента, определение которого легко выполняется с помощью логических операций. Однако известное устройство не позволяет использовать такие алгоритмы в связи с трудностями определения интеграла. В этих случаях вычисления ведутся по более трудоемким полиномам (например, итерационным) или путем интегрирования порождающих систем уравнений, что снижает скорость Вйчислений. Кроме того, отсутствие в известном устройстве логических операций существенно сужает его функциональнь1е возможности и область использования в системах управления. Целью изобретения является повышение быстродействия и расширение функциональных возможностей путем выполнения логических операций сравнения выделения и формирования. Предлагаемое устройство содержит регистры, формирователь приращений интеграла, сумматоры, преобразователь кода, блок экстраполяции и квантования, элементы И, ИЛИ. При этом, первые входы первого и второго регистров и формирователя приращений интеграла соединены с первым информационным входом устройства, второй информационный вход которого связан с первым входом третьего регистра и с.вторыми входами первого регистра и формирователя приращений интеграла, третий вход которого является третьим информационным входом устройства, первый выход первого регистра, служит первым инфор1мационным выходом устройства, второй информационный выход которого соединен с выходом третьего регистра. Первый вход первого сумматор,а связан с выходом второго регистра, выход первого сумматора подключен к первому входу первого элемента И, второй вход которого является входом признака значения .подынтегральной функции устройства. Шход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу второго элемента. И, выход первого элемента ИЛИ - с третьим входом первого регистра. Первый вход второго элемента И является входом ин версии .признака значения подынтёграл, ной функции устройства. Выход первого сумматора подключен к четвертому входу формирователя приращений интеграла пятый вход которого соединен с входом признака умножения устройства, а вы ход - с первым входом третьего Элемента И, выход KOTotoro связанс первым входом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И. Выход второго элемента ИЛИ подключен к первому входу преобразователя кода, второй вход которого является 1входом признака инверсии устройства. ПервЕлЙ вход второго сумматора соединен с выходом преобразователя кода, первый выход второго сумматора - с первым входом пятого элемента И, второй вход которого является входом признака окончания формирования переменной интегрирования устройства. Выход пятого элемента И соединен с первым входом блока экст раполяции и квантования, второй вход и выход котброго служат соответствбнно четвертым информационным входом и третьим информационным выходом устройства. Первый выход второго сумматора соединен с первым входом шёстО Ъ элемента И, второй вход которого является входом инверсии признака окончания формирования переменной интегри рования устройства, выход формирователя приращений интеграла - с первым входом седьмого элемента И, второй вход которого соединен с входом пр иэнака умножения устройства. Выход седьмого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выхо ду восьмого элемента И, выход третьего элемента ИЛИ - с вторым входом второго сумматора, второй выход третьего регистра соединен с первыми входами четвертого и восьмого элементов И, второй выход первого регистр подключен к вторым входам первого сумматора и второго элемента И. Особенностью предлагаемого устройства является то, что в него введены пять элементов И с девятого по тринадцатый и три элемента ИЛИ, причем с по шестой вторые входы тре тьего и восьмого JTeMeHTOB И и третий вход второго элемента соединены с вхо дом признака интегрирования устройства, второй выход первого регистра подключен к первому входу девятого эЛёмента И,второй вход которого соединен с вторым выходом третьего регистра. Вы ход девятого элемента И соединен с первым входом десятого элемента И- вто рой вход которого является входом признака выделения устройства, выход десятого элемента И - с первым входом четвертого элемента ИЛИ, второй вход которого, связан с выходом шестого элемента И. Выход четвертого элемента ИЛИ соединен с вторым входом третьего регистра, второй выход первого регистра подключен к первому входу пятого элемента ИЛИ, второй вход которого соединен с вторым выходом третьего регистра, а выход подключен к первому входу одиннадцатого элемента И, второй вход которого является входом признака формирования устройства. Выход одиннадцатого элемента И подключен -к третьему входу четвертого элемента ИЛИ, второй выход первого регистра соединен с первым входом двенадцатого элемента И, выход которого подключен к третьему входу третьего элемента ИЛИ. Второй вход двенадцатого элемента И и первый вход шестого элемента ИЛИ соединены с входом признака сравнения устройства. Второй вход шестого элемента ИДИ соединен с входом признака умножения устройства, выход - с вторым входом четвертого элемента И. Второй выход второго сумматора подключен к первому входу тринадцатого элемента И, второй вход которого является входом инверсии признака сравнения. Выход тринадцатого элемента И соединен с третьим выходом второго сумматбра. На чертеже представлена блок-схема устройства. Она содержит:блок 1 интегрирования; блок 2 суммирования приращений; блок 3 экстраполяции и «вантования; вход 4 признака значени подынтегральной функции; вход 5 инверсии признака значения подынтегральной функции; вьаход б для записи в блок хранения поддантегральной функции запоминающего устройства (ЗУ) информации с первого регистра подынтегральной функции; информационный вход 7 для занесения из блока хранения чисел (на чертеже не показан) сомножителей в первый регистр и формирователь приращений, а также операндов для выполнения операций выделения и формирования в первый и второй регистры и операндов гдля выполнения операции сравнения в первый и третий регистры; информационный вход 8, по которому из блока хранения подынтегральной функции ЗУ в блок интегрирования поступают приращения подынтегральной функции и подынтегральная ФУНКЦИЯ)вычисленная в предыдущем шаге интегрирования информационный вход 9i для занесения из блока храненияпеременной интегрирования ЗУ в формирователь приращений интеграла приращений переменной интегрирования; вход 10 признака сравнения; вход 11 для инверсии признака сравнения; информационный выход 12, по которому из третьего 1 егистра в блок хранения чисел ЗУ поступает результат операций умножения, умножения со сложением, умножения с вычитанием, сравнения, вьщеления или формирования вход 13 инверсии признака окончания формирования переменной интегрирования; информационный вход 14 для занесёния блока хранения квантованных приращенийостатков ЗУ в блок экстраполяции приращения переменной и остаток, полученный при квантовании переменной в предыдущем интегрировании; информационный выход 15, по которому из блока экстраполяции и квантования поступают квантованные и экстраполиро ванные приращения и новый остаток в блок хранения квантованных приращений и остатков ЗУ; вход 16 признака умножения rtmf вход 17 признака интегри рования Пи; вход 18 п изнака инверси Пг; вход 19 признака выделения Пвд; вход 20 признака формирования Пфр} вход 21 признака окончания формирова ния переменной интегрирования flfkr. Устройство содержит также элемент ИЛИ 22, элементы И 3, 24, регистр 25 для хранения подынтегральной функ ции регистр 26 для хранения новйто приращения подынтегральной функции; сумматор 27; формирователь 28 приращ ния интегралов элемент И 29, преобразователь 30 кода, элемент ИЛИ 31, элемент И 32, элемент ТШИ 33, элемен ты И 34, Э5, элемент ИЛИ 36, элемент И 37, сумматор 38, элемент ИЛИ 39, элементы И 40, 41, регистр 42 для хранения частичных сумм, элементы И 43, 44, элемент ИЛИ 45, элементы И 46, 47. В блоке 1 интегрирования при выпол нении операций интегрирования по заданной формуле численного интегрирования по Стилтьесу вычислйются прира щения интеграла а при наличии признака Пг - приращения - . vy и при выполнении операции умножения. с вычитанием (Y, Yg) вычисляется произведение сомножителей ху и осуще ствляётся инверсия операнда, храняще го в регистре 42 блока суммирования приращений при наличии.признака П z. Кроме того, в блоке 1 формируются но вые значения подынтегральной функции ). ... Блок 2 суммирования приращений служит для образования неквантованно го эЛачеЯкя приращения k-й функции VU --дц путем суммирования приращений 75р9г(.,)Д интеграловтри работе в режиме интегрирования, для образования суммы произведения ху с операндо R(-l) при выполнении операций Yj. , и для формирования результатов логических бПёраций сравнения, в1ыдё7 ния и формирования. В блоке 3 экстраполяции и квантования осуществляется вычисление экстраполированных значений приращений Ц(л4-г) квантованных приращений l Jiiltj} .О и остатка --- ду Рассмотрим вычислительный процесс при выполнении операции интегрирования в (i+l)-M шаге при работе устройства, который начинается после получения из блока хранения подынтегральной функции ЗУ (на чертеже не показан) по входу 8 приращения ) гистр 26, и приращений (об О, 1,...,т-1) в формирователь 28 Приращения. Кроме того, при выполнении экстраполяции и квантования по входу 14 в блок 13 поступает остаток и приращения ( 1, . 2,...,т). После занесения в устройство необходимой для вычу йлений информации значение ординаты Yprl поступает на вход сумматора 27, на другой вход которого поступает значение приращения УРГ(4.4) с выхода регистра 26. Новое значение подынтегральной функции Ypr (l+l) с выхода сумматора 27 направляется в формирователь 28 Приращения и одновременно поступает в регистр 25 через элемент К 23f на вход которого поступает признак nykr, и элемент ИЛИ 22. В случае Ilykr О неизменное значение подынтегральной функции с выхода регистра 25 через элемент И 24 и ИЛИ 22 перезаписывается Ё регистр 25. Полученное на выходе формирователя 28 приращение-- ЗГ11И;, поступающее при Пи 1 через элемент И 29 и элемент ИЛИ 31 в преобразователь 30 кода, умножается в последнем на коэффициент (-1)4 С выхода преобразователя кода эначе ние направляется на вход сумматора 38 и складываетсд с содержимым peifHCTpa 42, поступакяцим на сумматор 38 через элемент И 37 при Пи 1, и элемент ИЛИ 36. Если, признак окончания формирования переменной nfkr О, сумма выхода сумматора 38 через элемент 46 и элемент ИЛИ 45 проходит.is регистр 42. Если nfkr 1, элемент И 46 закрыт и с выхода сумматора 38 через элемент И УУц(и1 47 приращение поступает в У блок 3. После окончания вычислений на выход 6 устройства поступает и заносится в блок хранения подынтегральной функции в ЗУ значение Ypri при IJykr « О или Ypr (i+1) при rigkr 1, снима емое с выхода регистра 25, а на выход 15 поступают и заносятся в блок хране ния квантованных приращения и остат Ук(и) ков ЗУ значения At} oancuii при nfkr 1 и приращение прИ| выполнении экстраполяции приращения. Вычислительный процесс выполнения операции умножения начинается после поступления по входу 7 множимого Y регистра 25, множителя в формирователь 28 приращения интеграла. Операнд R является результатом предыдущей опе рации и к началу рассматриваемой oneрации хранится в регистре 42. После занесения в устройство необходимой для выполнения операции информации ко множимого из регистра 25 через сумматор 27, на вход которого поступает нулевая информация с выхода регистра 26, без изменения проходит на вход формирователя 28 приращения, осуществляющего при Пт 1 перемножение величин. Произведение с выхода формирователя приращения через элемент И 35 элемент ИЛИ 36 поступает на вход сумматора 38. На другой вход этого сумматора с выхода регистра 42 через эле мент И 32, элемент ИЛИ 31 и преобразо ватель 30 кода, на вход которого заво дится оризиак П г, поступает величина R (-I) При выполнении операции Пz 0 с выхода преобразователя 30 кода на вход сумматора 38 поступает величина R. При выполнении операции Y Qf при Пг 1 в преобразователе 30, кода формируется величина -R. В сумматоре 38 формируется сумма z R(-l) поступающая на вход регистра 42 через элемент И 46, дополнительный при nfkr и через элемент И 45. Результат операции Y , Yg,,; остается в регистре 42 и заносится в блок хранения чисел ЗУ с выхода 12 устройства. Вычислительный процесс выполнения логических операций выделения (вд) и формирования (фр) начинается после . поступления из блока хранения чисел ЗУ по входу 7 первого операнда х в ре гистр 25. Вели Пвд - 1 коды операндов поступают из регистра 25 и регистра 42 иа элемент И 40, на котором образуется результат операции вьшеления, и через злемеит И 44 и элемент ИЛИ 45 поступает в регистр 42. Если Пфр «- 1 кода операндов из регистра 25 и регистра 42 поступают на элемент ИЛИ 39, на котором образуется результат операции фосмирования. Затем этот резуль тат поступает через элемент И 43 и элемент ИЛИ 45 в регистр 42. Результат выполнения логической операции выделения, или формирования из регистра 42 с выхода 12 устройства поступают в блок хранения чисел ЗУ. Вычислительный процесс выполнения логической операции сравнения начинается после поступления операндов х в регистр 25 и R в регистр 42 из блока хранения чисел ЗУ по входу 7 устройства. Операнд X поступает из регистра 25 через элемент И 34 при наличии признака Пер и через элемент ИЛИ 36 на вход су№латора 38. Операнд R с выхода регистра 42 проходит через элемент И 32 при наличии на входе элемента И 35 признаки Пер через элемент ИЛИ 31, преобразователь 30 кода на вход сумматора 38. Цель переноса с выхода С5 матора 38 через элемент И 41 на выход сумматора 38 остается не замкнутой. Результат операции сравнения с выхода сумматора 38. поступает через элемент И 46 и элемент ИЛИ 45 на вход регистра 42. Результат операции сравнения чисел поступает с выхода регистра 42 по выходу 12 в блок хранения чисел ЗУ. Использование устройства позволяет увеличить скорость отработки в точке функциональных зависимостей, вычис ляемых по полиномам предварительного определения интервгша нахождения аргумента с помсмцью логических операций. При этом выигрыш достигается тем, что время вычисления ряДа математических зависимостей.при использовании аппроксимирующих полимонов, параметры которых зависят от ийтервала нахождения аргумента, меньше, чем по другим алгоритмам или путем интегрирования порождающих систем уравнений. Формула изобретения Интегро-арифметическое устройство, содержащее регистры, формирователь приращений интеграла, супинаторы, преобразователь кода, блок экстраполяции и квантования, элементы И, ИЛИ, причем первые входы первого и второго регистров и формирователя П1эиращений интеграла соединены с первым информационным входом устройства, второй информационный вход которого соединен с перЕыг входом третьего регистра и вторыми входами первого региЬтра и формирователя приращений интеграла, третий вход которого является третьим информационным входом устройства, первый выход первого регистра является первым информационным выходом устройства, второй информационный выход которого соединен с .ыходомтретьего регистра, первый вход первого сумматора соединен с выходом второго регистра, выход Первого сумматора подключен к первому входу первого элемента И, второй вход которого является входом признака значения подынтегральной функции устройства, выход первого эле мента И соединен с первым входом первого элемента ИЛИ, втсэрой вход которого подключен к выходу второго элемента И, выход первого элемента ИЛИ соединен с третьим входом первого регистра, первый вход второго элемента И является входом инверсии признака значения подынтегральной функции устройства, выход первого сумматора подключен к четвертому входу формирователя приращений интеграла, пятый вход которого соединен с входом признака умножения устройства, а выход соединен с первьвй входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с Ьыходом четвертого элемента И, выход второго эле мента ИЛИ подключен к первому входу преобразователя кода, второй вход которого является входом признака инвер сии устройства, первый вход второго сумматора соединен с выходом преобразователя кода, первый выход второго сумматора соединен с первым входом пя того элемента И, второй вход которого является входом признака окончания формирования переменной интегрироваНй й. устройства, выход пятого элемента И соединен с первым входом блока экст раполядии и квантования, второй вход и выход которого являются соответствейно четвертым информационным входом и третьим информационным выходом устройства, первый выход второго сумматора соединен с первым входом шес,трго элемента И, второй вход которого является входом инверсии признака окончания формирования переменной интегрирования устройства, выход формирователя приращений интеграла соединен с первым входом седьмого элемента И, второй вход которого соединен с входом признака умножения устройства, выход седьмого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выхо ду вогйьмого элемента И, выход третьего элемента ИЛИ соединен с в О1зйй вхо дом BTOjSoro сумматора, второй выход третьегорегистра соединен с первыми вхЪдами четвертого и восьмого элементов И, второй выход первого регистра подключен к вторым входам первого - сумматора и второго элемента И, о т личающаееся тем, что, с целью повышения быстродействия, в него введено пять элементов И с девятого по тринадцатый и три элемента ИЛИ, причем с четвертого по шестой вторые входы третьего и восьмого элементов И и третий вход второго элемента И соединены с входом признака интегрирования устройства, второй выход первого регистра подключен к первому входу девятого элемента И, второй вход которого соединен с вторьом выходом третьего регистра, выход девятого элемента И соединен с первым входом десятого элемента И, второй вход которого является входом признака выделения устройства, выход десятого элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выход четвертого элемента ИЛИ соединен с вторым входом третьего регистра, второй выход первого регист ра подключен к первому входу пятого элемент а ИЛИ, второй вход которого соединен с вторым выходом третьего регистра, а выход подключен к первому входу одиннадцатого элемента И, второй вход которого является входом признака формирования устройства, выход одиннадцатого элемента И. подключен к третьему входу четвертого элемента ИЛИ, второй выход первого регистра соединен с первым входом двенадцатого элемента И/ выход которого подключен к третьему входу третьего элемента ИЛИ, второй вход двенадцатого элемента И и первый вход шестого элемента ИЛИ соединены с входами признака сравнения устройства, второй вход шестого элемента ИЛИ соединен с входом признака s лнoжeния устройства, выход соеди-. нен с вторым входом четвертого элемента И, второй выход второго сумматора подключен к первому входу тринадцатого элемента И, второй вход которого является входом инверсии признака сравнения, выход тринадцатого элемента И соединен с третьим выходом второго сумматора. Ис точ н ик и,информации, принятые во внимание при экспертизе -1. Авторское свидетельство СССР «.418864, кл. G Об J 1/02, 1972, 2. Авторское свидетельство по заявке 2438194/13-24, кл, G 06 J 1/02, 1977,

Авторы

Даты

1980-11-30—Публикация

1979-01-24—Подача