I

Предлагаемое изобретение относится к области вычислительной техники и может быть использовано в цифровых интегрирующих машинах и однородных интегрирующих структурах с многоразряднымИ приращениями.

Известны блоки логических операций для цифровых интегрирующих мащин, содержавшие узел накопления приращений, сумматор подынтегральной функции, узел управляющих импульсов и потенциалов, узел выработки н хранения иоправкн и узел выходных приращений.

Однако известные блоки имеют низкую точность работы и ограниченные функциональные возможности в выполнении логических операций.

В известных логических блоках в зависимости от знаков подынтегральных функций (i-1)-го и 1-го тагов рещения задачи выдается величина выходного приращения /-го тага (v 2i ), в то время как для рещения задачи в следующем щаге в экстраполяциониых интегрирующих мащинах требуется значение выходного ириращеиия (i + 1)-го щага рещения ( v2;+i). Значение приращения (i + 1)-го ( ) получают путем дополнительной экстраполяции выходных приращений (AZ,) на один щаг вперед, то есть принимают AZ;+1 равным .,- При таком подходе существенно снижается точность работы устройства, та.к как становится невозможным своевременное введение поиравки.

В предлагаемом блоке логических операций для цифровых интегрирующих машин в его состав введен экстрано.тятор, вход которого соединен с первым входом блока и третьим входом узла выходных приращений, первый выход - со вторым входом сумматора

подынтегральной функции, а второй выход - со вторым входом узла управляющих импульсов и потенциалов, третий вход которого подключен к выходу сумматора подынтегральной функции и к третьему входу узла выработки

и хранения поправки, третий выход - ко второму входу узла накопления приращений, а четвертый вход - к выходу регистра кода операций, выход которого соединен со вторым входом блока.

Это позволяет повысить точность и расширить функциональные возможности блока.

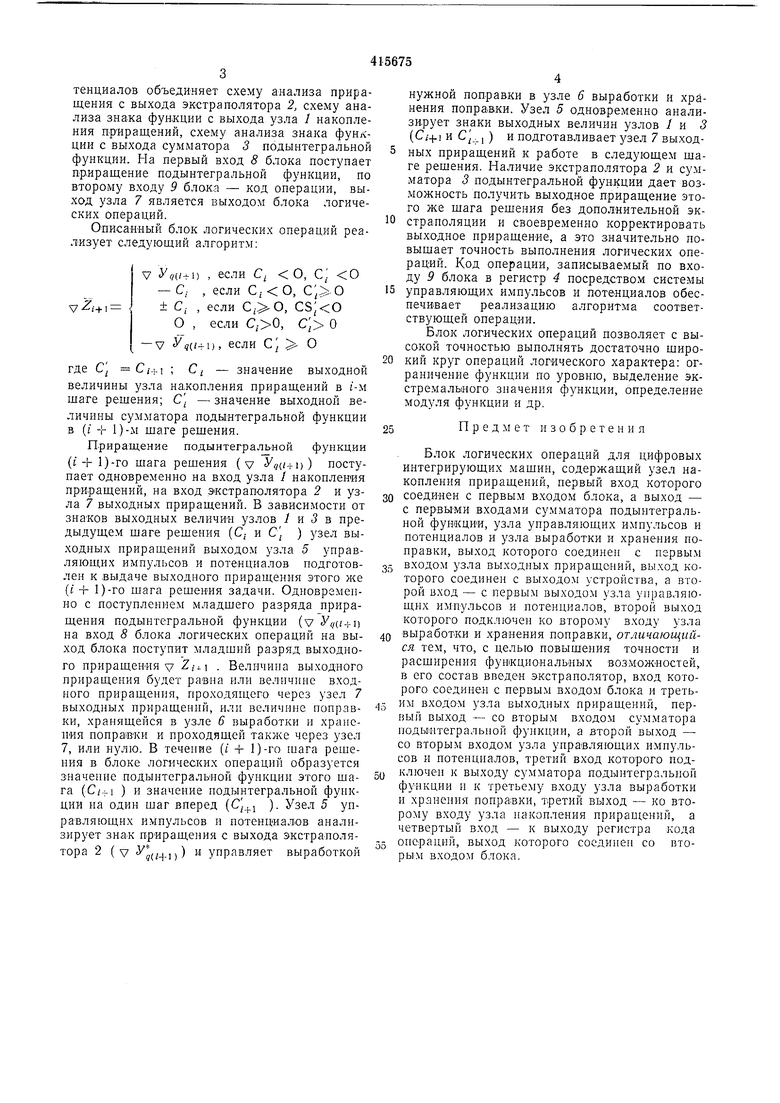

Схема блока логических операций изображена на чертеже.

Блок логических операций содержит узел / накопления приращений, экстраполятор 2, сумматор 3 подынтегральной функции, регистр 4 кода операции, узел 5 управляющих импульсов и потенциалов, узел 6 выработки и хранення поправки н узел 7 выходных приращений. Узел 5 управляюп их импульсов и потенциалов объединяет схему анализа приращения с выхода экстраполятора 2, схему анализа знака функции с выхода узла 1 накопления Приращений, схему анализа знака фунлции с выхода сумматора 3 подынтегральной функции. На первый вход 8 блока поступает приращение подынтегральной функции, по второму входу 9 блока - код операции, выход узла 7 является выходом блока логических операций.

ОписаННый блок логических операций реализует следующий алгоритм:

V У(/-М) , если С О, С; 0 - С,. , если , ± С; , если ,

2-:iJf I О , если , с; О

- V Уq(i), если С) о

где С - CM-I ; С i - значение выходной величины узла на.копления приращений в г-м шаге решения; С -значение выходной величины сумматора подынтегральной функции в (г -г 1)-м щаге решения.

Приращение подынтегральной функции (t Ч- 1)-го шага решения (у y((+i)) поступает одновременно на вход узла / накопления приращений, на вход экстраполятора 2 и узла 7 выходных приращений. В зависимости от знаков выходных величин узлов У и 5 в предыдущем шаге решения (С; и С ) узел выходных приращений выходом узла 5 управляющих импульсов и потенциалов подготовлен к выдаче выходного приращения этого же (t-f 1)-го шага решения задачи. Одновременно с поступлением младшего разряда приращения подынтегральной функции (v (/(;-И) на вход 8 блока логических операций на выход блока поступит младший разряд выходного приращения V . Величина выходного приращения будет равна или величине входного приращения, проходящего через узел 7 выходных приращений, или величине поправки, хранящейся в узле 6 выработки и хранения nonpaiBKH и проходящей также через узел 7, или нулю. В течение (I + 1)-го шага решения в блоке логических операций образуется значение подынтегральной функции этого шага ( ) и значение подынтегральной функции на один шаг вперед (С..,. ). Узел 5 управляющих импульсов и потенциалов анализирует приращения с выхода экстраполятора 2 (v (i.)} и управляет выработкой

нужной поправки в узле 6 выработки н хранения поправки. Узел 5 одновременно анализирует знаки выходных величин узлов / и 5 (С;-|.1 и С.,, ) и подготавливает узел 7 выходных приращений к работе в следующем шаге решения. Наличие экстраполятора 2 и су.мматора 3 подынтегральной функции дает возможность получить выходное приращение этого же шага решения без дополнительной экстраполяции и своевременно корректировать выходное приращение, а это значительно повышает точность выполнения логических операций. Код операции, записываемый по входу 9 блока в регистр 4 посредством системы

управляющих импульсов и потенциалов обеспечивает реализацию алгоритма соответствующей операции.

Блок логических операций позволяет с высокой точностью выполнять достаточно щирокий круг операций логического характера: ограничение функции по уровню, выделение экстремального значения функции, определение модуля функции и др.

Предмет изобретения

Блок логических операций для цифровых интегрирующих машин, содержащий узел накопления приращений, первый вход которого 30 соединен с первым в.ходом блока, а выход - с первыми входами сумматора подынтегральной функции, узла управляющих импульсов и потенциалов и узла выработки и хранения поправки, выход которого соединен с первым 35 входом узла выходных приращений, выход которого соединен с выходом устройства, а второй вход - с первым выходом узла управляющих импульсов и потенциалов, второй выход которого подключен ко второму входу узла

Q выработки и хранения поправки, отличающийся тем, что, с целью повыщения точности и расширения функциональных возможностей, в его состав введен экстраполятор, вход которого соединен с первым входом блока и третьим входОМ узла выходных прирашений, первый выход - со вторым входом сумматора поды нтегральной функции, а второй выход - со вторым входом узла управляющих и.мпульсов и потенциалов, третий вход которого подключей к выходу сумматора подынтегральной функции и к третьему входу узла выработки и хранения поправки, третий выход - ко второму входу узла накопления прираи1ений, а четвертый вход - к выходу регистра кода

5 операций, выход которого соединен со вторым входом блока.

J

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения логических операций при решении дифференциальных уравнений | 1980 |

|

SU955081A1 |

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU650085A2 |

| ЭКСТРАПОЛЯТОР ПРИРАЩЕНИЙ ДЛЯ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ Л\АШИНЬГ | 1969 |

|

SU244735A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ЭКСТРЕ/1^АЛЬНОГО ЗНАЧЕНИЯ ФУНКЦИИ -«i-,,. | 1970 |

|

SU264814A1 |

| Цифровой интегратор | 1979 |

|

SU805362A1 |

Даты

1974-02-15—Публикация

1972-01-04—Подача