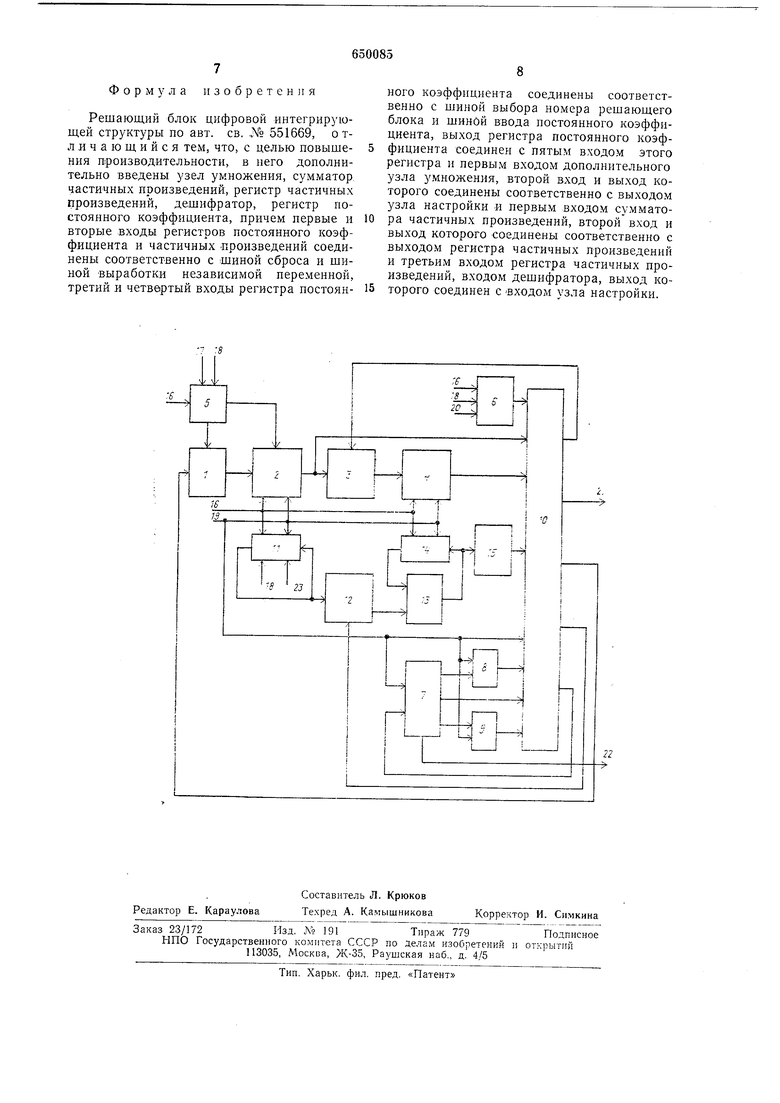

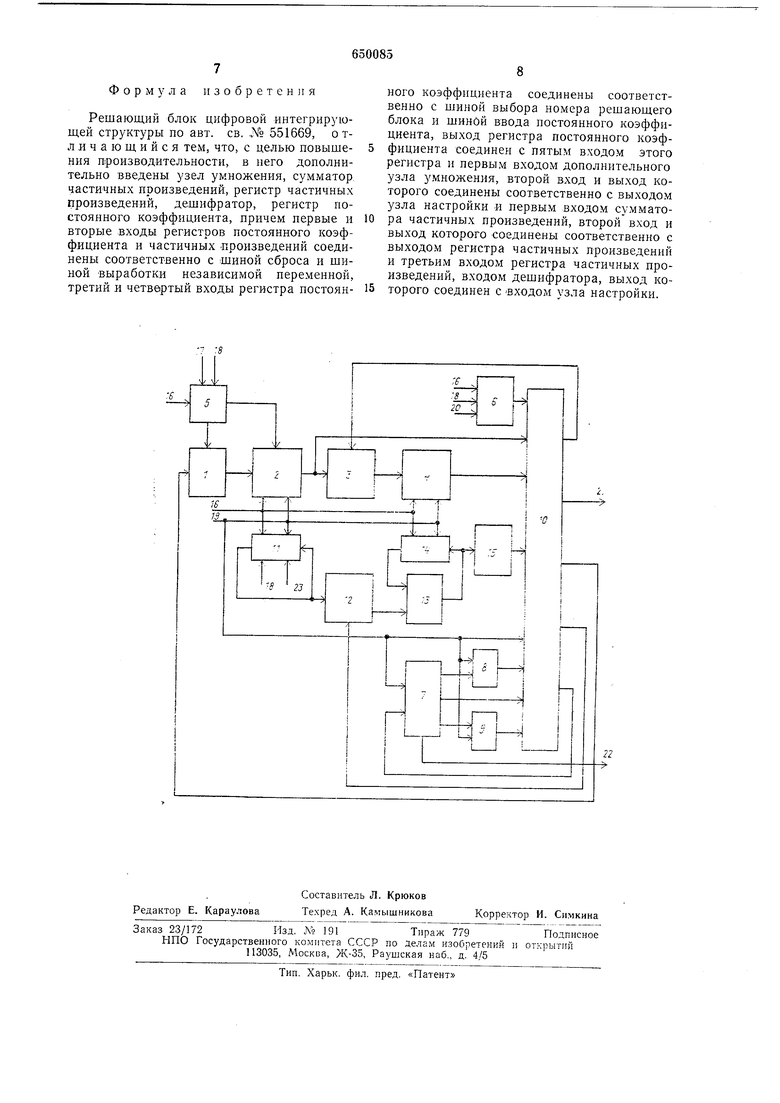

Изобретение относится к области BbimiCлительной техники и предназначено для использования в цифровой интегрирующей структуре. По основному авт. с-в. № 551669 известен решающий блок цифровой интегрирующей структуры. Для такого решающего блока характерна недостаточная производительность. Целью изобретения является ловыщение производительности. Поставленная цель достигается те.м, что в решающий блок дополнительно введены узел умножения, сумматор частичных произведений, регистр частичных ироизведекий, дешифратор, регистр иостоянного коэффициента, причем первые и вторые входы регистров постоянного коэффициента и частичных произведений соединены соответственно с шиной сброса и шиной выработки независимой переменной. Третий и четвертый входы регистра постоянного коэффициента соеди1 ены соответственно с шиной выбора номера решающего блока и с шиной ввода иостоянного коэффициента. Выход регистра иостоянного коэффициента соединен с пятым входом этого регистра и первым входом дополнительного узла умножения, второй вход и выход которого соединены соответственно с выходом узла настройки и первым входом сумматора частичных произведений, BTOpoii вход н выход которого соединены соотзетсзенно с выходом решстра частичных произведенн; и третьим входом регистра частичных произведений, входом дешифратора, зыход которого соединен с входом узла настрочки. На чертеже показан: структурная схема предлагаемого блолл. Решающий блок содержит сумматор / входных приран1ен.::й, узел 2 образования подынтегральной функипл, узел 3 умножения, узел 4 образования остатка интеграла, узел 5 масштабировлния, регистр 6 хранения кода операций, узел 7 выделения выходных приращений, узел 5 выполнения операции ограничения, узел 9 вьгполнении знаковой функци;, узел W нгстройх. регистр // постоянного коэффиц)нта, узел 12 умножения, сумматор /о -мстичнь х произведений, регистр /- частиччыч произзедсний, дешифратор 15, iii.:i:iy 16 сброса, шину /7 ввода начальных значений, шину IS выбора номера решающего блок, шину 19 выработки незавпсимоП перемгнмой, шя;у 20 занесения кода операцин, выходн} О шину 2J, шину 22 переполнения, шину .26 нзода постоянного коэффициента. Узел 2 состоит из суммлтора подынтсгральной ф нкци;..|. :ыходы которого через

регистр .подынтегральной функции и элемент задержки соединены со своими входами, узел - из сумматора остатка интеграла, выходы которого через регистр остатка интеграла и элемент задержки соединены со своими входами.

Рассмотрим работу решающего блока во всех режимах.

В режиме цифрового интегрирования ио шине /7 через узел 5 в узел 2 заносятся начальные данные, а s регистр 6 записывается соответствующий код. Структура решающего блока настраивается на выиолнение операции численного интегрирования.

Приращения подынтегральной функции в виде постоянных сигналов «+1 или «-1 до ши.не 17 через узел 5 поступают на вход сумматора /. Полученная в сумматоре / сумма приращений поступает иа вход узла 2, где происходит ее суммирование со значением подынтегральной функции предыдущего щага решения, и полученное новое значение подынтегральной функции поступает на вход узла 3. В узле 3 образуется произведение значения подынтегральной функции на приращение независимой переменной, которое по щине 19 через узел 10 поступает на второй вход узла 3.

В узле 4 происходит сложение полученного после узла 3 некзантованного приращения интеграла с остатком интеграла предыдущего щага и происходит образование иового значения остатка интеграла, а полученная сумма постуиает через узел 10 в узел 7, где ио сигналу, поступающему по щиие 19, происходит выделение квантованного приращения интеграла, которое через узел 10 поступает на шину 21.

В режиме суммирования в узел 2 записывается нуль, а в регистр 6 записывается соответствующий код. Структура рещаюи1,его блока настраивается на выполнение операции суммиро,вания.

Приращения подынтегральной функции ио щине 17 через узел 5 поступают на вход сумматора /. Полученная в сумматоре / сумма приращений запоминается в узле 2 и поступает через узел 10 на вход узла 7. Узел 7 в режиме суммирования производит анализ модуля я знака поступающего значения суммы приращений и выдачу приращений со знаком суммы приращений (если значение суммы приращений не равно 0) через узел 10 на щину 21 с обратным знаком - на вход сумматора /, где они складываются с приращениями подынтегральной функции.

В режиме операции ограничения но щине 17 через узел 5 в узел 2 заносятся начальные данные, а по щине 20 в регистр 6 - соответствующий код. Структура решающего блока настраивается на выполнение операции ограничения.

Приращения подынтегральной функции по шине /7 через узел 5 поступают на вход

сумматора /. Полученная в сумматоре / сумма приращений поступает в узел 2, где она суммируется со значением подынтегральной функции предыдущего шага li полученное новое значение подынтегральной функции через узел W поступает ,в узел 7 выделения выходных приращений, который анализирует модуль и знак поступившего числа и в случае положительного его значения выдает приращения на вход узла 8, на второй вход которого поступает приращение машинной переменной с шины 19. Узел 8 пропускает приращения машинной переменной через узел 10 на шину 21 в том случае, если с выхода узла 7 на вход узла 8 поступают приращения, т. е. когда значение подынтегральной функции положительно. В случае отрицательного значения подынтегральной функции узел 7 не выдает приращения, и узел 8 не проиускает приращения машииной переменной на шину 21.

В режиме функции знака по шине 17 через узел 5 в узел 2 заносятся начальные данные, а но шине 20 в регистр 6 - соответствующий код. Структура решающего блока настраивается на выполнение функции знака.

Приращения подынтегральной функции по шине 17 через узел 5 поступают на вход сумматора ./. Полученная в сумматоре 1 сумма Ириращений иоступает в узел 2, где она су.ммируется со значением подынтегральной функции предыдущего шага, и полученное новое значение иодынтегральной функции через узел 10 иоступает в узел 7, который анализирует знак и модуль поступившего числа и выдает приращения со знаком постуиившего значения подынтегральной функции на вход узла 9, на второй вход которого поступает приращение машинной переменной с шины 19. Узел 9 пропускает приращения мащинной переменной через узел 10 на щцну 21 без из.менения в случае, если значение подынтегральной функции положительно. В случае отрицательного значения подынтегральной функции узел 9 производит переадресацию приращений машинной переменной, т. е. положительное приращение поступает по отрицательной шине, а отрицательное по положительной.

В режиме цифрового ннтегрирования с одновременным умножением на постоянный коэффициент меиьще едииицы по щине 17 через узел 5 в узел 2 заносятся начальные данные, по щине 23 В регистр // заносится постоянный коэффициент, а по шнне 20 в регистр 6 - соответствующий код.

Приращения подынтегральной функции поступают по ши«е 17 через узел 5 на вход сумматора /. Полученная в сумматоре / сумма приращений поступает в узел 2, где она суммируется со значением подынтегральной функции предыдущего щага, и полученное новое значение подынтегральной

функции поступает на вход узла 3. В узле 3 образуется произведение значения подынтегральной функции на приращение независимой неременной, которое по шине 19 через узел 10 поступает на второй вход узла 3.

В узле 4 осундествляется сложение полученного .после узла 3 неквантованного приращения интеграла с остатком интеграла предыдущего щага и происходит образование нового значения остатка интеграла, а полученная сумма поступает через узел W в узел 7, где по .сигналу, поступающему по шине 19, выделяется квантованное приращенне интеграла, которое через узел 10 проходит на вход узла 12, на второй вход которого поступает значение постоянного коэффициента из регистра И.

В сумматоре 13 происходит суммирование полученного после узла 12 значения приращения интеграла, умноженного на коэффициент, с частичным нроизведеннем приращения интеграла на коэффициент, которое ноступает из регистра 14. Полученное в сумматоре 13 новое значение частичного произведения поступает на вход регистра

14и на вход узла 15, который анализирует знаковые разряды поступившего числа и в случае их нереполнения выдает квант произведения.

Квант .произведения постоянного коэффициента на приращение интеграла из узла

15через узел 10 поступает на шину 21.

В режиме умножения на коэффициент, больший единицы, в узел 2 записывается нуль, в регистр // - величина, обратная коэффициенту, а в регистр 6 - соответствуюший код.

Приращения подынтегральной функции по шине 17 через узел 5 поступают на вход сумматора 1. Полученная в сумматоре / сумма приращений запоминается в узле 2 и поступает через узел 10 на вход узла 7. Узел 7 в этом режиме производит анализ модуля и знака поступающего значения суммы приращений, и если значение суммы приращений не равно нулю, то узел 7 выдает через узел 10 на шину 21 приращения со знаком, соответствующим значению суммы приращений и одновременно это ириращение подается в узел 12. Оно поступает на шину 21 и в узел 12 до тех нор, пока сумма частичных произведений в сумматоре 13 не ста.нет равной 1,0. bio так как зиаченне регистра // равно IIK, где /С - значенне коэффициента, то сумма частичных произведений становится равной 1,0 после того, как узел 7 выдает на вход узла 12 и на шину 21 /С приращений. Когда значение суммы частичных произведений становится равным единице, ззел 15 выдает одно приращение (квант произведения) со знаком, обратным выходному приращению. Это приращение ноступает через узел 10 и сумматор / в узел 2, где вычитается из значения суммы приращений. Если в этом случае значение суммы приращений становится равным нулю, то узел 7, проанализировав вновь значение суммы приращений, перестает выдавать вы.ходные приращения. Таким образом, в данном режиме за один шаг решения решающий блок вместо одного приращения выдает /С приращений, т. е. производит умножение входного приращения на коэффициент /С.

В режи.ме численного интегрирования с одновременным умножением на постоянный коэффициент больше единицы в узел 2 заносятся начальные данные, в регистр //- величина, обратная коэффициенту, а в регистр 6 - соответствующий код.

Приращения подынтегральной функции но шине 17 через узел 5 поступают на вход сумматора /. Полученная в сумматоре / сумма приращений поступает на вход узла 2, где проис.ходит ее суммирование со значением подынтегральной функцни предыдущего шага решення, и полученное новое значение подынтегральной функции поступает на вход узла 3. В узле 3 образуется произведение значения подынтегральной функции на приращение независимой переменной, которое по щине 19 через узел 10 поступает на второй вход узла 3.

В узле 4 осуидествляется сложение полученного после узла 3 неквантованного нрнращения интеграла с остатком иитеграла предыдущего щага и происходит образование нового значения остатка интеграла, а полученная сумма поступает через узел W в узел 7. В случае, если значения величины, поступившей на вход узла 7, будут 1,0, то узел 7 но сигналу, ноступающему по шине 19, выдает квантованное приращение интеграла, которое через узел /О иоступает на щину 21 выхода рещающего блока и одновременно через узел 10 на вход узла 12, на второй вход которого поступает коэффициент из регистра 11. Это приращение на шине 21 и на входе узла 12 удержнвается в течение /С итераций, т. е. пока сумма частичных произведений в сумматоре 13 не станет равной 1,0. Тогда узел 15 анализа частичных произведений выдает одно приращение, которое через узел 10 поступает на в.ход узла 7 на установку его в исходное состояние, и узел 7 перестает выдавать приращения. Таким образом, в этом режиме в течение одного шага решения }зел 7 вместо одного приращения интеграла выдает на шину 21 выхода решающего блока Л приращений, т. е. получаемое в процессе пнтегрирования приращение интеграла умножается на коэффициент Д .

Предлагаемый блок повышает быстродействие при незначительном увеличении оборудования.

Формула изобретения

Решающий блок цифровой интегрирующей структуры по авт. св. .N° 551669, о тллчающийся тем, что, с целью повышения производительности, в него дополнительно введены узел умножения, сумматор, частичных произведений, регистр частичных произведений, дешифратор, регистр постоянного коэффициента, причем первые и вторые входы регистров постоянного коэффициента и частичных .произведений соединены соответственно с щиной сброса и шиной выработки независимой переменной, третий и четвертый входы регистра постоянного коэффициента соединены соответственно с шиной выбора номера решающего блока и шиной ввода постоянного коэффициента, выход регистра постоянного коэффициента соединен с пятым входом этого регистра и первым входом дополнительного узла умножения, второй вход и выход которого соединены соответственно с выходом узла настройки и первым входом сумматора частичных произведений, второй вход и выход которого соединены соответственно с выходом регистра частичных произведений и третьим входом регистра частичных произведений, входом дешифратора, выход которого соединен с входом узла настройки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Решающий блок цифровой интегрирующей структуры | 1976 |

|

SU600573A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

Авторы

Даты

1979-02-28—Публикация

1976-07-19—Подача