1

Изобретение относится к области автоматики и ко,нтрольио-измерительной техники и может применяться для контроля интегральных схем.

Известно устройство для контроля интетральных схем, содержащее цифровую вычислительную машину, соединенную с блоком ввода и с первым входом блока управления, второй вход которого соединен с выходом буферного блока, а выход - со входами блока опорных воздействий, формирователя сигналов, генератора, блока синхронизирующих сигналов, цифрового вольтметра и входами анализаторов, в каждо.м из которых выход формирователя испытательных воздействий и выход компаратора подключен к выводу колтролируемой интегральной схемы, второй выход колшаратора - к первому входу буферного блока, и второму входу формирователя сигналов, первый вход коммутатора испытательных воздействий и коммутатора граничных воздействий - к выходу блока спорных воздействий, второй их вход - к выходу генератора, а первый вход формирователя ионытатель.ных воздействий и компаратора - к первому выходу блока синхронизирующих сигналов, подключенного вторым выходом ко второму входу генератора и второму входу буферного блока.

Однако это устройство не обеспечивает одловре.менно статический, динамический и функциональный контроль интегралы ых схем и приводит к ложным ошибкам контроля больших интегральных схем.

С целью расширения области применения устройства для контроля интегральных схем в каждый анализатор введены последовательно соединенные регистр тестовых переходов, дешифратор и коммутатор перестройки, выход которого подключен к третьему входу коммутатора иснытательных воздействий, к третьему входу коммутатора граничных воздействий ко второму входу формирователя испытательных воздействий, третнй вход которого соединен с выходом коммутатора испытательных воздействий, и ко второму входу компаратора, третий вход которого соединен с выходом коммутатора граничных воздействий.

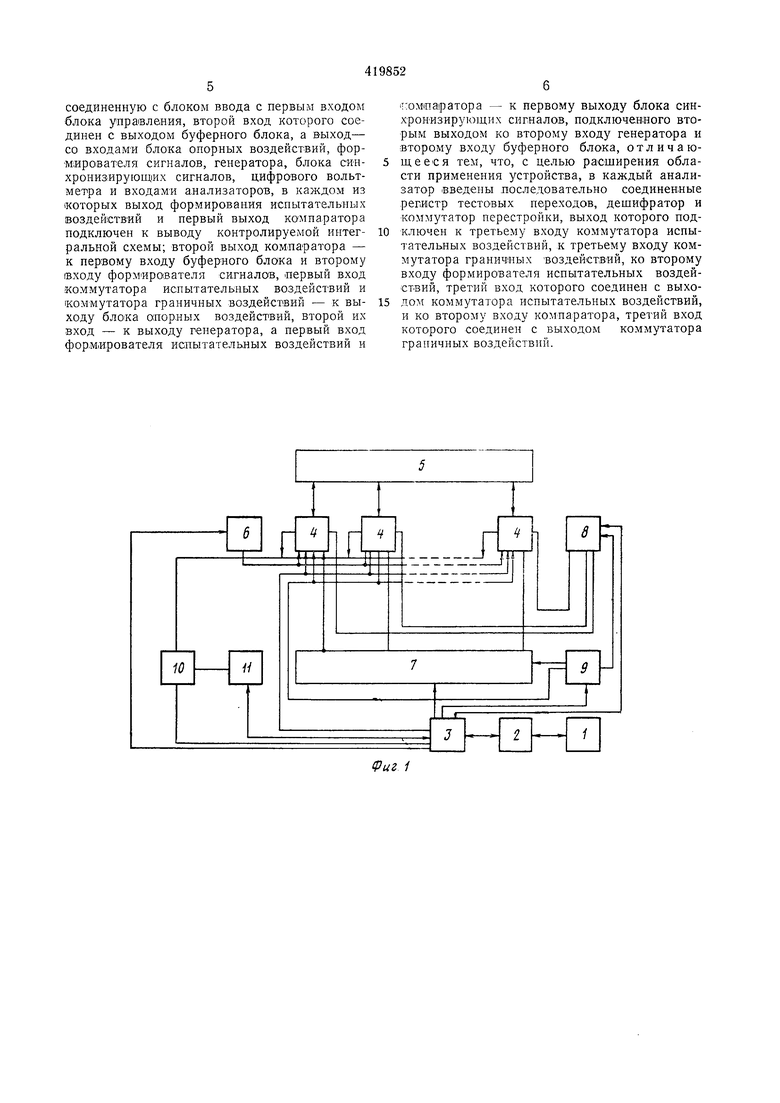

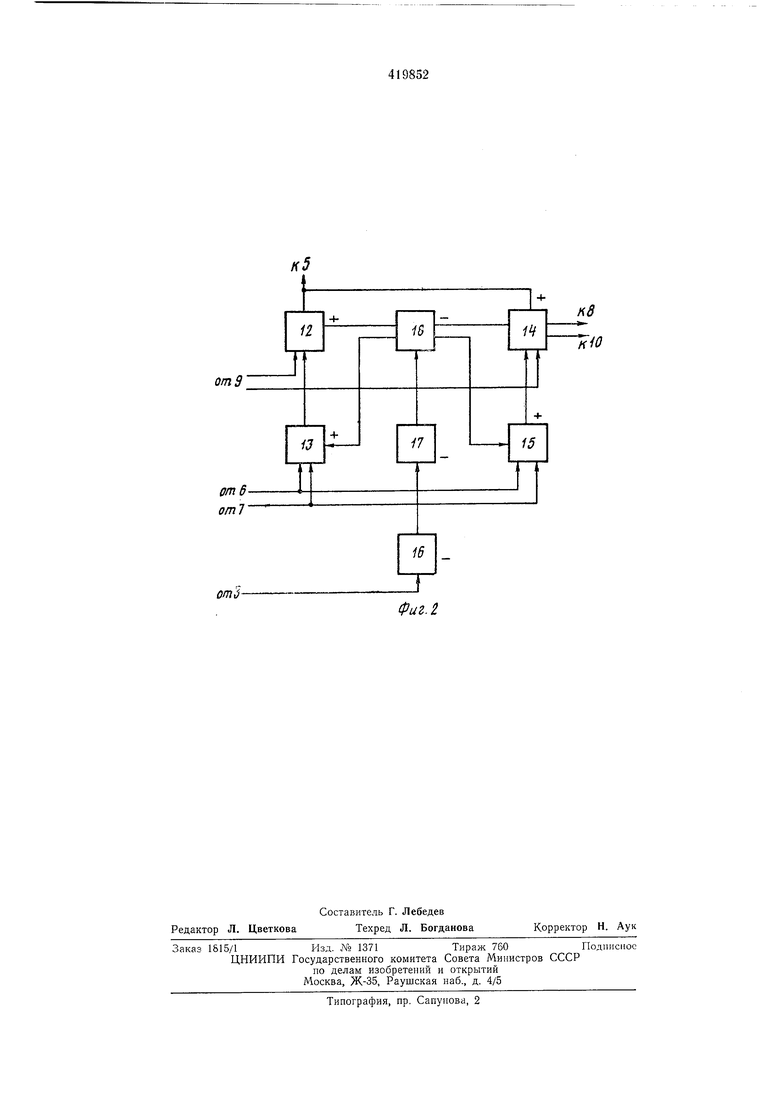

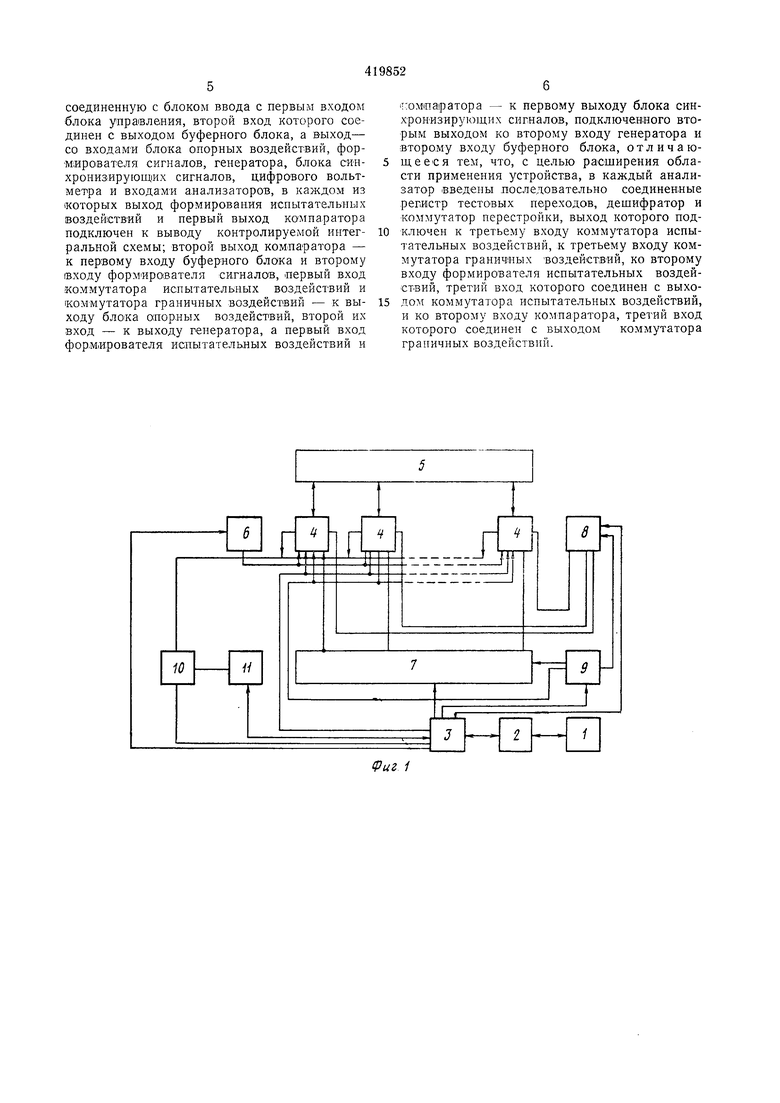

На фиг. 1-2 приведены схемы предлагаемого устройства. На фиг. 1 - блок-схема yciройства для контроля интегральных схем; на фиг. 2 - структурная схема блока контроля.

Устройство содержит блок ввода 1, цифровую вычислительную машину 2, блок управления 3, анализаторы 4, соединенные с выводами контролируемой интегральной схемы 5, блок опорных воздействий 6, генератор 7, буферный блок 8, блок синхронизирующих сигналов 9, формирователь сигналов 10 и цифровой вольтметр 11.

Анализатор 4 содержит формирователь испытательных воздействий 12. коммутатор испытательных воздействий 13, компаратор 14, коммутгтор гргничлых воздейстБий 15, регистр тестовых переходов 16, детнифратор 17 и коммутатор перестройки 18.

Устройство работает следующим образом.

Блок 1 нредпазначен для ввода программ контроля в цифровую вычислительную машину 2 и вывода из иее результатов контроля. Цифровая вычислительная машина 2 осуществляет об:,;ен информацией посредством блока управления 3, в результате чего синтезируются из независимых блоков контрольноиснытател Д1ые схемы для каждого теста. Анализаторы 4 служат для задания последовательностей испытателы ых воздействий на выводы контролируемой схемы 5, когггроля параметра в заданном испытательном режиме и выдачи результатов контроля.

Блок опорных воздействий 6 преобразует цифровые коды в аналоговые опорные испытательпые и граничные воздействия, которые поступают на анализаторы 4.

Управляющие тестовыми переходами двоичные последовательности на каждый анализатор 4 1выдают:ся генератором 7.

Результаты контроля поступают с анализаторов 4 на буферный блок 8, который предназначен для согласования по длинам слов и быстродействию выходов анализаторов 4 и цифровой вычислительной машины 2.

Блок синхронизирую.-.их сигналов 9 предназначен для синхронизации формирования испытательных воздействий иа выводах кон;ролируемой интегральной схемы 5 и стрема информации о контролируемых нараметрах в нрограММируемые моменты времени относительно начала тестов. Форм:ирователь сигналов 10 согласует параметры Сигналов и измерительных цепей со входом цифрового вольтметра 11. Все устройства и блоки по режимам работы являются программно-управляемыми от цифровой вычислительной машииы.

В состав каждого анализатора 4 входит: формирователь испытательных воздейст-внй 12, формирующий носледовательноста- испытательных воздействий на выводе интегральной схемы 5 из двоичных последовательностей опорных испытательных воздействий, коммутатор испытательных воздействий 13, компаратор 14, сравнивающий последовательности контролируемых нараметров, снимаемых с выводо:в интегральной схемы 5, с двоичными опорными граничными последовательностями и выдающ,ий результаты контроля, коммутатор граничных воздействий 15, регистр тестовых переходов 16 для запоминания и хранения кодов тестовых переходов, дешифратор 17 и коммутатор перестройки 18, предназначенный для настройки на формирование и контроль нараметров в соответствии с кодом тестового перехода.

Испытательно-контрольнаяинформация

вводится посредством блока ввода 1 в цифровую вычислительную машину 2. В соответствии с командами, получаемыми от цифровой вычисл.ительной машины 2, блок управления 3 сннтезирует нз независи.мых блоков испытательно-коитрольные схемы длл последовательности контрольных тестов. у нализаторы 4 параллельно формнруют двоичные последовательности иснытательных воздействий на выводы и;нтегралыюй схемы 5 из онорных испытательных воздействий и коитролируют параметры на этих выводах но опорным граничным воздействиям, которые поступают от блока опорных воздействий 6. Управление формированием носледователы-юстей двоичиых

иснытательных и граничных воздействий осуществляется генератором 7.

Результаты испытаний накапливаются буферным блоКом 8. Согласование во времени моментов и длительностей формирования иснытательных воздействий и съема информации о контролируемых нараметрах осуществляется блоком синхронизирующих сигналов 9. В режиме измерения анализатор 4 в соответствии с программой подключает к выводу интегральной схемы 5 через формирователь сигналов 10 вход цифрового вольтметра П.

Требуемый испытательный режим на выводе интегральной схемы 5 обеснечивается формирователем испытательных воздействий 12

из опорного испытательного воздействия, выбранного коммутатором иснытательных воздействий 13. Комнаратор 14 сравнивает контролируемый нараметр в заданном испытательном режиме с выбранным коммутатором

граничных воздействнй 15 граничным значением. Регистр тестовых переходов 16 через денлнфратор 17 унравляет коммутатором перестройки 18.

Коммутатор нерестройки 18 настраивает

коммутатор испытательных воздействий 13 на выбор по тестам одного из двух опорных испытательных воздейств.ий; а коммутатор граничных воздействнй 15 - одного из двух граНИЧТ1ЫХ воздействий в соответствии с двоичными носледовательностями, ностунающ.ими от генератора 7. При изменении величины или характера иснытательного или граничного воздействия в двоичиых носледовательностях воздействий для следующего теста цифровая

вычислительная мащина 2 в данном тесте через блок управления 3 засылает код нового тестового перехода.

По 0:кончании одного или нескольких тестов буферный блок 8 через блок управления 3 передает результаты испытаний в цифровую вычислительную мащину 2, которая обрабатывает их, продолжает управлять контролем, корректирует испытательный режим или выдает обработанные результаты.

предмет изобретения

Устройство для контроля интегральных схе.м, содержащее вычислительную мащину,

соединенную с блоком ввода с первым входом блока управления, второй вход которого соединен с выходом буферного блока, а выход- со входамИ блока опорных воздействий, формирователя сигналов, генератора, блока синхронизирующих сигналов, цифрового вольтметра и входами анализаторов, в каждом из которых выход формирования испытательных воздействий и первый выход компаратора подключен к выводу контролируемой интегральной схемы; второй выход компаратора - к первому входу буферного блока и второму (ВХОДУ формирователя сигналов, первый вход коммутатора испытательных воздействий и коммутатора граничных воздействий - к выходу блока опорных воздействий, второй их вход - к выходу генератора, а первый вход формирователя испытательных воздействий и

1 :ом па1ратора - к первому выходу блока синхронизирующих сигналов, подключенного вторым выходом ко второму входу генератора и второму входу буферного блока, отличающееся тем, что, с целью расширения области применения устройства, в каждый анализатор введены последовательно соединенные регистр тестовых переходов, дешифратор и коммутатор перестройки, выход которого подключен к третьему входу коммутатора испытательных воздействий, к третьему входу коммутатора граничных воздействий, ко второму входу формирователя испытательных воздействий, третий вход которого соединен с выходом коммутатора испытательных воздействий, и ко второму входу компаратора, третий вход которого соединен с выходом коммутатора граничных воздействий.

от 9

от

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Система для комплексного контроля интегральных схем | 1972 |

|

SU437988A1 |

| Устройство для контроля и измерения параметров | 1980 |

|

SU947833A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЛЕКС КОНТРОЛЯ И ДИАГНОСТИКИ (ВАРИАНТЫ) | 2003 |

|

RU2257604C2 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для проверки функциональных блоков | 1980 |

|

SU1008745A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

Авторы

Даты

1974-03-15—Публикация

1971-09-24—Подача