I

Изобретение относится к контрольно-измерительной технике, в частности к технике контроля параметров интегральных схем.

Pi3BecTHbi системы для комплексного контроля интегральных схем, содержащие унравляюн ую вычислительную машину, комплект устройств ввода-вывода, блок сопряжения, блок управления, блок цифро-аналоговых преобразователей, блоки статических испытательных воздействий и измерения статических параметров, апалого-цифровой преобразователь, коммутационную матрицу постояппого тока, контактирующее устройство, блок согласования и распределения выводов контролируемой интегральной схемы, блок формирователей, блок компараторов, блок накопления результатов, коаксиальный многоканальный ком.мутатор, преобразователь временной параметрннапряжение, генератор слов, комплект задающих гелераторов и коммутатор задающих сигналов.

Известные устройства имеют ограниченные возможности программирования формы тестовых последовательностей сигналов.

Цель изобретения - расширение возможностей программирования.

Эта цель достигается тем, что между выходами комплекта задающих генераторов и входами коммутатора задающих сигналов включены последовательно соединенные коммутатор объединения задающих сигналов и блок N-входовых схе.м цифрового или аналогового суммирования, нричем унравляющий вход коммутатора объединения задающих сигналов нодсоединен к выходу блока управления.

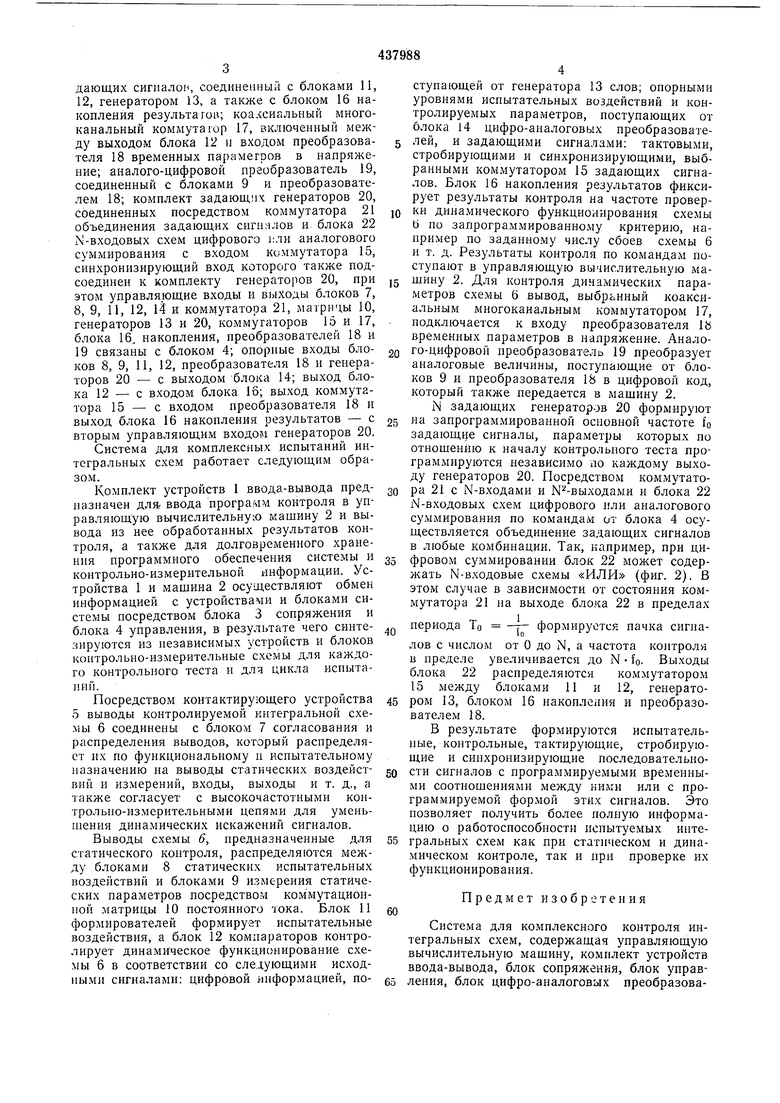

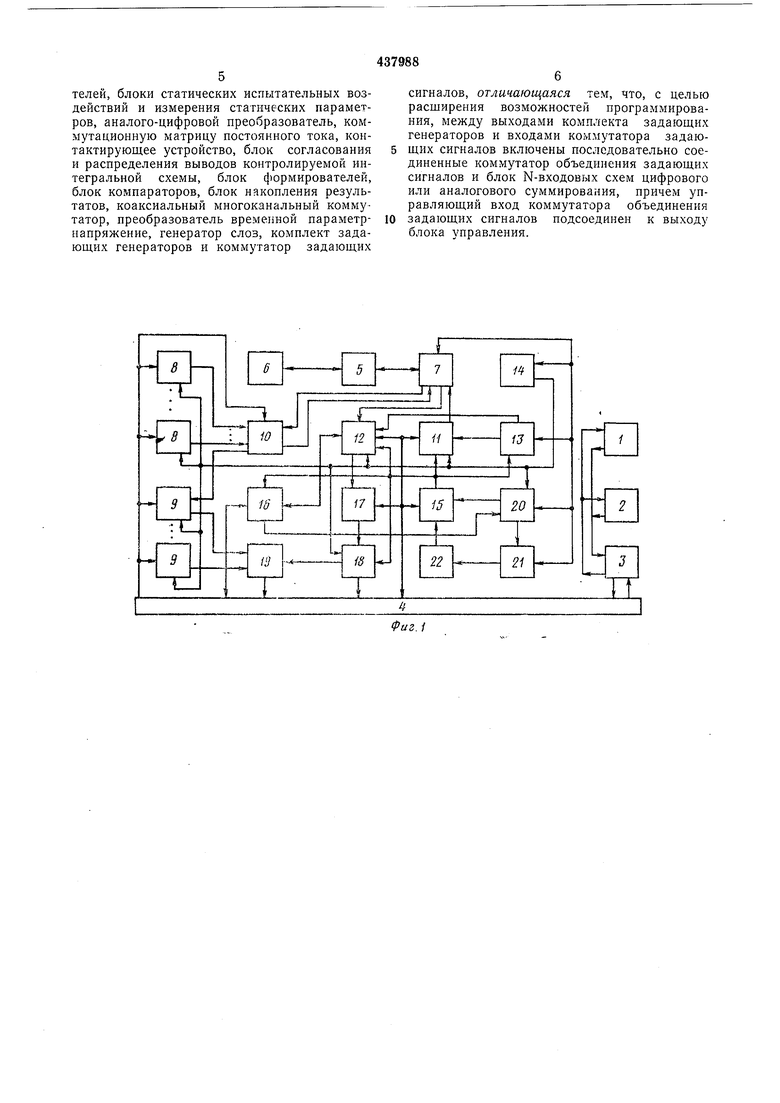

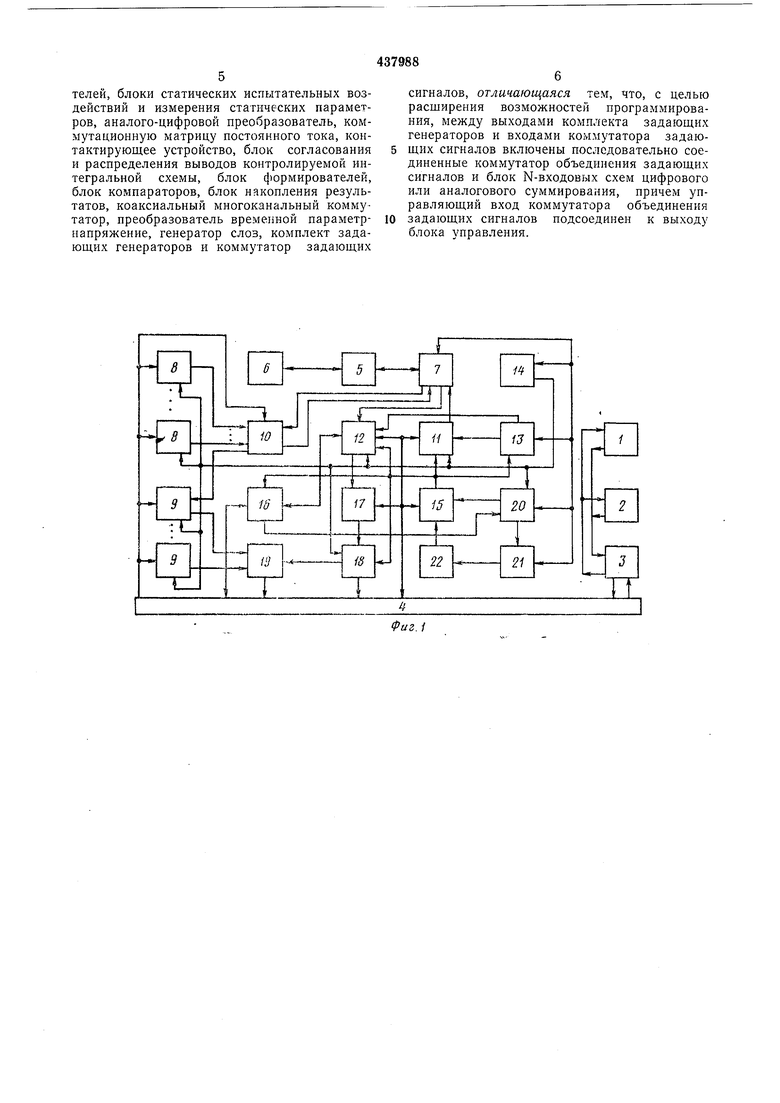

Иа фиг. 1 изображена блок-схема системы для комплексного контроля интегральных схем; на фиг. 2 - блок-схема одного варианта коммутатора объединения задающих сигналов и блока N-входовых схем цифрового суммирования.

Система для комплексного контроля интегральных схем содержит комплект устройств 1 ввода, вывода и долговременного хранения контрольно-измерительной информации, управляющую вычислительную манщну 2, соединенные посредством блока 3 сопряжения с блоком 4 управления; контактирующее устройство 5 для иодключения коитролируемой интегральной схемы 6 к блоку 7 согласования и распределепия выводов схемы 6, соединеииому с блоками 8 статических испытательных воздействий и блоками 9 измерения статических пара.етров посредством коммутационной матрицы 10 ностоянного тока, а также с блоком 11 формирователей и блоком 12 компараторов, которые соедипеиы с генератором 13 слов; блок 14 цифро-аналоговых преобразователей; коммутатор 15 задающих сигиалои, соединенный с блоками 11, 12, генератором 13, а также с блоком 16 накопления результатов; коаксиальный многоканальный коммутатор 17, включенный выходом блока 12 и входом преобразователя 18 временных параметров в напряжение; аналого-цифровой преобразователь 19, соединенный с блоками 9 и преобразователем 18; комплект задающих генераторов 20, соединенных посредством коммутатора 21 объединения задающих сигналов и. блока 22 N-входовых схем цифрового 1;ли аналогового суммирования с входом коммутатора 15, синхронизирующий вход которого также подсоединен к комплекту генераторов 20, при этом управляющие входы и в))1Ходы блоков 7, 8, 9, 11, 12, 14 и коммутатора 21, матрицы 10, генераторов 13 и 20, коммутаторов 15 и 17, блока 16, накопления, преобразователей 18 и 19 связаны с блоком 4; опорные входы блоков 8, 9, 11, 12, преобразователя 18 и генераторов 20 - с выходом блока 14; выход блока 12 - с входом блока 16; выход коммутатора 15 - с входом преобразователя 18 и выход блока 16 накопления результатов - с вторым управляющим входом генераторов 20.

Система для комплексных испытаний интегральных схем работает следующим образом.

Комплект устройств 1 ввода-вывода предназначен дляг ввода программ контроля в управляющую вычислительную мащину 2 и вывода из нее обработанных результатов контроля, а также для долговременного хранения программного обеспечения системы и контрольно-измерительной информации. Устройства 1 и машина 2 осуществляют обмен информацией с устройствами и блоками системы посредством блока 3 сопряжения и блока 4 управления, в результате чего синтезируются из независимых устройств и блоков контрольно-измерительные схемы для каждого контрольного теста и для цикла испытаний.

Посредством контактирующего устройства 5 выводы контролируемой интегральной схемы 6 соединены с блоком 7 согласования и распределения выводов, который распределяет их по функциональному н испытательному назначению па выводы статических воздействий и измерений, входы, выходы и т. д., а также согласует с высокочастотными контрольно-измерительными цепями для уменьН1ения динамических искажений сигналов.

Выводы схемы 6, предназначенные для статического контроля, распределяются между блока.ми 8 статических испытательных воздействий и блоками 9 измерения статических параметров посредством коммутационной матрицы 10 постоянного тока. Блок 11 формирователей формирует испытательные воздействия, а блок 12 компараторов контролирует динамическое функционирование схемы 6 в соответствии со следующими исходны.ми сигналами: цифровой информацией, поступающей от генератора 13 слов; опорными уровнями испытательных воздействий и контролируемых параметров, поступающих от блока 14 цифро-аналоговых преобразователей, и задающими сигналами: тактовыми, стробирующими и синхронизирующими, выбранными коммутатором 15 задающих сигналов. Блок 16 накопления результатов фиксирует результаты контроля на частоте проверки динамического функционирования схемы 6 по запрогра.ммированному критерию, например по заданному числу сбоев схемы 6 и т. д. Результаты контроля по командам поступают в управляющую вычислительную машину 2. Для контроля динамических параметров схемы 6 вывод, выбранный коаксиальным многоканальным коммутатором 17, подключается к входу преобразователя 1Ь временных параметров в напряжение. Аналого-цифровой преобразователь 19 преобразует аналоговые величины, поступающие от блоков 9 и преобразователя 18 в цифровой код, который передается Б мащину 2.

N задающих генераторов 20 формируют

5 на запрограммированной основной частоте fo задающие сигналы, параметры которых по отношению к началу контрольного теста программируются независимо по каждому выходу генераторов 20. Посредством коммутатора 21 с N-входами и N -выходами и блока 22 N-входовых схем цифрового пли аналогового су.ммирования по командам от блока 4 осуществляется объединение задающих сигналов в любые комбинации. Так, например, при цифровом суммировании блок 22 может содержать N-входовые схемы «ИЛИ (фиг. 2). В этом случае в зависимости от состояния коммутатора 21 на выходе блока 22 в пределах

периода То -г- формируется пачка сигналов с числом от О до N, а частота контроля в пределе увеличивается до N fo. Выходы блока 22 распределяются коммутатором 15 между блоками II и 12, генератором 13, блоком 16 накопле; ия и преобразователем 18.

В результате формируются испытательные, контрольные, тактирующие, стробирующие и синхронизирующие последовательности сигналов с программируемыми временными соотношениями между ними или с программируемой формой этих сигналов. Это позволяет получить более полную информацию о работоспособности испытуемых интегральных схем как при статическом и динамическом контроле, так и при проверке их функционирования.

Предмет изобретения

Система для ко.мплексного контроля интегральных схем, содержащая управляющую вычислительную мащину, комплект устройств ввода-вывода, блок сопряжения, блок управления, блок цифро-аналоговых преобразователей, блоки статических испытательных воздействий и измерения статических параметров, аналого-цифровой преобразователь, коммутационную матрицу постоянного тока, контактирующее устройство, блок согласования и распределения выводов контролируемой интегральной схемы, блок формирователей, блок компараторов, блок накопления результатов, коаксиальный многоканальный коммутатор, преобразователь време11ной параметрнапряжение, генератор слов, комплект задающих генераторов и коммутатор задающих

сигналов, отличающаяся тем, что, с целью расширения возможностей программирования, между выходами комплекта задающих генераторов и входами коммутатора задающих сигналов включены последовательно соединенные коммутатор объединения задающих сигналов и блок N-входовых схем цифрового или аналогового суммирования, причем управляющий вход коммутатора объединения задающих сигналов подсоединен к выходу блока управления.

Г

in

22 Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| МНОГОКАНАЛЬНЫЙ ИМПУЛЬСНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ | 2024 |

|

RU2838912C1 |

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1971 |

|

SU419852A1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ БИОЛОГИЧЕСКОЙ АКТИВНОСТИ МОЗГА | 1993 |

|

RU2076625C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ГИБРИДНЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2012 |

|

RU2493609C1 |

л/5

L.

I

Фиг. 2.

Авторы

Даты

1974-07-30—Публикация

1972-07-28—Подача