1

Изобретение относится к обласги вычислительной техиики и иредиазначено для исно.чьзования в цифровых вычислительных машинах, использующих форму представления чисел в системе остаточных классов.

Известно арифметическое устройство, содержит два регистра для размещения операндов, комплект таблиц, схемы передачи операндов на комплект таблиц в прямом коде, схемы передачи вычитаемого на комплект таблиц в дополнительном коде, дешифраторы умножения, регистр для храиения выходной ннформации и устройство контроля и определения знака.

Нелдостатками известного устройства являются: необходимость использования искусственной формы представления чисел, иеполное использование диапазона представляемых чисел, певозможпость проведения онераций и над мантиссами, и над знаками чисел.

С целью расширеиия .функциональиых возможиостей и повышения быстродействия устройство дополнительно содержит схему определения знака и управления схемами передач операидов, логическую схему «Р1ЛИ, а в регистры записи операидов и в регистр хране иия результата операции введены дополнительные разряды знака числа, выходы знаковых разрядов регистров записи операпдов соединены со схемой определепия знака и управ2

ления схемой передачи оиераидов, выходы которой подсоединены к схемам передачи операндов и к иерво.му входу схе.мы «ИЛИ, выход схемы «ИЛИ соедннен со знаковым разрядом регистра хранения результата онерации, а второй вход с.чел-ы «ИЛИ соединен с выходом схемы коптро.тя.

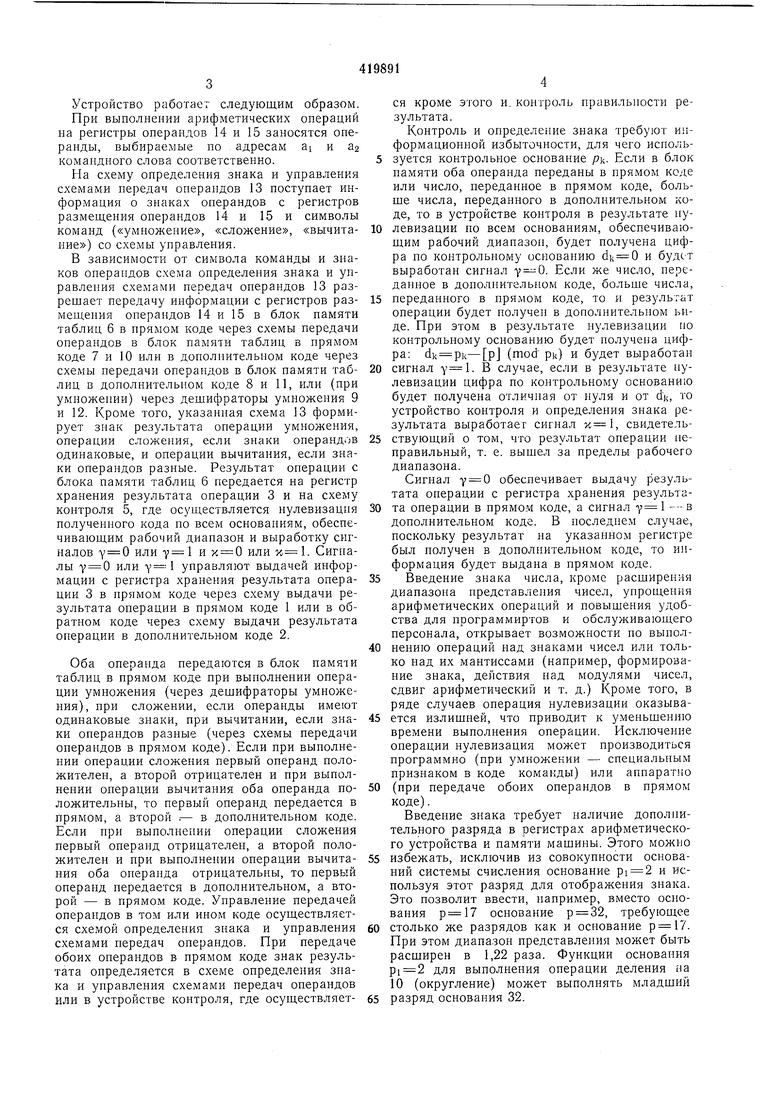

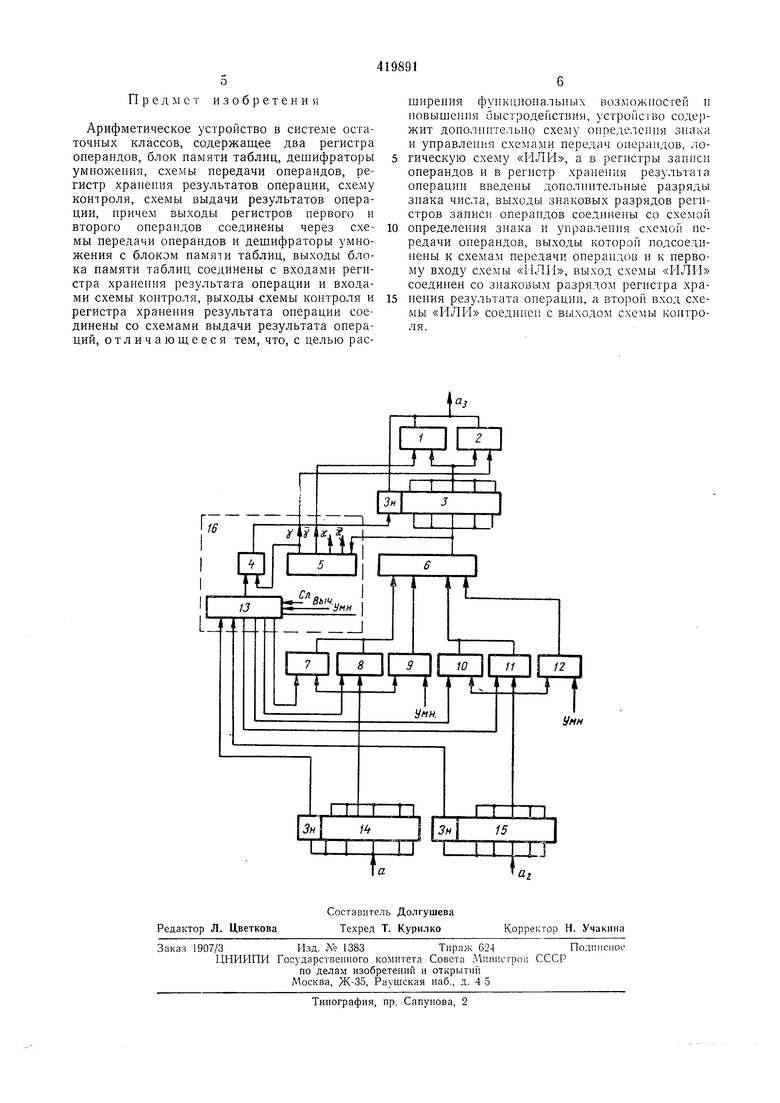

Иа чертеже приведена схема предлагаемого устройства.

Устройство содерл ит: схему выдачи результата операции в прямом коде 1, схему выдачи результата операции в дополпительном кодо 2, регистр хранення результата операции с разрядом знака 3, схе.му «ИЛИ 4, схему контроля 5, блок памяти (комплект таблиц) б, схему передачи первого операнда на гюмплект таблиц в нрямом коде 7, схему передачи первого операида на комплект таблнц в донолнительном коде 8, дешнфратор у.множения (первого операнда) 9, схему передачи второго операнда на ко.мплект таблнц в нрямом коде 10, схе.му передачн второго операнда на комплект таблиц в дополнительном коде 11, дешифратор умнол ения (второго онеранда) 12, схему определення знака н управления схемами передач операндов 13, регнстр первого операида с разрядом знака 14, регпстр второго операнда с разрядом знака 15, схему контроля и определения знака результата 16.

Устройство работает следующим образом.

При выполнении арифметических онераций на регистры операндов 14 и 15 заносятся операнды, выбираемые по адресам ai и а2 командного слова соответственно.

На схему определения знака и управления схемами передач операндов 13 поступает информация о знаках операндов с регистров размещения операндов 14 и 15 и символы команд («умножение, «сложение, «вычитание) со схемы управления.

В зависимости от символа команды и знаков операндов схема онределения знака и управления схемами передач операндов 13 разрешает передачу информации с регистров размещения операндов 14 и 15 в блок памяти таблиц б в прямом коде через схемы передачи операндов в блок памяти таблиц в прямом коде 7 и 10 или в дополнительном коде через схемы передачи операндов в блок памяти таблиц в дополнительном коде 8 и 11, или (при умножении) через дещифраторы умножения 9 и 12. Кроме того, указанная схема 13 формирует знак результата операции умножения, операции сложения, если знаки операндов одинаковые, и операции вычитания, если знаки операндов разные. Результат операции с блока памяти таблиц 6 передается на регистр хранения результата операции 3 и на схему контроля 5, где осуществляется нулевизацпя полученного кода по всем основаниям, обеспечивающим рабочий диапазон и выработку сигналов Y 0 или у и и 0 или . Сигналы или управляют выдачей информации с регистра хранения результата операции 3 в прямом коде через схему выдачи результата операции в прямом коде 1 или в обратном коде через схему выдачи результата операции в дополнительном коде 2.

Оба операнда передаются в блок памяти таблиц в прямом коде при выполнении операции умножения (через дешифраторы умножения), при сложении, если операнды имеют одинаковые знакн, при вычитании, если знаки операндов разные (через схемы передачи операндов в прямом коде). Если при вынолнении операции сложения первый операнд положителен, а второй отрицателен и при выполнении онераций вычитания оба операнда положительны, то первый операнд передается в прямом, а второй .- в дополнительном коде. Если при выполнении операции сложения первый операпд отрицателен, а второй положителен и при выполнении операции вычитания оба операпда отрицательны, то первый операнд передается в дополнительном, а второй - в прямом коде. Управление передачей операндов в том или ином коде осуществляется схемой определения знака и управления схемами передач операндов. При передаче обоих операндов в прямом коде знак результата определяется в схеме определения знака и управления схемами передач операндов или в устройстве контроля, где осуществляется кроме этого и. контроль правильности результата.

Контроль н определение знака требуют информационной избыточности, для чего используется контрольное основание pk. Если в блок намяти оба операнда переданы в прямом коде или число, переданное в прямом коде, больше числа, переданного в дополнительном коде, то в устройстве контроля в результате ну10 левизации по всем основаниям, обеспечивающим рабочий диапазон, будет получена цифра по контрольпому основанию и будет выработан сигнал . Если же число, нереданное в донолнительном коде, больше числа,

5 переданного в прямом коде, то и результат операции будет получен в дополнительном ьпде. При этом в результате нулевизации по контрольному основанию будет получена цифра: dk (mod pk) и будет выработан

0 сигнал В случае, если в результате нулевизации цифра по контрольному основанию будет нолучена отличная от нуля и от dk, то устройство контроля и определения знака результата выработает сигнал , свидетельствующий о том, что результат операции неправильный, т. е. вышел за пределы рабочего диапазона.

Сигнал 7 0 обеспечивает выдачу 15езультата онераций с регистра хранения результата операции в прямом коде, а сигнал ---в дополнительном коде. В носледнем случае, поскольку результат на указанном регистре был получен в дополнительном коде, то информация будет выдана в прямом коде.

5 Введение знака числа, кроме расширения диапазона представления чисел, упрощения арифметических операций и повышения удобства для программиртов и обслуживающего персонала, открывает возможности по выполнению операций над знаками чисел или только над их мантиссами (например, формирование знака, действия над модулями чисел, сдвиг арифметический и т. д.) Кроме того, в ряде случаев операция нулевизации оказывается излишней, что приводит к уменьшению времени выполнения операции. Исключение операции нулевизация может производиться программно (при умножении - специальным признаком в коде команды) или аппаратно

0 (при передаче обоих операндов в прямом коде).

Введение знака требует наличие дополнительного разряда в регистрах арифметического устройства и памяти машины. Этого можно

5 избежать, исключив из совокупности оснований системы счисления основание н используя этот разряд для отображения знака. Это позволит ввести, например, вместо основания основание р 32, требующее

0 столько же разрядов как и основание . При этом диапазон представления может быть расширен в 1,22 раза. Функции основания для выполнения операции деления на 10 (округление) может выполнять младший

разряд основания 32.

Предмет изобретения

Арифметическое устройство в системе остаточных классов, содержащее два регистра операндов, блок памяти таблиц, дешифраторы умножения, схемы передачи операндов, регистр храпения результатов операции, схему контроля, схемы выдачи результатов операции, причем выходы регистров первого и второго операндов соединены через схемы передачи операндов и дешифраторы умножения с блоком памяти таблиц, выходы блока памяти таблиц соединены с входами регнстра хранения результата операции и входами схемы контроля, выходы схемы контроля и регистра хранения результата операции соединены со схемами выдачи результата операций, отличающееся тем, что, с целью расширения функциональных возмож 1остей н повышения быстродействия, устройсгво содержит донолннтельно схему определения знака и управления схемами передач операндов, логическую схему «ИЛИ, а в регистры записи операндов и в регистр хранения результата операции введеиы дополнительные разряды знака числа, выходы знаковых разрядов регистров записи операндов соединены со cxeMoii

определения знака и управления схелюи передачи операндов, выходы которой подсоединены к схемам передачи операпдов и к первому входу схемы «ИЛИ, выход схемы «ИЛИ соединен со знаковым разрядом регистра хранения результата операции, а второй вход схемы «ИЛИ соединен с выходом схемы контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

| Арифметическое устройство в системе остаточных классов | 1979 |

|

SU857992A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Арифметическое устройство в системе остаточных классов | 1980 |

|

SU881745A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО С КОНТРОЛЕМ И КОРРЕКЦИЕЙ ОШИБОК | 1973 |

|

SU387362A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Даты

1974-03-15—Публикация

1972-04-06—Подача