мации. При обм-ене разными ма-ссивами инфо.рмации с ОЗУ уменьшается эффективность использования ОЗУ.

Другой недостаток системы заключается в том, что При чтении информации из ОЗУ в каналы устройство для -буферизации информации от каналов ввода-вывода выставляет запросы к логическим блокам памяти ло каждому запросу от канала. Информащия, считанная из ОЗУ, сохраняется в буферной памяти лишь на время, необходимое для передачи ее в канал. Накопления в буферной памяти не осуществляется. Поэтому при каждом запросе канала чтение информации всегда осуществляется из ОЗУ, что приводит к снижению быстродействия вычислительной системы.

Третьим недостатком является то, что обращения к четырем логическим блокам ОЗУ осуществляется от четырех каналов ввода-вывода, каждый из которых обращается к ОЗУ по своему адресу. При этом необходимо для каждого канала опрашивать матрицу адресов, что приводит к повышению числа конфликтов по матрице адресов между обращениями каналов и процессора.

Цель изобретения-повыщение быстродействия системьг.

Поставленная- цель достигается- тем, что в вычислительную систему введеньг триггер запроса адресов и блок формирования запросов. Выход триггера запро-са адресов соединен с вторым входом матрицы адресов, выходом подключенной к первому входу триггера запроса адресов, второй вход триггера запроса адресов - с третьим выходом блока о-бработки запросов, четвертым выходом подключенного к первому входу блока формирования запросов, второй вход которого -соединен- с четвертым выходом блока управления и четвертым входом буферного регистра информации. Выход блока формирования запросов соединен с пятым входом блока управления, третьи -выходы каналов ввода-вывода - с третьим и четвертым входами блока приоритета, а четвертые выходы каналов ввода-вывода -с третьим входом блока обработки запросов.

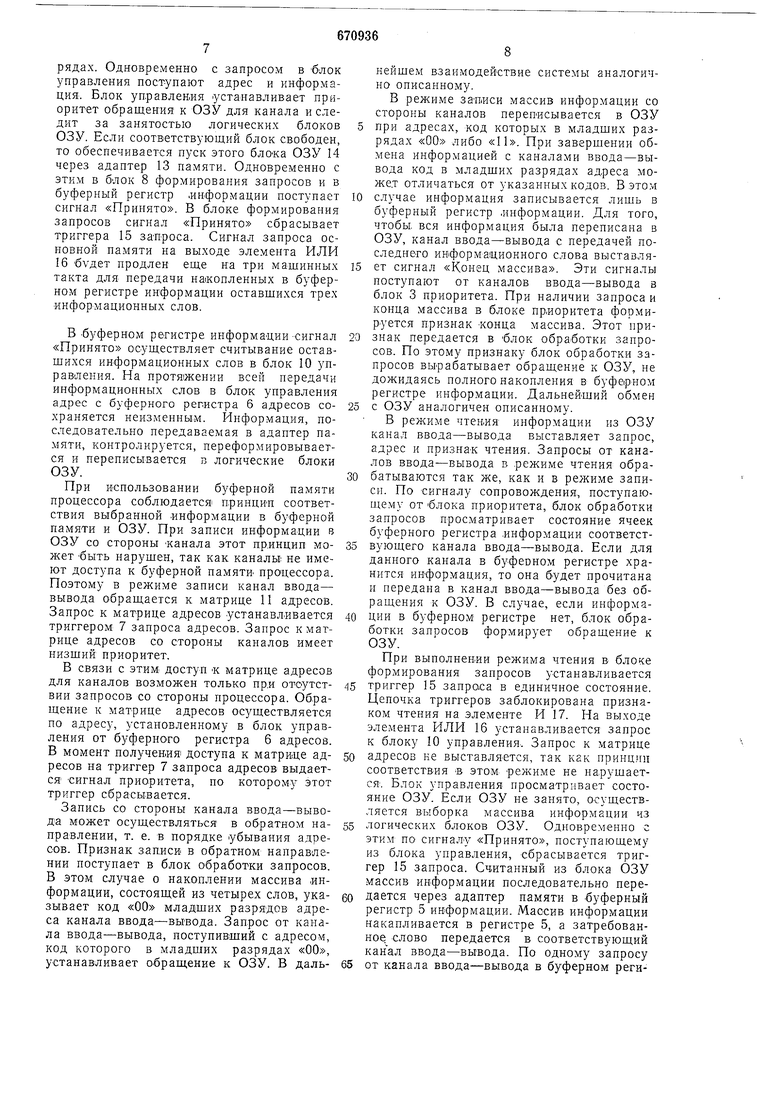

Кроме того, блок формирования запросов в системе содержит элемент ИЛИ, триггер запроса, последовательно соединенные элемент И и триггеры, причем первый вход элемента И соединен с первым выходом триггера запроса, второй вход подключен к вто-рому входу блока, выходы четных триггеров соединены с входа.ми элемента ИЛИ, выходом .подсоединенного к выходу блока, первый и второй входы которого соединены соответственно с первым и вторым входами триггера запроса, второй выход которого соединен с входом элемента ИЛИ.

В описываемой вычислительной системе осуществляется накопление массива информации для каждого канала ввода-вывода в буфере информации. При таком накоплении каждый канал -ввода-вывода, обращаясь к ОЗУ, запускает четыре логических блока по одному адресу. При групповом обращении каналов и процессора уменьшается чи-сло кон-фликтов между ними по обращению к ОЗУ.

Использование общего адреса для пуска четырех логических -блоков ОЗУ со стороны одного канала позволяет ликвйдировать конфликты по обращению к матрице

адресов между каналами и процессором. Все это приводит к повышению быстродействия- вычислительной системы.

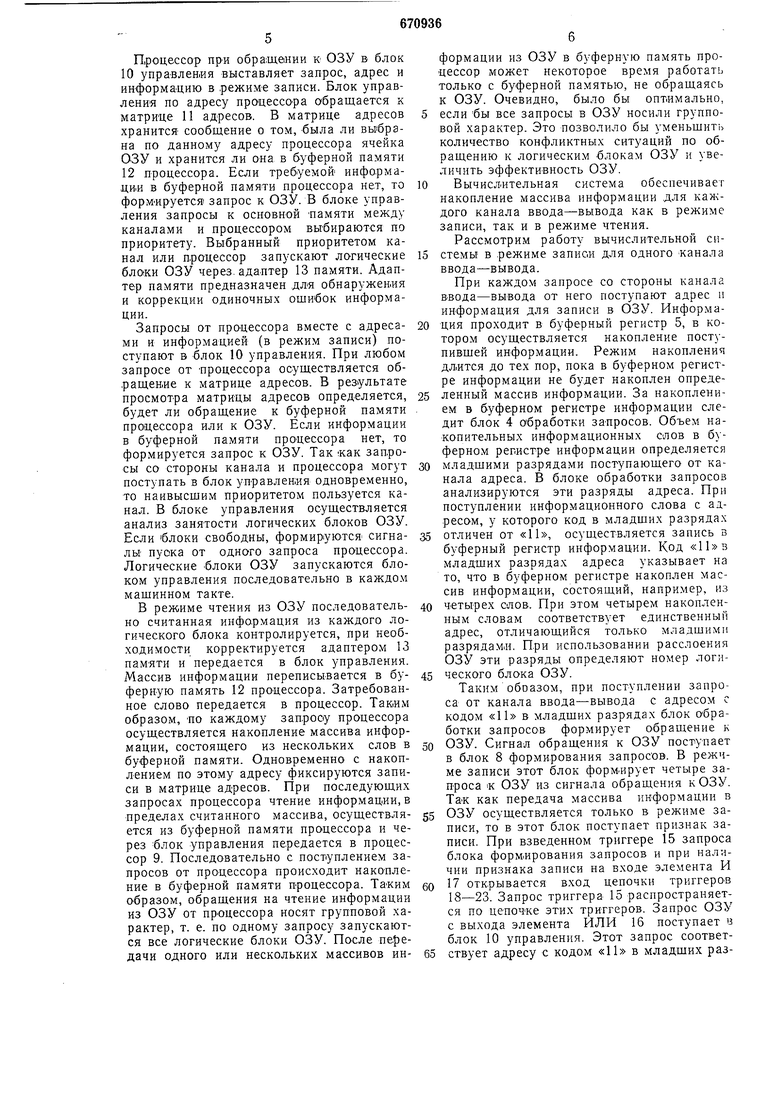

На фиг. 1 -представлена структурная схема цифровой вычислительной системы; на

фиг. 2 - схема блока формирования запросов.

Система содержит каналы 1, 2 вводавывода, блок 3 приоритета, блок 4 обработки запросов, буферны-й регистр 5 информации, буферный регистр 6 адресов, триггер 7 запроса адресо-в, блок 8 формирования запросов, про-цессор 9, -блок 10 управления, матрицу II адресов, буферную память 12, адаптер 13 памяти, основное запоминающзе

устройство 14 (ОЗУ).

Блок формирования запросов (см. фиг. 2) содержит триггер 15 зап-роса, элемент ИЛИ 16, элемент И 17, триггеры 18-23. Каналы ввода-вывода, готовые к обмену информацией с основной -памятью, выставляют запросы. Эти запросы поступают в блок 3 приоритета, в котором одновременно поступившие запросы выбираются по установленному приоритету.

Выбранный запрос устанавливает сигная считывания из соответствующего канала. По сигналу считывания из канала ввода- выв-ода в буферный -регистр адресов подается адрес ячейки ОЗУ (в дальнейшем просто адрес), в блок об-работки запросов-младшие разряды этого адреса, а в буферный регистр информации - информация (только в режиме записи). В блок обработки запросов nocTiynaeT признак записи.

Время считывания- из канала ввода-вывода определяется временем связи с каналом, а момент приема адреса и информации - сигналом сопровождения, поступающим из блока приоритета. В блок

обработки запросов поступает сигнал признака направления записи. Буферный регистр информации для каждого канала ввода-вывода содержит четыре ячейки для накопления ин-форм-аци.и. В режиме записи накапливается информация со стороны канала в-вода-вывода, а в режиме чтения - инфо-рмация со стороны ОЗУ. Буферный регистр адресов предназначен- для хранения адреса. Для каждого канала ввода-вывода он содержит по одной ячейке.

Процессор прИ обращении к ОЗУ в блок 10 управления выставляет запрос, адрес и информацию в .режиме записи. Блок управления по адресу процессора обращается к матрице 11 адресов. В матрице адресов хранится сообщение о том, была ли выбрана по данному адресу процессора ячейка ОЗУ и хранится ли она в буферной памяти 12 процессора. Если требуемой информации в буферной памяти процессора нет, то формируется запрос к ОЗУ. В блоке управления запросы к основной памяти между каналами и процессором внбираются по приоритету. Выбранный приоритетом канал или процессор запускают логические блоки ОЗУ через, адаптер 13 памяти. Адаптер памяти предназначен для обнаружен.ия и коррекции одиночных ошибок информации.

Запросы от процессора вместе с адресами и информацией (в режим записи) поступают в блок 10 управления. При любом запросе от процессора осуществляется обращение к матрице адресов. В результате просмотра матрицы адресов определяется, будет ли обращение к буферной памяти процессора или к ОЗУ. Если информации в буферной памяти прОЦессора нет, то формируется запрос к ОЗУ. Так как запросы со стороны канала и процессора могут поступать в блок управления одновременно, то наивысшим приоритетом пользуется канал. В блоке управления осуществляется анализ занятости логических блоков ОЗУ. Если блоки свободны, формируются сигналы пуока от одного запроса процессора. Логические блоки ОЗУ запускаются блоком управления последовательно в каждом машинном такте.

В режгиме чтения из ОЗУ последовательно считанная информация из каждого логического блока контролируется, при необходимости корректируется адаптером 13 памяти и передается в блок управления. Массив информации переписывается в буферную память 12 процессора. Затребованное слово передается в процессор. Так.им образом, ПО каждому запросу процессора осуществляется накопление массива информации, состоящего из нескольких слов в буферной памяти. Одновременно с накоплением по этому адресу фиксируются записи в матрице адресов. При последующих запросах процессора чтение информации,в пределах считанного массива, осуществляется из буферной памяти процессора и через блок управления передается в процессор 9. Последовательно с поступлением запросов от процессора происходит накопление в буферной памяти процессора. Таким образом, обращения на чтение информации из ОЗУ от процессора носят групповой характер, т. е. по одному запросу запускаются все логические блоки ОЗУ. После передачи одного или нескольких массивов информации из ОЗУ в буферную память процессор может некоторое время работать только с буферной памятью, не обращаясь к ОЗУ. Очевидно, было бы оптимально, если бы все запросы в ОЗУ носили групповой характер. Это позволило бы уменьшить количество конфликтных ситуаций по обращению к логическим -блокам ОЗУ и увеличить эффективность ОЗУ.

Вычислительная система обеспечивает накопление массива информации для каждого канала ввода-вывода как в режиме записи, так и в режиме чтения.

Рассмотрим работу вычислительной системы в режиме записи для одного канала ввода-вывода.

При каждом запросе со стороны канала ввода-вывода от него поступают адрес и информация для записи в ОЗУ. Информация проходит в буферный регистр 5, в котором осуществляется накопление поступившей информации. Режим накопления длится до тех пор, пока в буферном регистре информации не будет накоплен определенный массив информации. За накоплением в буферном регистре информации следит блок 4 обработки за-просов. Объем накопительных информационных слов в буферном регистре информации определяется

младшими разрядами поступаюшего от канала адреса. В блоке обработки запросов анализируются эти разряды адреса. При поступлении информационного слова с адресом, у которого код в младших разрядах

отличен от «11, осуществляется запись в буферный регистр информации. Код «11 в младших разрядах адреса указывает на то, что в буферном регистре накоплен массив информации, состоящий, например, из

четырех слов. При этом четырем накопленным словам соответствует единственный адрес, отличающийся только младшими разрядами. При использовании расслоения ОЗУ эти разряды определяют номер логического блока ОЗУ.

Таким обоазом, при поступлении запроса от канала ввода-вывода с адресом с кодом «11 в младших разрядах блок обработки запросов формирует обращение к

ОЗУ. Сигнал обращения к ОЗУ поступает в блок 8 формирования запросов. В режиме записи этот блок форм.ирует четыре запроса к ОЗУ из сигнала обращения к ОЗУ. Так как передача массива информации в

ОЗУ осуществляется только в режиме записи, то в этот блок поступает признак записи. При взведенном триггере 15 запроса блока форм.ирования запросов и при наличии признака записи на входе элемента И

17 открывается вход цепочки триггеров 18-23. Запрос триггера 15 распространяется по цепочке этих триггеров. Запрос ОЗУ с выхода элемента ИЛИ 16 поступает в блок 10 управления. Этот запрос соответствует адресу с кодом «11 в младших разрядах. Одновременно с запросом в блок управления поступают адрес и информация. Блок уп.равлбЕия устанавливает приоритет обращения к ОЗУ для канала и следит за занятостью логических блоков ОЗУ. Если соответствующий блок свободен, то обеспечивается пуск этого блока ОЗУ 14 через адаптер 13 памяти. Одновременно с этим в блок 8 формирования запросов и в буферный регистр .информации поступает сигнал «Принято. В блоке формирования запросов сигнал «Принято сбрасывает триггера 15 запроса. Сигнал запроса основной памяти на выходе элемента ИЛИ 16 будет продлен еще на три машинных такта для передачи накопленных в буферном регистре информации оставшихся трех информационных слов.

В буферном регистре информации сигнал «Принято осуществляет считывание оставщихся информационных слов в блок 10 управления. На протяжении всей передачи информационных слов в блок управления адрес с буферного регистра 6 адресов сохраняется неизменным. Информация, последовательно передаваемая в адаптер памяти, контролируется, переформировывается и переписывается в логические блоки ОЗУ.

При использовании буферной памяти процессора соблюдается принцип соответствия выбранной информации в буферной памяти и ОЗУ. При записи информации в ОЗУ со стороны Канала этот пр.инцип может быть нарущен, так как каналы не имеют доступа к буферной памяти процессора. Поэтому в режиме записи канал ввода- вывода обращается к матрице И адресов. Запрос к матрице адресов устанавливается триггером 7 запроса адресов. Запрос к матрице адресов со стороны каналов имеет низший приоритет.

В связи с ЭТИМ доступ К матрице адресов для каналов возможен только пр,и отсутствии запросов со стороны процессора. Обращение к матрице адресов осЗществляется по адресу, установленному в блок управления от буферного регистра 6 адресов. В момент получения доступа к матрице адресов на триггер 7 запроса адресов выдается Сигнал приоритета, по которому этот триггер сбрасывается.

Запись со стороны канала ввода-вывода может осуществляться в обратном направлении, т. е. в порядке убывания адресов. Признак задней в обратном направлении поступает в блок Обработки запросов. В этом случае о накоплении массива информации, состоящей из четырех слов, указывает код «00 младщих разрядов адреса канала ввода-вывода. Запрос от канала ввода-вывода, поступивщий с адресом, код которого в младших разрядах «00, устанавливает обращение к ОЗУ. В дальнейшем взаимодействие системы аналогично описанному.

В режиме заП.иси массив информации со стороны каналов переписывается в ОЗУ при адресах, код которых в младших разрядах «00 либо «11. При завершении обмена информацией с каналами ввода-вывода код в младших разрядах адреса может отличаться от указанных кодов. В этом

случае информация записывается лишь в буферный регистр .информации. Для того, чтобы, вся информация была переписана в ОЗУ, канал ввода-вывода с передачей последнего информационного слова выставляет сигнал «Конец массива. Эти сигналы поступают от каналов ввода-вывода в блок 3 приоритета. При наличии запроса и конца массива в блоке пр.иоритета формируется признак Конца массива. Этот признак передается в блок обработки запросов. По этому признаку блок обработки запросов вырабатывает обращение к ОЗУ, не дожидаясь полного накопления в буферном регистре информации. Дальнейший обмен

с ОЗУ аналогичен описанному.

В режиме чтения информации из ОЗУ канал ввода-вывода выставляет запрос, адрес и признаК чтения. Запросы от каналов ввода-вывода в режиме чтения обрабатываются так же, как и в режиме записи. По сигналу сопровождения,, поступающему от блока приоритета, блок обработки запросов просматривает состояние ячеек буферного регистра .информации соответствующего канала ввода-вывода. Если для данного канала в буферном регистре хранится информация, то она будет прочитана и передана в канал ввода-вывода без обращения к ОЗУ. В случае, если информаЦии в буферном регистре нет, блок обработки запросов формирует обращение к ОЗУ.

При выполнении режима чтения в блоке формирования запросов устанавливается

триггер 15 запроса в единичное состояние. Цепочка триггеров заблокирована признаком чтения на элементе И 17. Па выходе эле1мента ИЛИ 16 устанавливается запрос к блоку 10 управления. Запрос к матрице

адресов ке выставляется, так как принцип соответствия В этом режиме не нарущается. Блок управления просматривает состояние ОЗУ. Если ОЗУ не занято, осуществляется выборка массива информации чз

логических блоков ОЗУ. Одновременно с этим по сигналу «Принято, поступающему из блока управления, сбрасывается триггер 15 запроса. Считанный из блока ОЗУ массив информации последовательно передается через адаптер памяти в буферный регистр 5 информации. Массив информации накапливается в регистре 5, а затребованное, слово передается в соответствующий канал ввода-вывода. По одному запросу

от канала ввода-вывода в буферном регистре информации накапливается массив информации. По последующим запросам от этого канала ввода-вывода считывание в пределах накопленного массива осуществляется из буферного регистра информации, что приводит к уменьщению числа одиночных обращений к ОЗУ.

Таким образом, в рассмотренной вычислительной системе обмен с ОЗУ для каналов ввода-БЫВОда и- процессора осуществляется массивом информации, это приводит к лучшему сопряжению обращений с ОЗУ.

В режиме чтения из ОЗУ в буферном регистре информации происходит накопление массива информации. Поэтому дальнейщее чтение осуществляется не из ОЗУ, я из буферного регистра информации. При этом уменьщается число конфликтов по обращению к ОЗУ, что пр,иводит к повыщеник быстродействия вычислительной системы. При этом значительно увеличивается пиковая пропускная способность каналов ввода-вывода для системы канал ввода- вывода - буферный регистр информации.

Использование общего адреса для массива .информации в режиме записи в ОЗУ со стороны каналов ввода-вывода позволяет убрать конфликты между каналами и процессором по обращению к матрице адресов. Это приводит к увеличению скорости обмена процессора с буферной памятью.

Формула изобретения

1. Вычислительная система, содержащая каналы ввода-вывода, блок приоритета, блок обработки- запросов, буферный регистр .информации, буферный регистр адресов, процессор, блок управления, матрицу адресов, буферную память, адаптер памяти и основное запоминающее устройство, причем первые выходы каналов ввода-вывода соединены с первым и вторым входами блока приоритета, выходы которого соединены с первыми входами каналов въода-вывода, третий выход соединен с первым входом блока обработки запросов, первый выход которого соединен с первым входом буферного регистра информации, второй выход соединен с первым входом буферного регистра адресов, вторые выходы каналов ввода-вывода соединены с вторыми входами блока обработки запросов, буферного регистра .информации и буферного регистра адресов, выходы буферного регистра информации и буферного регистра адресов

соединены с первым и вторым входами блока управления, выход процессора соединен с третьим входом блока управления, первый выход которого соединен с первым входом матрицы адресов, второй выход соединен с входом буферной памяти, третий выход соединен с входом адаптера памяти, выход адаптера памяти соединен с четвертым входом блока управления и с третьим

входом буферного регистра информации, второй выход буферного регистра информации соединен с вторыми входам.и каналов ввода-вывода, адалтер памяти соединен двусторонними связями с основным

запоминающим устройством, отличающаяся тем. что, с целью повыщения быстродействия, в нее введены триггер запроса адресов и блок формирования запросов, пр.ичем выход триггера запроса адресов соединен с вторым входом матрицы адресов, выход которой соединен с первым входом триггера запроса адресов, второй вход которого соединен с третьим выходом блока обработки запросов, четвертый выход которого соединен с первым входом блока формирования запросов, второй вход которого соединен с четвертым выходом блока управления и четвертым входом буферного регистр - информации, выход блока формирован.ия за.просов соединен с пятым входом блока управления, третьи выходы каналов ввода-вывода соединены с третьим и четвертым входами блока приоритета, четвертые выходы каналов ввода-вывода соединены с третьим входом блока обработки запросов.

2. Система по п. 1, отличающаяся тем, что блок формирования запросов содержит элемент ИЛИ, триггер запроса, последовательно соединенные элемент И и триггеры, причем первый вход элемента И соединен с первым выходом триггера запроса, второй вход подключен к второму входу блока, выходы четных триггеров соедкнены с входами элемента ИЛИ, выход которого подсоединен к выходу блока, первый и второй входы которого соединены соответственно с первым и вторым входами триггера запроса, второй выход которого

соединен с входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе 1. Катцан Г. Вычислигельные мащины системы 370. М., «Мир, 1974, с. 246-273.

2. Патент США № 3699530, кл. G 06F 9.18, опублик. 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1977 |

|

SU682900A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство для сопряжения основной памяти цифровой вычислительной машины с каналами ввода-вывода | 1977 |

|

SU689438A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Устройство управления памятью | 1987 |

|

SU1411761A1 |

| Устройство для сопряжения оперативной памяти с процессором и каналами ввода-вывода | 1977 |

|

SU689439A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

15

IB

Авторы

Даты

1979-06-30—Публикация

1977-04-12—Подача