1

Предложенное устройство относится к области автоматики и вычислительной техники и может быть иапользовано при реализации технических средств дискретной автоматики и вычислительной техяики.

Известны устройства для умножения чисел, содержащие два дешифратора чисел, входы которых связаны с входными шинами, а выходы - со входами матричного дешифратора, выполненного на схемах «И, выходы которого подключены ко входам схем «ИЛИ для отрицательных и положительных чисел, и формирователь знака, связанный с шинами знаковых разрядов сомножителей.

Недостатком известных устройств является большое количество элементов «И м атричного дешифратора и, как следствие этого, сложные схемы разрядных сборок, формирующие окончательный результат, так как один элемент матричного дешифратора, являющийся схемой совпадения, реализует только одну комбинацию результата с округлением для трех разрядов перемножаемых сомножителей.

Предложенное устройство отличается тем, что в него введены коммутатор кодов и два дешифратора rpyimi чисел, входы которых связаны с выходами дешифраторов чисел, а выходы - со входами матричного дешифратора. Матричный дешифратор содерл ит дополнителыные схемы «И, связанные входами с выходами дешифраторов чисел и дешифраторов груип чисел, а их выходы соединены со входами схем «ИЛИ для отрицательных чисел. Выходы схем «ИЛИ для положительных и отрицательных чисел связаны с соответствующими входами формирователя знака и через коммутатор кодов, другими входами связанный с выходами формирователя знака, - с выходными шинами устройства.

Это позволяет упростить устройство за счет уменьшения количества схем «И в матричном дешифраторе и упрощения схем «ИЛИ для разрядов чисел.

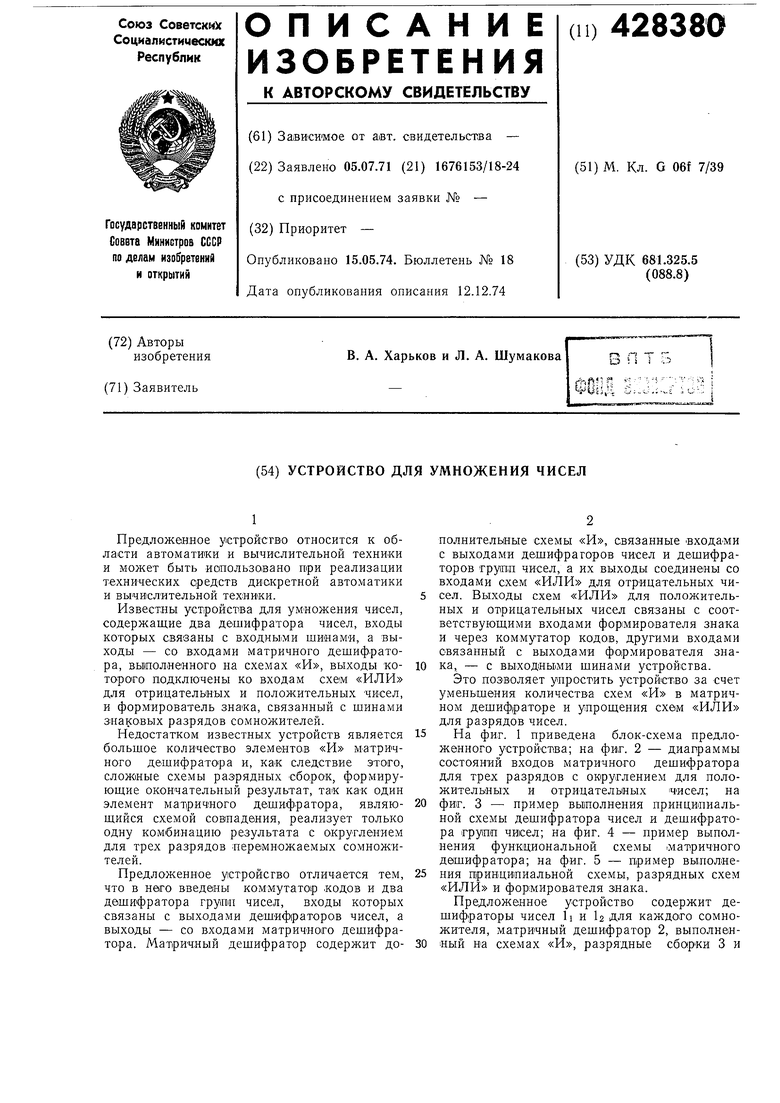

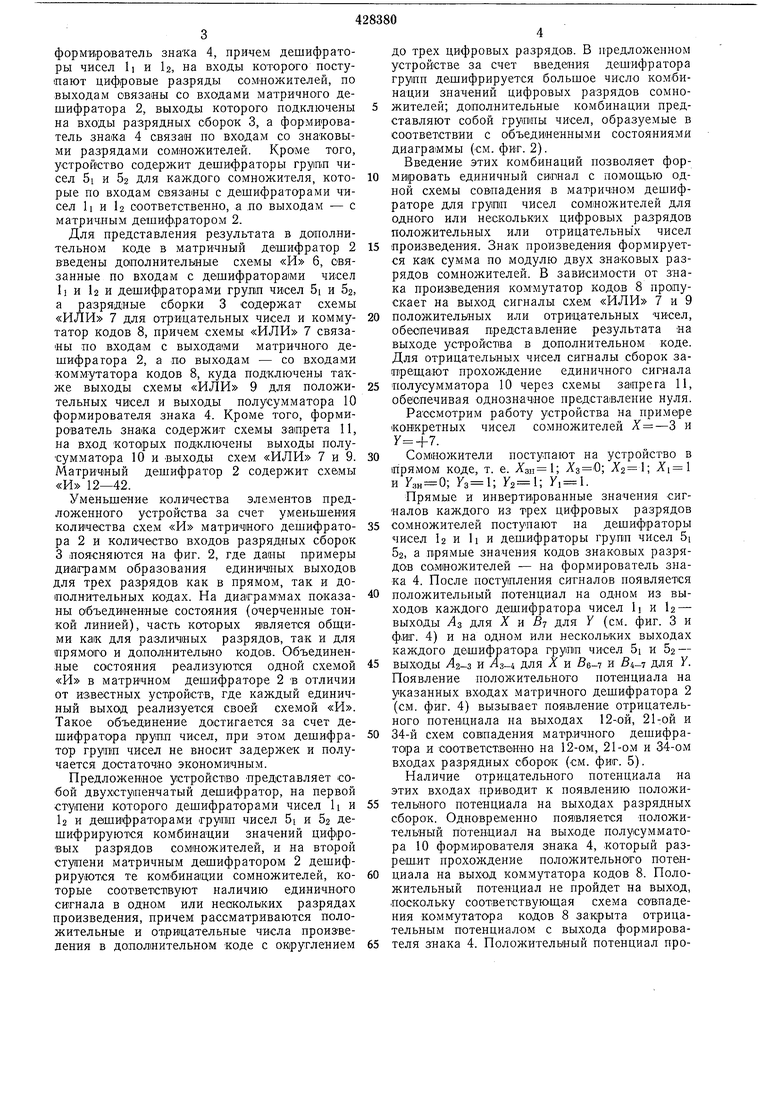

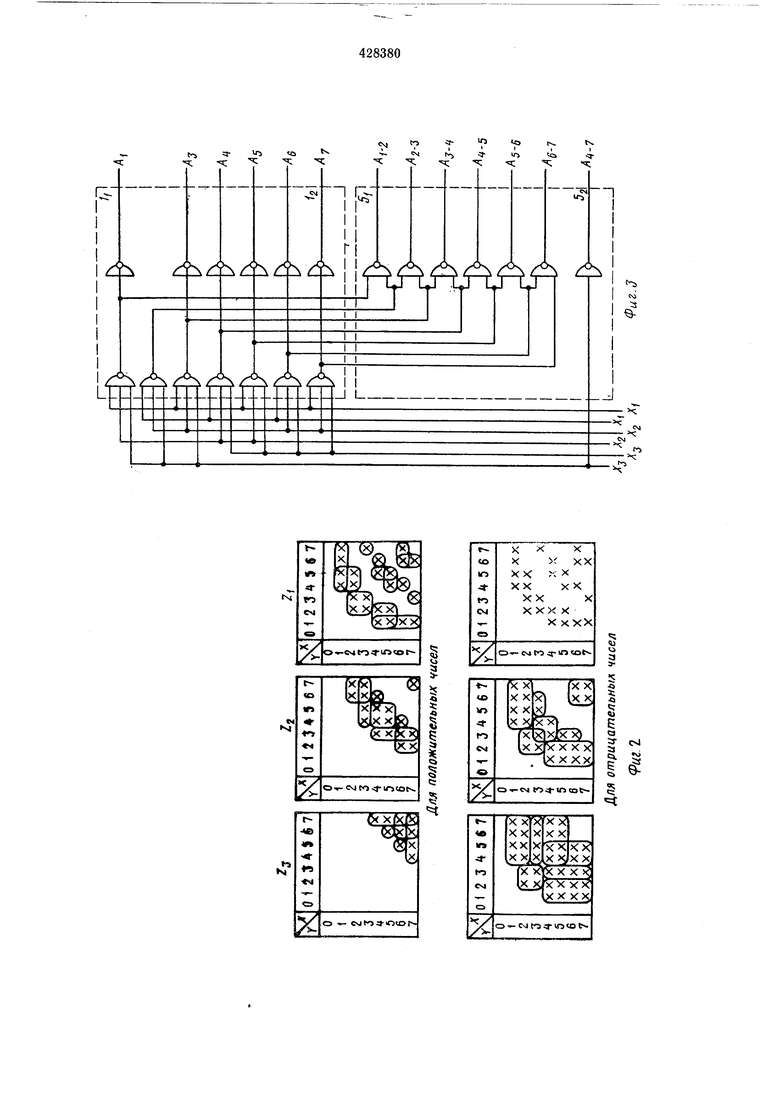

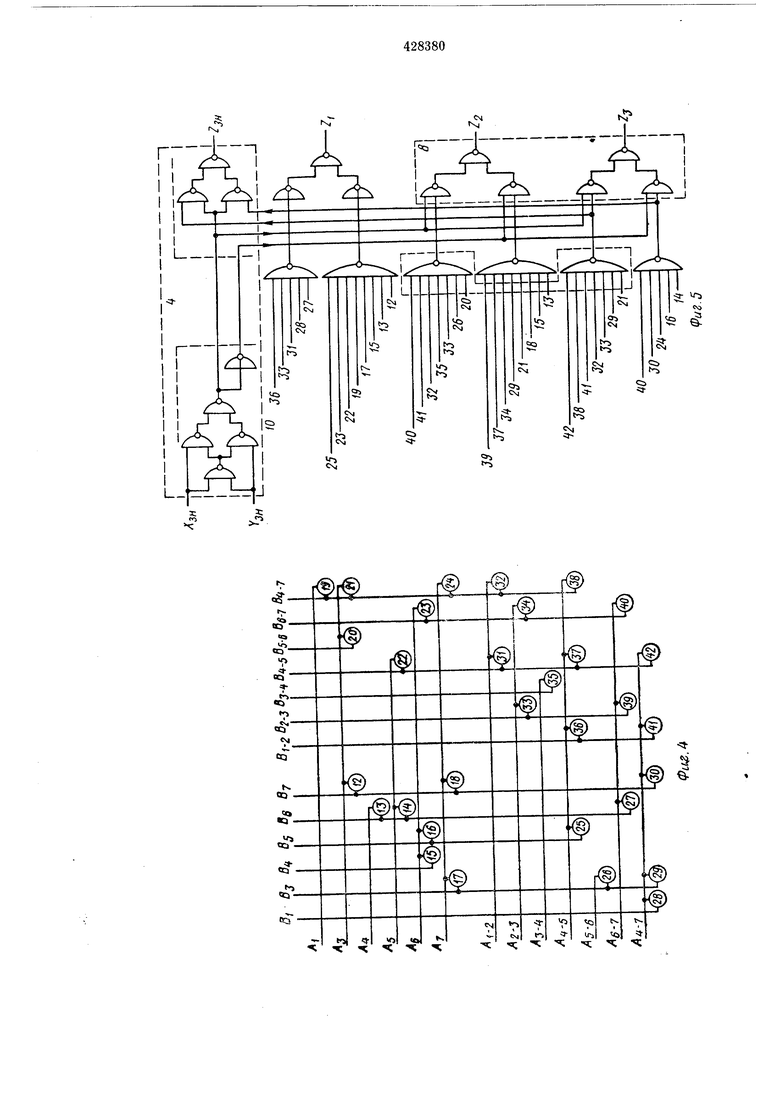

На фиг. 1 приведена блок-схема предложенного устройства; на фиг. 2 - диаграммы состояний входов матричного дешифратора для трех разрядов с округлением для положительных и отрицательных чисел; на

фиг. 3 - пример выполнения принципиальной схемы дешифратора чисел и дешифратора групп чисел; на фиг. 4 - пример выполнения функциональной схемы .матричного дешифратора; на фиг. 5 - пример вылолнения аринципиальной схемы, разрядных схем «ИЛИ и формирователя знака.

Предложенное устройство содержит дешифраторы чисел li и Ь для каждого сомножителя, матричный дешифратор 2, выполненный на схемах «И, разрядные сборки 3 и

формирователь знака 4, причем дешифраторы чисел Ii и 2, на входы которого поступают цифровые разряды сомяожителей, по выходам связаны со входами матричного дешифратора 2, выходы которого подключены на входы разрядных сборок 3, а формирователь знака 4 связан по входам со знаковыми разрядами сомножителей. Кроме того, устройство содержит дешифраторы груюл чисел 5i и 52 для каждого сомножителя, которые по входам связаны с дешифраторами чисел h и Ь соответственно, а ло выходам - с матричным дешифратором 2.

Для представления результата в даполнительном коде в матричный дешифратор 2 введены дополнительные схемы «И 6, связанные по входам с дешифраторами чисел li и Ь и дешифраторами групп чисел 5i и 62, а разрядные сборки 3 содержат схемы «ИЛИ 7 для отрицательных чисел и коммутатор кодов 8, причем схемы «ИЛИ 7 связаны по входам с выходами матричного дешифратора 2, а по выходам - со входами коммутатора кодов 8, куда подключены также выходы схемы «ИЛИ 9 для положительных чисел и выходы полусумматора 10 формирователя знака 4. Кроме того, формирователь знака содержит схемы запрета 11, на вход которых подключены выходы полусумматора 10 и выходы схем «ИЛИ 7 и 9. Матричный дешифратор 2 содержит cxeiMbi «И 12-42.

Уменьшение количества элементов предложенного устройства за счет уменьшения количества схем «И матричного дешифратора 2 и количество входов разрядных сборок 3 поясняются на фиг. 2, где даны примеры диаграмм образования единичных выходов для трех разрядов как в прямом, так и дополнительных кодах. На диаграммах показаны объединенные состояния (очерченные тонкой линией), часть которых является обшими как для различных разрядов, так и для прямого и дополнительно кодов. Объединенные состояния реализуют1ся одной схемой «И в матричном дешифраторе 2 в отличии от известных устройств, где каждый единичный выход реализуется своей схемой «И. Такое объединение достигается за счет дешифратора лрупл чисел, при этом дешифратор груип чисел не вносит задержек и получается достаточно экономичным.

Предложенное устройство представляет собой двухступенчатый дешифратор, на первой ступени которого дешифраторами чисел h и Ь и дешифраторами групп чисел 5i и бг дешифрируются комбинации значений цифровых разрядов сомножителей, и на второй ступени матричным дешифратором 2 дешифрируются те комбинации сомножителей, которые соответствуют наличию единичного сигнала в одном или нескольких разрядах произведения, причем рассматриваются положительные и отрицательные числа произведения в дополнительном коде с округлением

до трех цифровых разрядов. В предложенном устройстве за счет введения дешифратора групп дешифрируется большое число ком|бинации значений цифровых разрядов сомножителей; дополнительные комбинации представляют собой группы чисел, образуемые в соответствии с объединенными состояниями диаграммы (см. фиг. 2).

Введение этих комбинаций позволяет формировать единичный си1пнал с помошью одной схемы совпадения в матричном дешифраторе для групп чисел сомножителей для одного или нескольких цифровых разрядов положительных или отрицательных чисел произведения. Знак произведения формируется как сумма по модулю двух знаковых разрядов сомножителей. В зависимости от знака произведения коммутатор кодов 8 пропускает на выход сигналы схем «ИЛИ 7 и 9 положительных или отрицательных чисел, обеспечивая представление результата на выходе устройст1ва в дополнительном коде. Для отрицательных чисел сигналы сборок заррешают прохождение единичного сигнала полусумматора 10 через схемы запрега 11, обеспечивая однозначное представление нуля.

Рассмотрим работу устройства на примере конкретных чисел сомножителей Х -3 и .

Сомножители поступают на устройство в прямом коде, т. е. и Кзн--0; 1 1.

Прямые и инвертированные значения сигналов каждого из трех цифровых разрядов сомножителей поступают на дешифраторы чисел Ь и li и дешифраторы групп чисел 5i 62, а прямые значения кодов знаковых разрядов сомножителей - на формирователь знака 4. После поступления сигналов появляется положительный потенциал на одном из выходов каждого дешифратора чисел li и Ь - выходы АЗ для X -я B для У (см. фиг. 3 и фнаг. 4) и на одном или нескольких выходах каждого дешифратора групп чисел 5i и 52 -

выходы Лз-з и Лз-4 для X и Вб-7 и 4-7 ДЛЯ У.

Появление положительного потенциала на указанных входах матричного дешифратора 2 (см. фиг. 4) вызывает появление отрицательного потенциала на выходах 12-ой, 21-ой и 34-й схем совпадения матричного дешифратора и соответственно на 12-ом, 21-ом и 34-ом входах разрядных сборок (см. фиг. 5).

Наличие отрицательного потенциала на этих входах приводит к появлению положительного потенциала на выходах разрядных сборок. Одновременно появляется положительный потенциал на выходе полусумматора 10 формирователя знака 4, который разрешит прохождение положительного потенциала на выход коммутатора кодов 8. Положительный потенциал не пройдет на выход, поскольку соответствуюшая схема совпадения коммутатора кодов 8 закрыта отрицательным потенциалом с выхода формирователя знака 4. Положителыный потенциал проходит на выход устройства. Наличие положительного потенциала на .выходе разрядных сборок 3 разрешает прохождение положительного гютен1циала на выход формирователя анака 4. Таким образом, на выходе устройст1ва , 2 0; Zi, что соответствует числу произведения в дополнительном коде, являющемуся результатом округления до трех разрядов числа -21.

Предмет изобретения

Устройство для умножения чисел, содержащее два дешифратора чисел, входы которых связаны с входными шинами, а выходы- со входами матричнО(ГО дешифратора, выходы которого подключены ко входам схем «ИЛИ для отрицательных и положительных чисел, и формирователь знака, связанный с шинами з:на;ковых разрядов сомножителей, отличающее с Я тем, что, с целью улрощеиия устройства, в него В1ведены коммутатор и кодов и два дешифратора групп чисел, входы которых связаны с выходами дешифраторов чисел, а выходы - со входами матричного дешифратора, причем матричный дешифратор содержит дополнительные схемы «И, связанные входами с выходами дешифраторов чисел и дешифраторов групп чисел, а их выходы соединены со входами схем «ИЛИ для отрицательных чисел, выходы схем «ИЛИ для положительных и отрицательных чисел связаны с соответствующими входами фо|рмирователя знака и через коммутатор кодов, другими входами связанный с выходами формирователя знака, - с выходными шинами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ | 2006 |

|

RU2306595C1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Последовательное множительное устройство | 1984 |

|

SU1233138A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

fY23 «

гт

I

1

I 10 I

I I 71 .I I,I

1I

3H

«;

«} u ;

5 «

Даты

1974-05-15—Публикация

1971-07-05—Подача