1

Изобретение относится к области вычислительной техники, а именно к сумматорам накапливаюш,его типа.

Известны накапливаюЩ|Ие сумматоры со сквозным переносом.

Недостатком известных параллельных сумматоров на.капливающего типа со сквозным переносом является сложность выполнения цепей формирования сигнала сквозного переноса. В известном параллельном сумматоре накапливающего типа со сквозным переносом цепь формирования сигнала сквозного переноса содержит вентиль переноса В, вентиль прямого циклического переноса В-1, линию задержки либо триггер, фиксирующий сигнал переноса.

С целью упрощения схемы цепей формирования сигнала сквозного переноса в каждом разряде единичный и нулевой выходы суммирующего триггера соединены соответственно с «счетным входом и входом «установка 1 триггера памяти сигнала переноса, нулевой и единичный выходы которого подключены соответственно в следующем старщем разряде ко входам «управление 1 триггера памяти сигнала переноса и клапана (вентиля) ввода сигнала переноса, выход последнего подключен через клапан ввода числа к счетному входу суммирующего триггера.

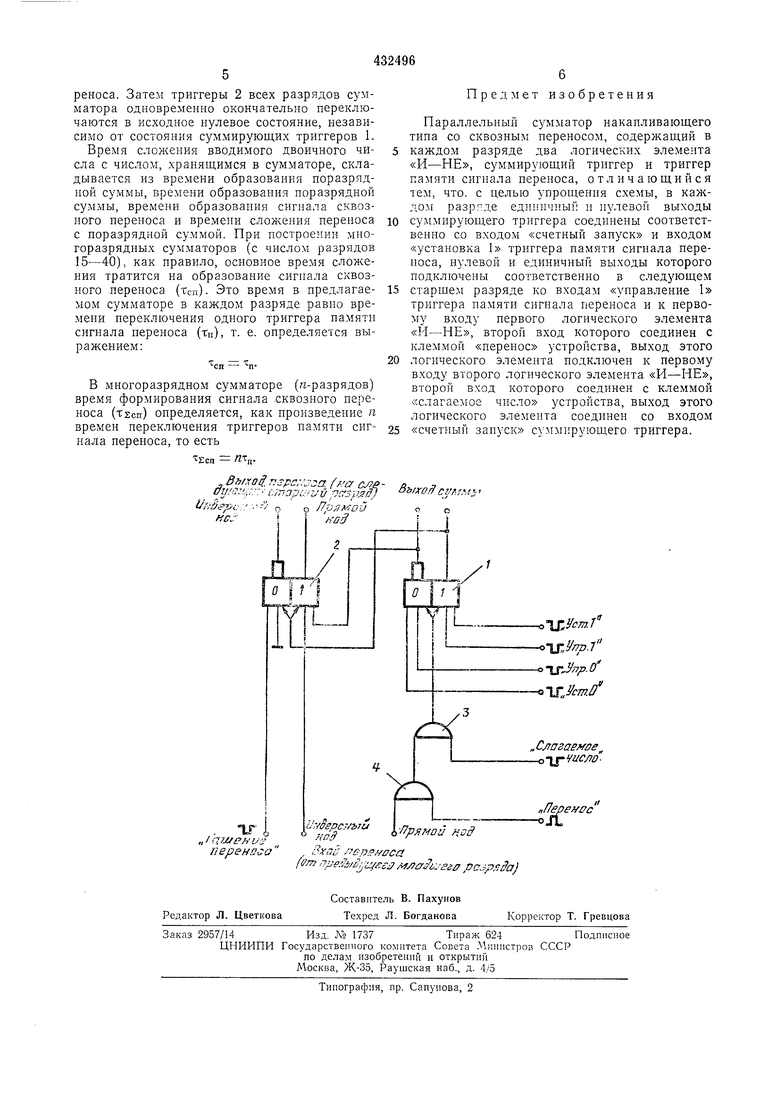

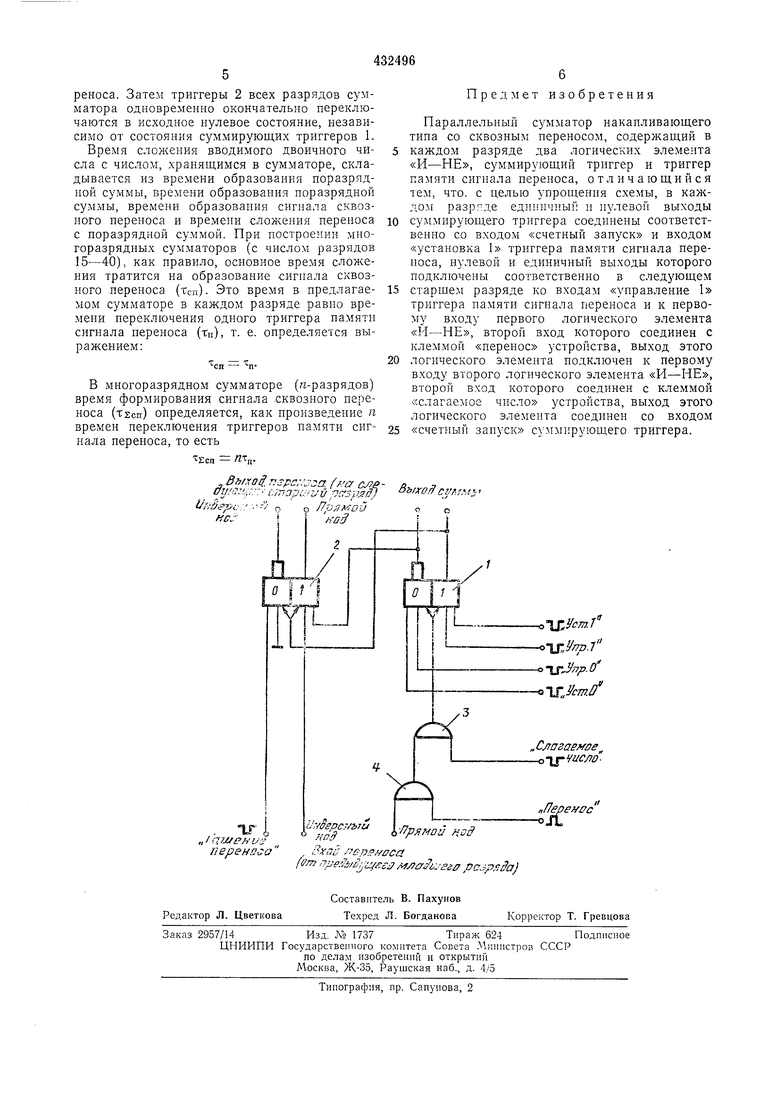

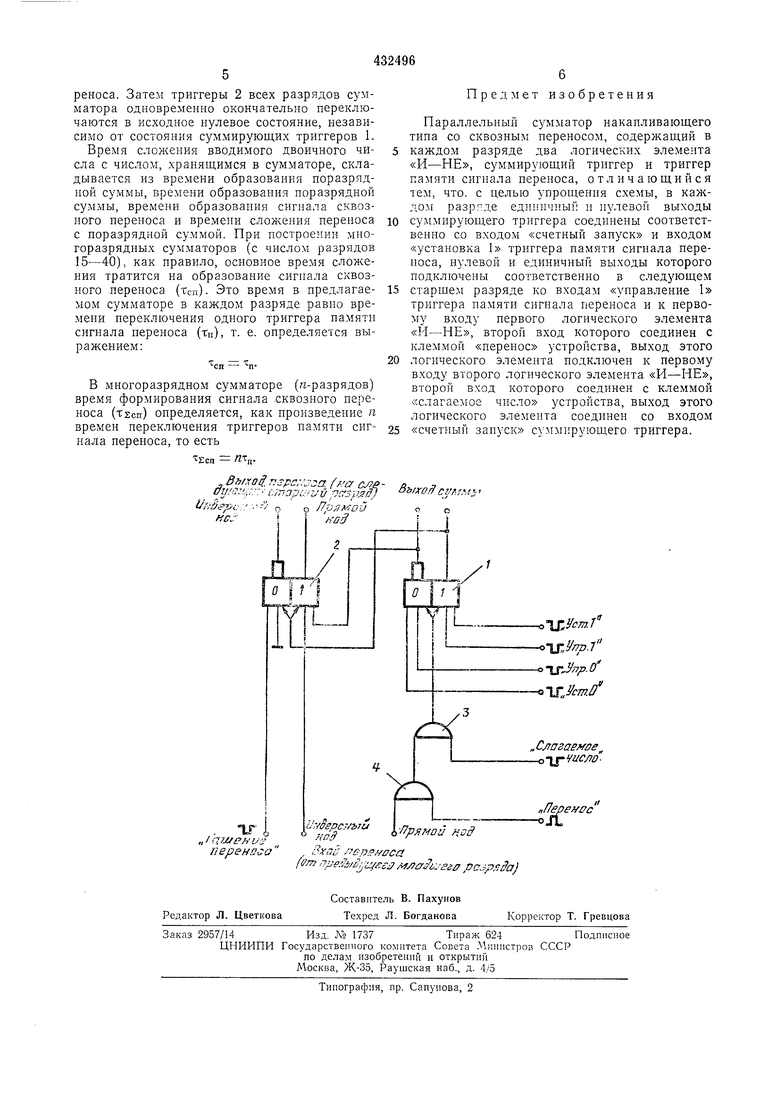

Функциональная схема одного из разрядов

двоичного параллельного сумматора со сквозным переносом изображена на чертеже.

Каждый разряд сумматора содержит суммирующий триггер 1, триггер памяти сигнала переноса 2, клапан ввода слагаемых чисел 3 и клапан ввода переноса 4, реализующих логическую операцию логических элементов «И-НЕ для высоких потенциалов. Единичный и нулевой выходы суммирующего триггера 1 соединены соответственно с входом «счетный запуск и входом «установка 1 триггера памяти сигнала .переноса 2 этого же разряда. Нулевой и единичный выходы триггера памяти переноса 2 подключены соответственно в

следующе.м старщем разряде к входу «управление 1 триггера памяти сигнала переноса 2 и клапану ввода сигнала переноса 4. Выход клапана переноса 4 через клапан ввода чисел 3 подключен к «счетному входу суммирующего триггера 1. Суммирующий триггер 1 может быть выполнен по любой схеме со счетным запуском, триггер памяти сигнала переноса 2 должен иметь входы: «счетный запуск, «управление 1, «установка 1, «управление О, «установка О. Счетный запуск осуществляется в момент отрицательного фронта изменения потенциала на «счетном входе при высоких потенциалах на всех остальных входах. Установка триггера в единичное (нулевое) состояние осуществляется либо низким

потенциалом на входе «установка I («установка О) нри ннзком потенциале на «счетном входе и высоких потенциалах на остальных входах, либо низкими потенциалами на входах «установка 1 и «управление 1 («установка О и «управление О) при высоких потенциалах на остальных входах. При применении такого же триггера в качестве суммирующего все перечисленные возможности управления («установка 1, «установка О) могут быть использованы с целью управления сумматором.

В предлагаемом сумматоре сложение двоичных чисел осуществляется в два этапа.

1.Вначале в суммирующих триггерах 1 производится поразрядное сложение числа, хранящегося в них, и числа, вводимого через клапан ввода чисел 3. Результат поразрядного сложения (поразрядная сумма) запоминается на суммирующих триггерах 1, а в это же время триггерами памяти сигнала переноса 2 формируются сигналы переноса, в том числе и сигнал сквозного переноса, если это диктуется условиями сложения.

2.Затем по команде «перенос, подаваемой после сформирования сигнала сквозного переноса на клапан ввода сигнала переноса 4, в соответствии с сигналами переноса из предыдущих младших разрядов осуществляется во всех разрядах одновременное сложение на суммирующих триггерах 1 переносов с поразрядной суммой. На выходах триггеров 1 формируются сигналы, отображающие конечный результат сложения двух чисел (окончательную сумму), который может храниться в сумматоре до следующего сложения.

Если требуется к хранимой сумме прибавить еще число, то после команды «перенос необходимо установить триггеры памяти сигнала переноса 2 в нулевое состояние (гашение Переноса), подав на входы «гашение переноса низкий потенциал. Для уменьшения времени цикла сложения чисел гашение переноса в данном сумматоре можно производить одновременно со вводом слагаемого числа. Если требуется погасить число в сумматоре, то для этого достаточно подать одновременно на входы «установка О суммирующих триггеров 1 всех разрядов низкий потенциал. Одновременно с этим на триггеры памяти сигнала переноса 2 следует подать также сигнал установки в нулевое состояние.

При поступлении на входы сумматора «слагаемое число импульсов низкого потенциала, отображающих слагаемые числа, в тех разрядах, где цифра равна единице, на выходах клапанов ввода чисел 3 формируются импульсы высокого потенциала. Эти импульсы поступают на «счетный вход суммирующих триггеров 1 и подготавливают их к счетному запуску. Счетный запуск осуществляется во время формирования заднего фронта импульсов, отображающих слагаемые числа, когда на счетных входах триггеров I формируется отрицательный фронт. Триггеры 1 нереключаются в -Противоположное исходночму состояние, осуществляя тем самым поразрядное сложение чисел. В зависимости от поразрядной суммы данного разряда и предыдущих младших разрядов сигнал переноса в следующий старший разряд формируется двумя способами.

а) Если в данном разряде хранится единица, то на единичном выходе триггера 1 нри

сутствует высокий нотенциал, который подготавливает триггер 2 к счетному запуску, и если в этом разряде во время ввода слагаемого числа вводится еще единица, то сигнал переноса формируется в мо.мент переключения

суммирующего триггера 1 из единичного состояния в нулевое, когда на его единичном выходе образуется отрицательный перепад потенциала, переключающий триггер 2 в единичное состояние. На выходах триггера 2 возникают сигналы, отображающие перенос в следующий старший разряд.

б) Если в данном разряде хранится единица (ноль) и во время ввода чнсла в этот разряд вводится ноль (единица), а из предыдущего младшего разряда поступает сигнал переноса в инверсном коде па вход «управление Ь триггера 2, то триггер 2 также переключается в единичное состояние, вырабатывая сигнал сквозного переноса в следующий

старший разряд.

Причиной срабатывания триггера 2 в этом случае является подача низкого потенциала одновременно па входы «управление Ь и «установка 1.

После сформирования сигнала сквозного переноса на клапапах ввода переноса 4 устанавливаются высокие потенциалы, отображающие перенос в прямом коде. При поступлении после этого сигнала «перенос те клапапы 4, на вторые входы которых в это время из предыдущих младших разрядов поступает сигнал переноса, пропускают импульсы низкого потенциала. В результате их воздействия на клапаны ввода чисел 3 на выходах

этих клапанов возникают импульсы высокого потенциала, подготавливающие триггеры 1 к счетному запуску. Счетный запуск происходит во время формирования отрицательного фронта импульса команды «перепое, когда на

счетных входах триггеров 1 образуется также отрицательный фронт. Триггеры 1 переключаются в состояния, соответствующие окончательной сумме и запоминают ее. После сформирования окончательной суммы триггеры памяти сигнала переноса 2 возвращаются в исходное нулевое состояние импульсом низкого потенциала («гашение переноса), поступающим на вход «установка О этих триггеров. При поступлении импульса

«гашение переноса независимо от величины потенциала на остальных входах, на нулевом выходе триггера 2 возникает высокий потенциал, который поступает па вход «управление 1 триггера 2 следующего старшего разряда и нарушает цепь сигнала сквозного пе

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

Даты

1974-06-15—Публикация

1972-05-25—Подача