Изобретение относится к области вычислительной техники и может быть использовано для обеспечения входного и выходного контроля логических микросхем, используемых, на1пример, в цифровых вычислительных машинах.

Известны устройства для контроля логических микросхем, с помощью которых производится полная и раздельная во времени проверка микросхем по статическим и динамическим параметрам. Это приводит к усложнению программы проверки и снижению производительности при частой смене видов проверки.

Целью настоящего изобретения является повышение производительности контроля микросхем путем совмещения во времени проверки на функционирование с проверкой по динамическим параметрам.

Сущность изобретения заключается в том, что в устройство введен кольцевой регистр сдвига, выход которого соединен с первым входом блока формирования сигналов, второй вход которого подключен к выходу.кольцевого регистра сдвига через группу вентилей, и дешифратор, управляющий вход группы вентилей соединен с первым входом устройства, второй вход которого подключен к первому входу кольцевого регистра сдвига, второй вход которого соединен с выходом задающего генератора.

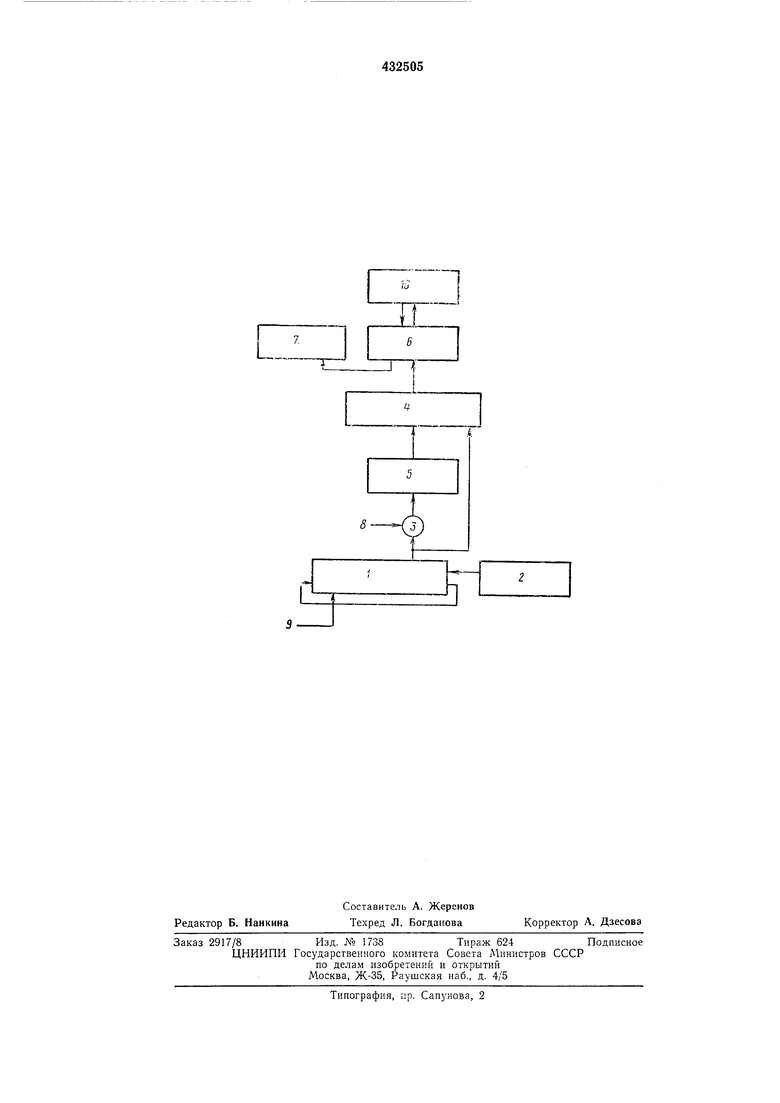

На чертеже представлена блок-схема устройства, в состав которой входят: кольцевой регистр 1 сдвига, задающий генератор 2, группа вентилей 3, блок 4 формироваппя сигналов, дешифратор 5, блок коммутаций 6, блок измерений 7; 8, 9-входы устройства; 10--контролируемая микросхема.

При работе устройства на проверяемую логическую микросхему подаются сигналы, соответствующие минимальным функциональным тестам каждого типа логических микросхем, формируемые по двухступенчатой закоммутированной программе.

Предварительно в кольцевом регистре 1 сдвига устанавливается необходимый для проверки логической микросхемы 10 код. После этого подаются импульсы сдвига от задающего генератора 2, что обеспечивает сдвиг кода, записанного в кольцевом регистре сдвига. Формируемые после каждого импульса сдвига кодовые комбинации с выходов регистра 1 поступают на вход вентилей 3 и на блок 4 формирования сигналов.

Для проверки большинства типов логических микросхем набор кодовых комбинаций, подаваемых непосредственно с регистра 1, достаточен для получения минимальных функциональных тестов.

В том случае, если кодовые комбинации с регистра 1 не дают возможности получить минимального теста проверяемой микросхемы, открываются вентили 3 и кодовые комбинации с выходов кольцевого регистра сдвига поступают на входы дешифратора 5. Дешифратор образует донолнительиые кодовые комбинации, необходимые для получения мипимального функционального теста. Эти дополнительные кодовые комбинации выходов дешифратора 5 поступают на входы блока 4, обеснечиваюш,его создание необходимых электрических режимов проверки микросхемы.

Дешифратор 5 и кольцевой регистр 1 сдвига образуют первую ступень коммутаций программы проверки. Повторяемость программы проверки во Бремени обеспечивают тем, что разряды регистра 1 сдвига образуют кольцо.

С выходов блока 4 кодовые комбинации подаются па блок коммутаций 6, образуюш.ий вторую ступень коммутации программы проверки, а с выходов блока 6 поступают минимальные функциональные тесты, которые за тем подаются на проверяемую микросхему 10.

Блок 6 обеспечивает необходимую коммутацию выходов проверяемой микросхемы к блоку измерений 7 и входов микросхемы 10 к блоку 4 в зависимости от типа проверяемой микросхемы.

Сигналы с выходов проверяемой микросхемы через блок коммутаций 6 поступают в блок 7, который служит для измерения и фиксации статических и динамических параметров проверяемой логической микросхемы, а также для ее проверки на функционирование.

Кодовые комбинации с выходов кольцевого регистра 1 сдвига формируются или на низкой частоте (десятые доли герца), что позволяет совместить проверку логической микросхемы 10 на функционирование с проверкой

по статическим параметрам, или на высокой частоте (несколько мегагерц), что позволяет совместить во времени проверку на функционирование с проверкой по динамическим параметрам.

Для реализации проверки логической микросхемы в динамическом режиме и одновременно на функционирование блок 7 содержит высокочастотный двухчастотный осциллограф.

На осциллографе в динамическом режиме наблюдают форму напряжения выхода данной проверяемой логической микросхемы и сравнивают с известной формой напряжения .выхода исправпой логической микросхемы данного типа, в случае несовпадения их форм проверяемую логическую микросхему признают негодной, а в случае совпадения--годной. Одновременно ироводятся измерения динамических параметров логических микросхем.

Предмет изобретения

Устройство для контроля логических микросхем, содержащее блок коммутаций, соединенпый с блоком измерений и блоком формирования сигналов, задаюш,ий генератор, отличаюш,ееся тем, что, с целью повышения производительности контроля, в него введен кольцевой регистр сдвига, выход которого соединен

с первым входом блока формирования сигналов, второй вход которого подключен к выходу кольцевого регистра сдвига через группу вентилей, и дешифратор, управляющий вход группы вентилей соединен с первым входом устройства, второй вход которого подключен к первому входу кольцевого регистра сдвига, второй вход которого соединен с выходом задающего генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для контроля интегральных схем | 1981 |

|

SU1029146A1 |

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

| Устройство для контроля интегральных микросхем памяти | 1983 |

|

SU1144154A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

Даты

1974-06-15—Публикация

1972-01-04—Подача