(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU842784A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1974 |

|

SU603985A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ | 1972 |

|

SU434404A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть исполь эовано при построении двоично-десятичных преобразователей. Известен преобразователь двоичных чисел в двоично-десятичные 1, содержащий группу элементов И, шифратор зквивалентов, -накопительный сумматор и распределитель импульсов. Недостаток этого преобразователя состоит в низком быстродействии, связанном с последовательной обработкой разрядов. Наиболее близким решением данной задачи по технической сушности и схемному решению является преобразователь двоичных чисел в двоич но-десятичные 2, содержащий злементы И, первые входы которых соединены с входами соответствующих разрядов входного кода, двбичнодесятичный шифратор, входы которого соединены с выходами злементов И, элементы ИЛИ, тет15ады двоично-десятичного сумматора, входы которых соединены с выходами соответствующих злементов ИЛИ, первые входы которых соединены с соответствующими выходами двоично-десятичного шифратора, блоки коррекции, информационные входь которых соединены с соответствующими выходами тетрад двоично-десятичного сумматора, распределитель импульсов, вход которого соединен с управляющими входами блоков коррекции и с тактовым входом преобразователя. Недостаток зтого преобразователя так же состоит в относительно низком быстродействии, связанном с возможностью многократного возникновения межтетрадного переноса. Целью изобретения является увеличение быстродействия при упрощении устройства. Поставленная цель достигается тем, что в преобразователе двоичных чисел в двоично-десятичные, содержащем злементы И, первые вмоды которых соединень с входами соответствующих разрядов входного кода, двоично-десятичный шифратор, входы которого соединены с выходами элементов И, злементы ИШ1, тетрады двоично-десятичного сумматора, входы которых соединены с выходами соответствующих злемеитов ИЛИ, первые входы которых соединены с соответствующими выходами двоишго-десятичного шифратора, блоки коррекции, информационные входы которых соединены с соответствующими

выходами тетрад двоично-десятичного сумматора, распределитель импульсов, вход которого соединен с управляющими входами блоков коррекции и с тактовым входом преобразователя, выходы распределителя импульсов соединены со вторыми входами с первого по одиннадцатьш элементов И rijpHieM первый выход распределителя импульсов соединен со вторыми входами четвертого элемента И, второй в;ыход распределителя .импульсов соединен со вторыми входами второго, третьего и.пятого элементов И, третий выход распределителя импульсов соединен со вторыми входами первого и шестого элементов И, четвертый вы- ход распределителя импульсов соединен со вторыми входами седьмого и восьмого элементов И, пятый выход распределителя импульсов соединен со вторыми входами девятого, десятого и одиннадцатого элементов И, причем для любого числа разрядов преобразуемого числа связи выходов распределителя импульсов со вторыми входами элементов И соотношением Р- + Р. i-2

л-Ц-где: PJ - межтетрадный перенос в двоично-десятичном сумматоре, i - номер выхода распределителя импульсов, а выход каждого блока коррекции через элементы ИЛИ соединен со входами второго и третьего разрядов соответствующей тетрады двоично-десятичного сумматора и со входом младшего разряда соседней старшей тетрады.

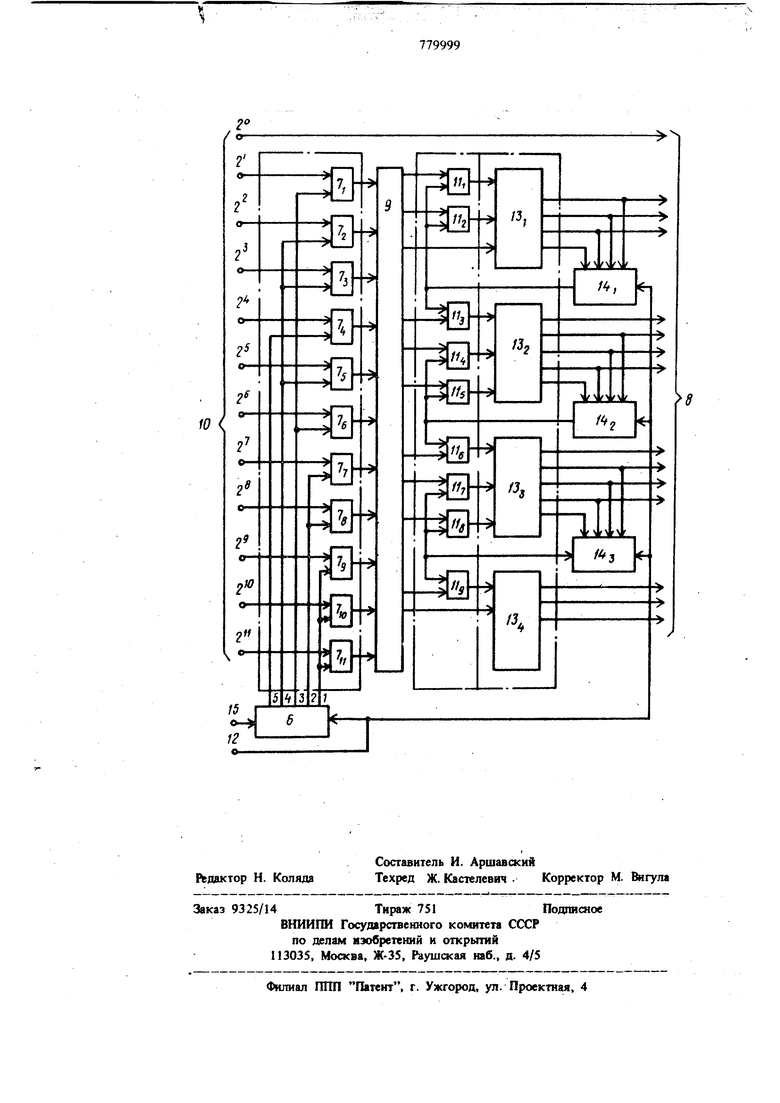

На чертеже представлена функциональная схема устройства.

Оно содержит выходы 1-5 распределителя импульсов 6, элементы И 7 - 7 ввода разрядов с первого по одиннадцатый входного числа с весами 2 ... 2 соответственно, выходы 8 преобразователя, двоично-десятич ы.й шифратор 9, ходы 10 двоичного числа, элементы ИЛИ 11 Vвход 12 тактовых импульсов, тетрады 13ц, двоично-десятичного сумматора, блоки коррекции 14 - 14,, вход 15 импульса начала преобразования.

Каждый такт преобразования состоит из двух полутактов. В первом полутакте (в течение тактового импульса) производится ввод числа, запись его в сумматор, выявление коррекции и переносов схемами коррекции. Во втором Г1олутакте (в течение паузы между тактовыми импульсами) производится коррекция числа записанного в сумматоре.

Преобразование происходит следующим образом. По входу 15 в устройство поступает импульс начала преобразования, запускаюи1ий в распределитель 6 импульсов, который формирует пять импульсов опроса, последовательно возникаюцщх на его выходах. При возникновении первого импульса на выходе распределителя икшульсов 6 открьшаются три элемента И 79, /iо, 7, 1 , соответствующие разрядам 2 , 2°, 2. Единицы со входов 10 этих разрядов,

если они имеются, поступают в двоично-десятичный шифратор 9, и сигналы с соответствующих выходов шифратора через элементы ИЛИ 11 подаются на входы тетрад двоично-десятичного сумматора 13. В этом же полутакте происходит выявление коррекции и переносов блоками коррекции Ид, которые формируют и запоминают сигнал коррекции, если чисдо, записанное в соответствующей тетраде сумматора больше или равно десяти.

Блок коррекции реализует логическую функцию;

4)%VP..

(s

К

V S.

2 тетрады

2 2 s.

где: S

SQ -выходы

:

а

соответственно; Р - выход переноса тетрады; К - сигнал коррекции.

Коррекции суммы и сложения переносов в первом полутакте не происходит, поэтому сигнал коррекции запоминается до начала полутакта коррекции.

Коррекция суммы и сложение переносов осуществляется добавлением числа шесть (ОНО) к содержимому тетрады сумматора, н добавлением единицы переноса к содержимому следующей старшей тетрады. Выявление коррекции и переносов в полутакте коррекдаи не происходит..

На этом заканчивается первый такт преобразования. В оставшиеся четыре такта преобразователь действует аналогично.

Предлагаемая группировка входных информационных шин исключает одновременную подачу двух сигналов на один вход сумматора.

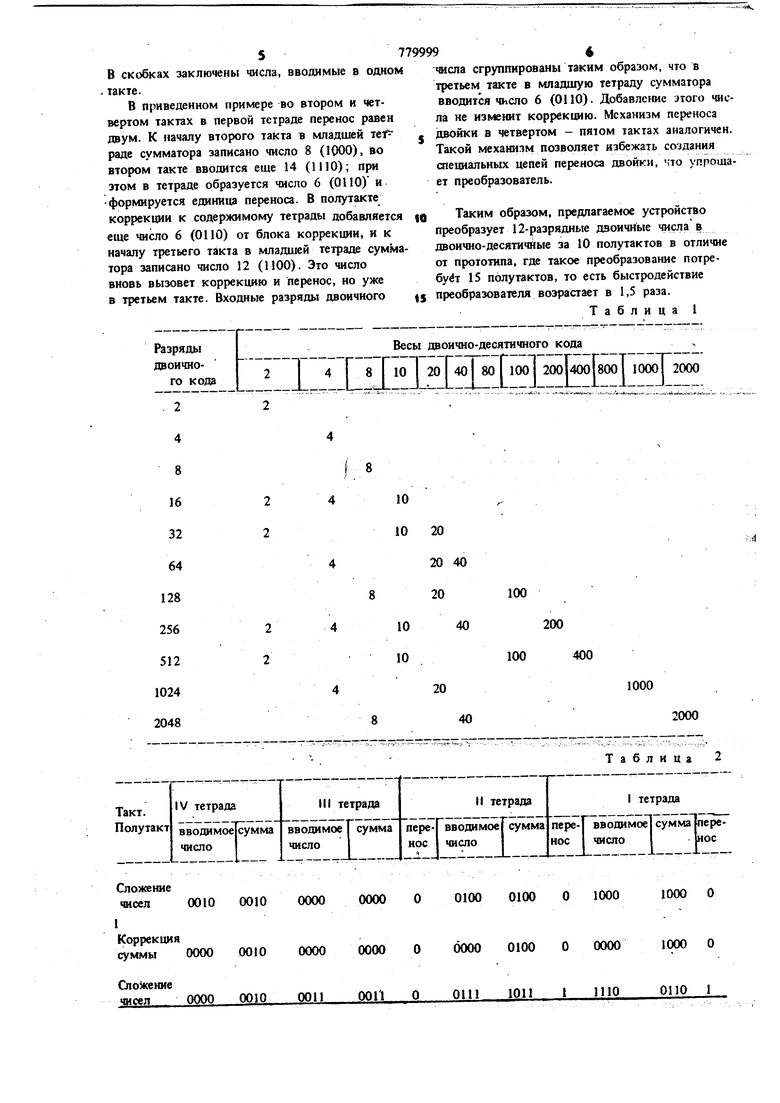

Распределение весов двоично-десятичного кода по разрядам двоичного кода приведено в табл. 1.

Каждый столбец таблицы соответствует какому-либо входу сумматора. Числа, стоящие в одном столбце, должны подаваться в сумматор в разные такты. Из таблицы видно, что для 12-разрядного числа минимально возможное число тактов - пять.

Другая особенность предлагаемого преобразователя заключается в следующем: если в процессе преобразования в каком-то такте пере- . нос равен двум, то в следующем такте перенос в данной тетраде отсутствует; это позволяет распространять перенос, равный двум, за два такта преобразования без усложнения устрюйства.

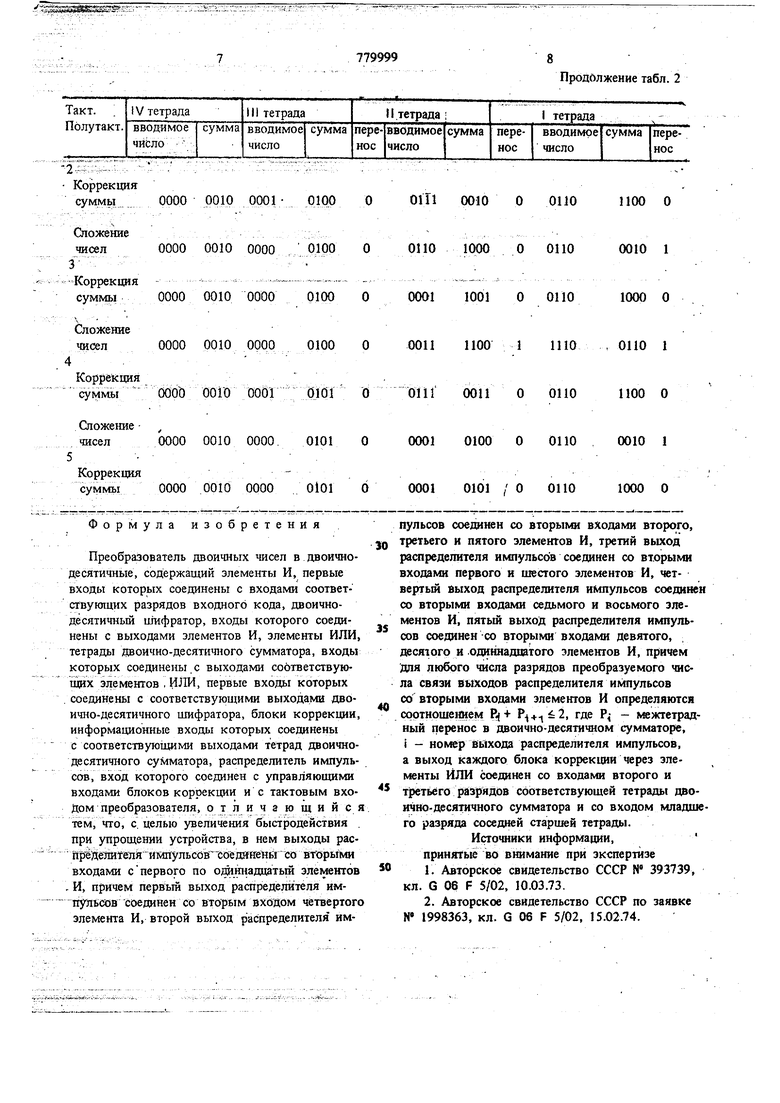

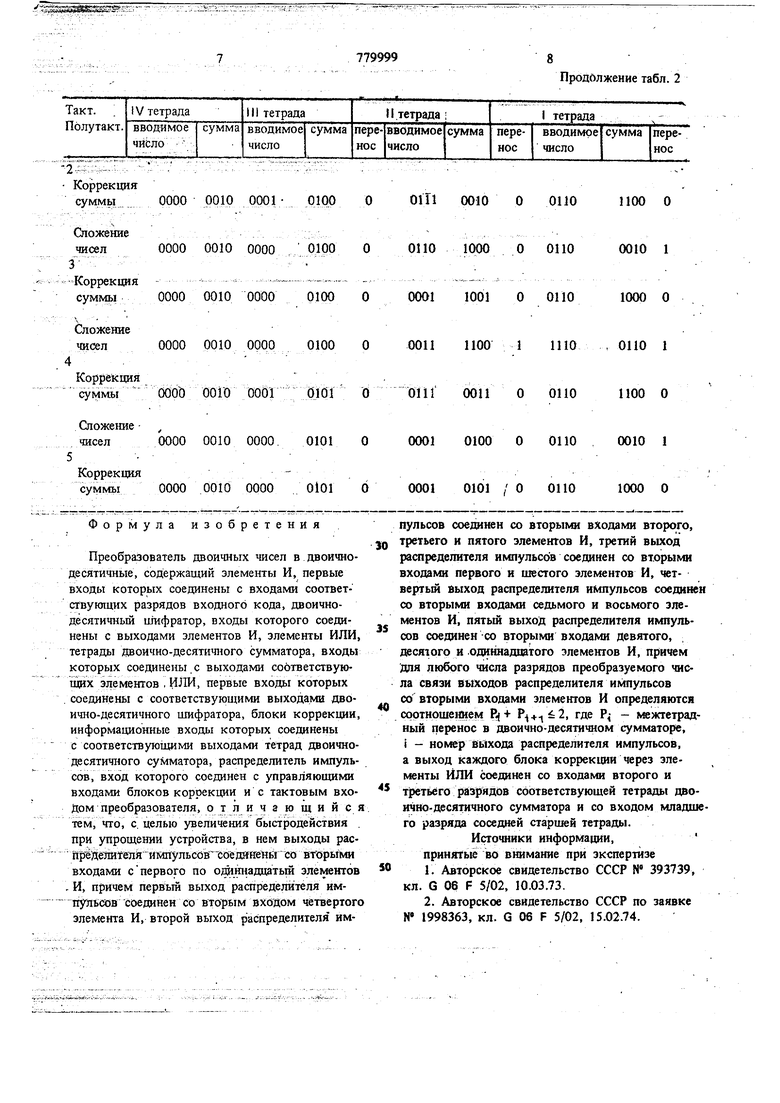

В табл. 2 в качестве примера, поясняющего особенности работы преобразователя, расписано по полутактам преобразование числа 2558.

2558-(2048)+(256+128)+(64+2)+(32+8+4)+ +(16) (2)+(2®+ 2) + ( 2)+ ( 2 +(2).. .

В скобках заключены числа, вводимые в одном . такте.

В приведенном примере во втором и четвертом тактах в первой тетраде перенос равен двум. К началу второго такта в младшей раде сумматора записано число 8 (1(ЮО), во втором такте вводится еще 14 (1110); при этом в тетраде образуется число 6 (ОНО) и формируется единица переноса. В полутакте коррекции к содержимому тетрады добавляется еще число 6 (ОНО) от блока коррекции, и к началу третьего такта в младшей тетраде сумматора записано число 12 (1100). Это число вновь вызовет коррекцию и перенос, но уже в третьем такте. Входные разряды двоичного

2 2

2 2 Сложение 0000 0000 О чисел0010 0010 Коррекция 0000 0000 о суммы 0000 0010 Сло кение ООП ООН о чисел 0000 0010

числа сгруппированы таким образом, что в третьем такте в младшую тетраду сумматора вводится число 6 (ОНО). Добавление лого числа не изменит коррекцию. Механизм переноса двойки а четвертом - пяюм тактах аналогичен. Такой мехашпм позволяет избежать создания специальных цепей переноса двойки, ;то упрощает преобразователь.

Таким образом, предлагаемое устройство преобразует 12-разрядные двоичные шсла в двоично-десятичйые за 10 полутактов в отличие от прототипа, где такое преобразование потребует 15 полутактов, то есть быстродействие

преобразователя возрастает в 1,5 раза.

Таблица 1

10

10 20

:4

20 40

100

20

200

1040 100400

10

1000

20 40

2000

Таблица 2 0100 0100 О 1000 1000 О 0000 0100 о 0000 1000 о 0111 1011 1 1110 оно 1

0000 0010 0001- 0100 О

0000 0010 0000 . 0100 О

- ..-...--. -.

0000 0010 0000 0100 О

0000 0010 0000 0100 О 0000 ООШ 0001 ; Ш01 О

,

0000 0010 0000. 0101 О

0000 0010 0000 OiOl О

Формула изобретения

Преобразователь двоичных чисел в двоичнодесятичные, содержащий элементы И, первые входы которых соединены с входами соответствующих разрядов входного кода, двоичнодесятичный игафратор, входы которого соединены с выходами элементов И, элементы ИЛИ, тетрады двоично-десятишого сумматора, входы которых соединены.с выходами соответствующих элементов , ИЛИ, первые входы которых соединены с соответствующими выходами двоично-десятичного шифратора, блоки коррекции, информационные входы которых соединены с соответствующими выходами тетрад двоичнодесятичного сумматора, распределитель импульсов, вход которого соединен с управляющими входами блоков коррекции и с тактовым входом преобразователя, отличающийся тем, что, cVцелью увеличения быстродействия . при упрощении устройства, в нем выходы рас прейеяйтелЯимпульсов соёдяненй со вгорьгми входами с первого по одйшидцатый элементов . И, причем первый выход распределителя импупьсов соединен со вторым входом четвертого элемента И, второй выход распределителя им779999

Продолжение табл. 2

ОП1 0010 о оно1100 о

оно 1000 о оно0010 1

0001 1001 о оно1000 о

ООН 1100 1 1110 ,0110 1

0111 ООН о оно ноо о

0001 0100 о оно0010 1

0001 0101 / о оно1000 о

пульсов соединен со вторыми входами второго, третьего и пятого элементов И, третий выход распределителя импульсов соединен со вторыми входакш первого и шестого элементов И, четвертый выход распределителя импульсов соединен со вторыми входами седьмого и восьмого элементов И, пятый выход распределителя импульсов соединен-со вторыми входами девятого, десятого и .одиннадцатого элементов И, причем для любого числа разрядов преобразуемого числа связи выходов распределителя импульсов со вторыми входами элементов И определяются сортношетем Е)Н , где Р - межгетрадный перенос в двоично-десятичном сумматоре, i - номер выхода распределителя импульсов, а выход каждого блока коррекции через элеNKHTbi ИЛИ соединен со входами второго и т ретьего разрядов соответствующей тетрады двоично-десятичного сумматора и со входом младшго разряда соседней старшей тетрады.

Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1980-11-15—Публикация

1978-02-02—Подача