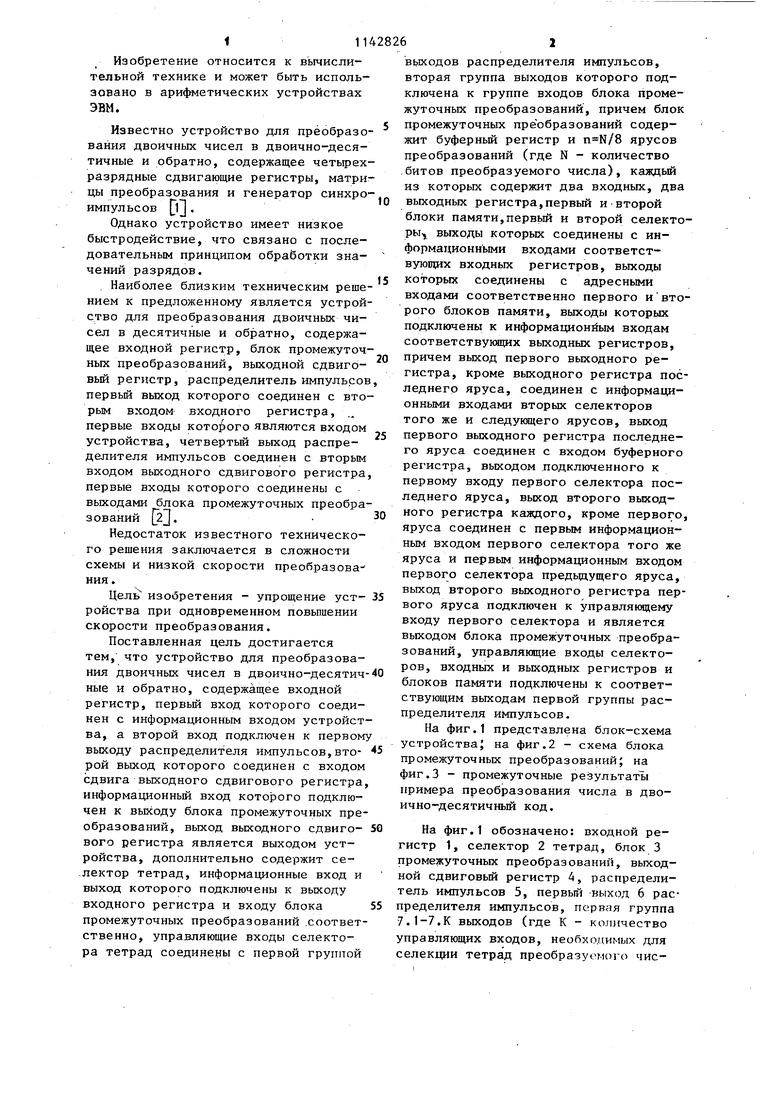

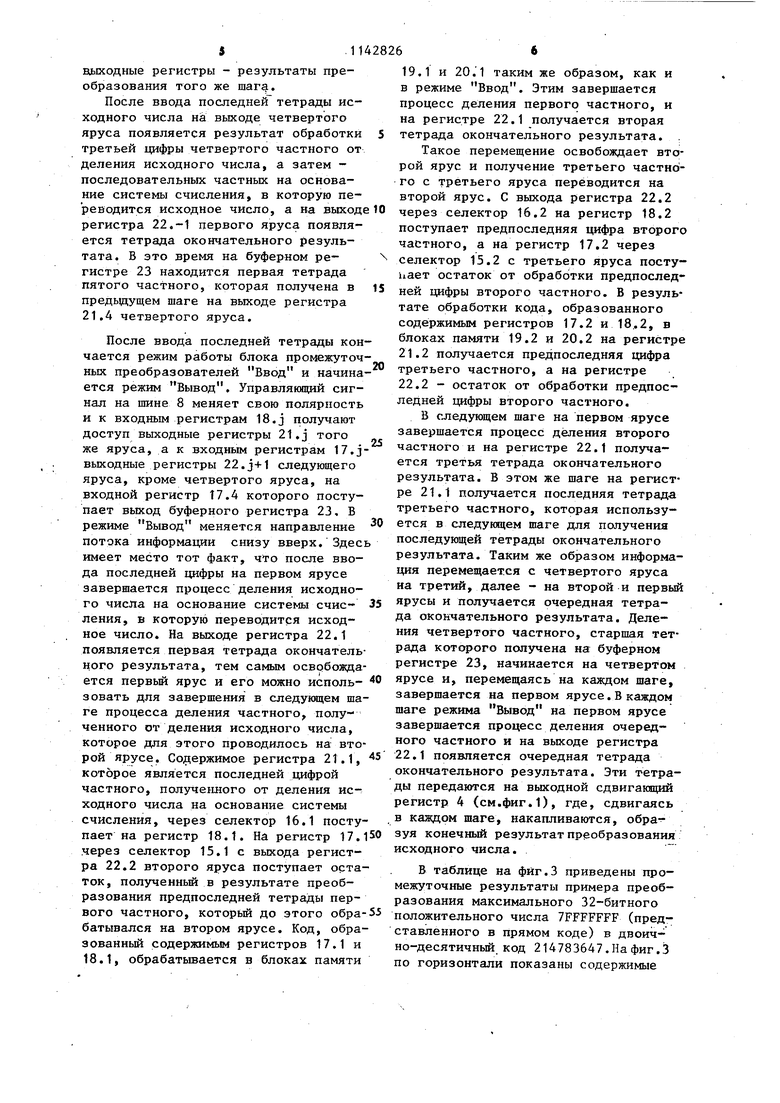

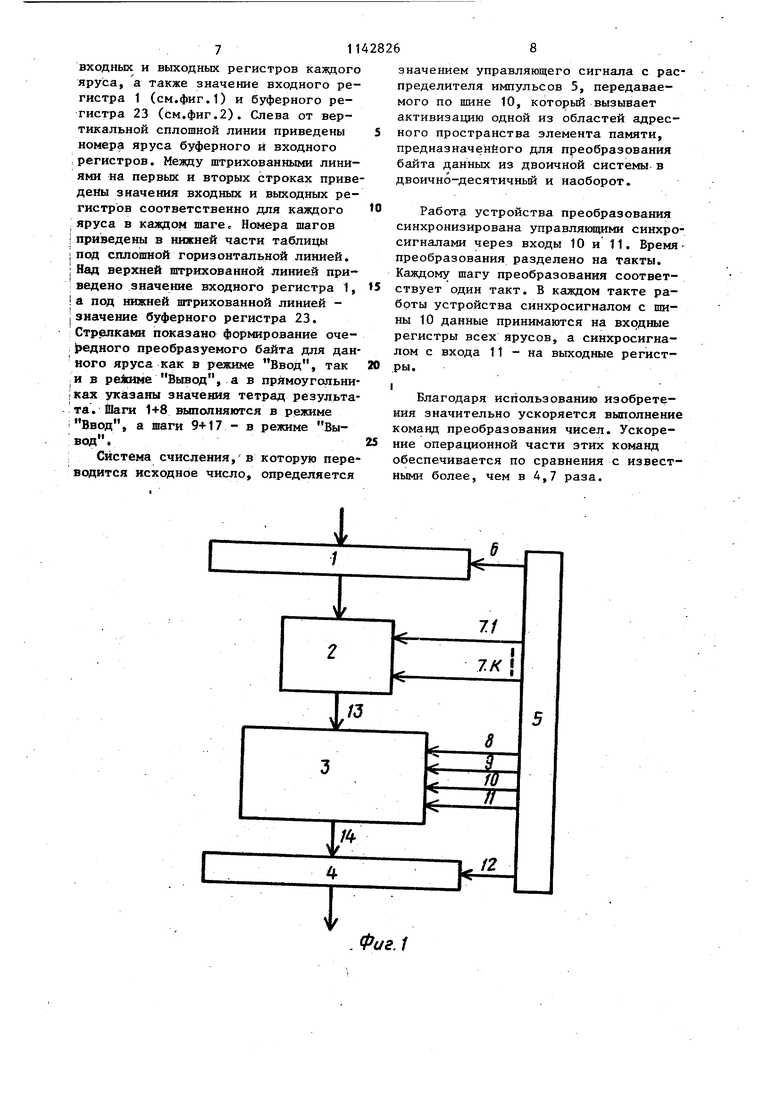

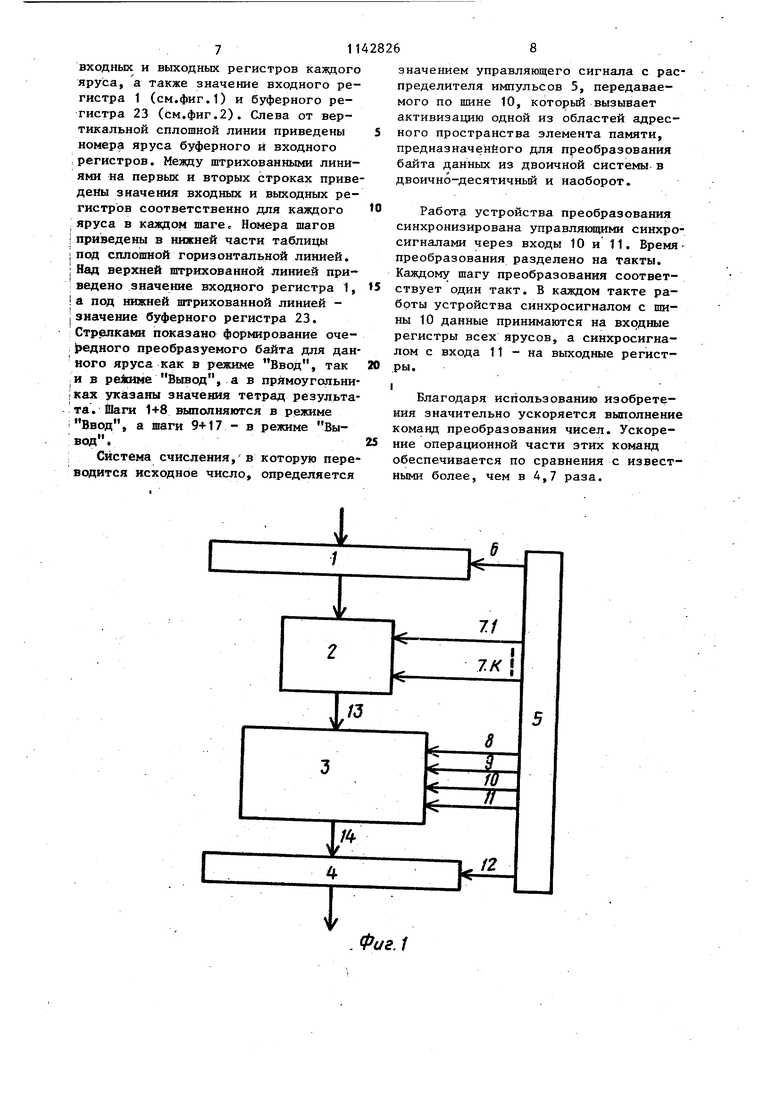

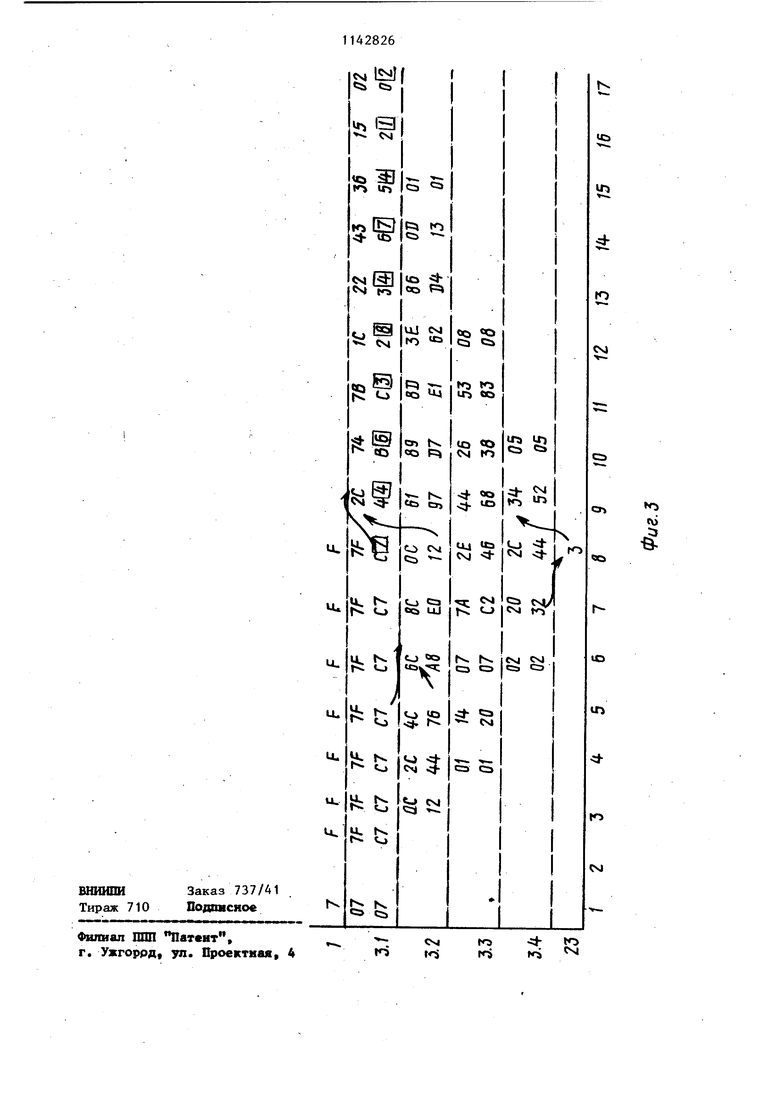

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ. Известно устройство для преобразования двоичных чисел в двоично-десятичные и обратно, содержащее четырехразрядные сдвигающие регистры, матри цы преобразования и генератор синхро импульсов р, Однако устройство имеет низкое быстродействие, что связано с последовательным принципом обработки значений разрядов. Наиболее близким техническим реше нием к предложенному является устрой ство для преобразования двоичных чисел в десятичные и обратно, содержащее входной регистр, блок промежуточ ных преобразований, выходной сдвиговьй регистр, распределитель импульсов первый выход которого соединен с вто рым входом входного регистра, первые входы которого являются входом устройства, четвертьм выход распределителя импульсов соединен с вторым входом выходного сдвигового регистра первые входы которого соединены с выходами блока промежуточных преобра зований (2J. Недостаток известного технического решения заключается в сложности схемы и низкой скорости преобразования. Цель изобретения - упрощение устройства при одновременном повышении скорости преобразования. Поставленная цель достигается тем, что устройство для преобразования двоичных чисел в двоично-десятич ные и обратно, содержащее входной регистр, первый вход которого соединен с информационным входом устройст ва, а второй вход подключен к первом выходу распределителя импульсов,второй выход которого соединен с входом сдвига выходного сдвигового регистра информационньй вход которого подключен к выходу блока промежуточных пре образований, выход выходного сдвигового регистра является выходом устройства, дополнительно содержит се.лектор тетрад, информационные вход и выход которого подключены к выходу входного регистра и входу блока промежуточных преобразований .соответ ственно, управляющие входы селектора тетрад соединены с первой группой вькодов распределителя импульсов, вторая группа выходов которого подключена к группе входов блока промежуточных преобразований, причем блок промежуточных преобразований содержит буферньм регистр и ярусов преобразований (где N - количество битов преобразуемого числа), каждый из которых содержит два входных, два выходных регистра,первый и второй блоки памяти,первьш и второй селекторы, выходы которых соединены с информационными входами соответствующих входных регистров, выходы которых соединены с адресными входами соответственно первого ивторого блоков памяти, выходы которых подключены к информационйым входам соответствукмцих выходных регистров, причем выход первого выходного регистра, кроме выходного регистра последнего яруса, соединен с информационными входами вторых селекторов того же и следукяцего ярусов, выход первого выходного регистра п.оследнего яруса соединен с входом буферного регистра, выходом подключенного к первому входу первого селектора последнего яруса, выход второго выходного регистра каждого, кроме первого, яруса соединен с первым информационным входом первого селектора того же яруса и первым информационным входом первого селектора предьдущего яруса, выход второго выходного регистра первого яруса подключен к управлякицему входу первого селектора и является выходом блока промежуточных преобразований, управлякщие входы селекторов, входных и выходных регистров и блоков памяти подключены к соответствующим выходам первой группы распределителя импульсов. На фиг.1 представлена блок-схема устройстваJ на фиг.2 - схема блока промежуточных преобразований; на фиг.З - промежуточные результат примера преобразования числа в двоично-десятичный код. На фиг.1 обозначено: входной регистр 1, селектор 2 тетрад, блок 3 промежуточных преобразований, выходной сдвиговый регистр А, распределитель импульсов 5, первый выход 6 распределителя импульсов, первая группа 7.1-7.К выходов (где К - количество управляющих входов, необходимых для селекции тетрад преобразуемого числа) распределителя импульсов, вторая группа выходов 8-11 распределителя импульсов, второй выход 12 распределителя импульсов, вход 13 и выход 14 блока промежуточных преобразований. Блок 3 промежуточных преобразований (см.фиг;2) содержит ярусов пре образований 3.1-3,j, где N количество битов преобразуемого числа, j 1,2,..., п, и буферный регистр 23, Каждый ярус блока промежуточных преобразований содержит первьш и второй селекторы 15, 16, два входных регист ра 17, 18, первый и второй блоки памяти 19, 0, два выходньк регистра 21, 22, буферный регистр 23 блока промежуточных преобразований. Рассмотрим работу устройства на примере, когда количество битов преобразуемого числа . Тогда , . . Число, подлежащее преобразованию, поступает на регистр 1, с выхода которого тетрады этого числа поочередно, под управлением сигналов, поступающих по шинам 7. распределителя импульсов, начиная со старшей тетрады, через селектор тетрад 2, поступают на вход 13 блока промежуточных преобразований, далее под управлени- ем сигнала, поступающего по шине 8 через селектор 16.1, Поступают на регистр 18.1 (см.фиг.2). Восьмибитный код информации с выходов входных регистров 17.1 и 18.1 поступает на адресные входы блоков памяти 19.1 и 20,1, выполнякщих функцию преобразования входной информации из двоичной системы в двоично-десятичную и наоборот. В исходный момент, когда на входной регистр 18.1 передается старшая тетрада преобразуемого числа, входной регистр 17.1 имеет нулевое значение. Информация этой тетрады преобразуется из одной системы в другую и помещается в регистры 21.1 и 22.1. Например, в режиме десятичного преобразования, если двоичный код старшей тетрады преобразуемого числа имеет значение 1100 (С), то код 0000 1100 (ОС), образованньй содержимым регистров 17.1 и 18.1, nodTynaeT на входы блоков памяти 19.1 и 20,1, на выходах которых появляется код 0001 0010 (12.), представляющий собой двоично-десятичный код двоичного числа 1100 (С), причем старшая тетрада 0001(1) двоично-десятичного кода 12 появляется на выходе блока памяти 19.1, а мпадшая тетрада 0010 (2) - на выходе блока памяти 20.1. Это двоично-десятичное число с выходов блоков памяти 19.1 и 20.1 принимается соответственно на регист ры 21.1 и 22.1. Старшая тетрада этого кода (0001) представляет собой старшую шестна ;цатиричную цифру двоичного числа (частного), получаемого от деления исходного двоичного числа на основании системы счисления, в которую переводится исходное число (в данном случае на 10). Эта тетрада на втором ярусе подвергается такому же преобразованию, как и старшая тетрада исходного числа на первом ярусе. Одновременно с передачей старшей тетрады исходного числа-на второй ярус младшая тетрада (0010) этого числа с выхода регистра 22.1 поступает на входной регистр 17.1 через селектор 15,1 первого яруса, а на регистр 18.1 через селектор 16.1 поступает вторая тетрада исходного числа. Если, например, эта тетрада имеет значение tMI(F), то код 0010 1111(2F), образованньй содержимым регистров17.1 и 18.1, преобразуется в блоках памяти 19.1 и 20.1 в двоично-десятичный код, который равен 47 (0100, 0111), и передается на выходные регистры 21.1 и 22.1. Одновременно с получением на выходе первого яруса результата преобразования второй тетрады на выходе второго яруса получается результат преобразования старшей тетрады частного, полученного в предьщущем шаге на выходе первого яруса. Затем старшая тетрада результата преобразования с выхода второго яруса передается на вход третьего яруса, младшая тетрада - на вход того же яруса, а старшая тетрада с выхода первого яруса поступает на вход второго яруса, младшая тетрада - на вход того же яруса, которая совместно с третьей тетрадой исходного числа, поступившей в это время на входной регистр 18.1 первого яруса, образует новый байт для дальнейшей обработки. Таким образом, устройство работает онвейерньв 1 способом. В каждом шаге реобразования на входные регистры сех ярусов поступают результаты пребразования предьщущего шага, а на выходные регистры - результаты преобразования того же шаг§. После ввода последней тетрады исходного числа на выходе четвертого яруса появляется результат обработки третьей цифры четвертого частного от деления исходного числа, а затем - последовательных частных на основание системы счисления, в которую переводится исходное число, а на выходе регистра 22.-1 первого яруса появляется тетрада окончательного результата. В это время на буферном ре- гистре 23 находится первая тетрада пятого частного, которая получена в предьиущем шаге на выходе регистра 21.4 четвертого яруса. После ввода последней тетрады кон чается режим работы блока промежуточ ных преобразователей Ввод и начина ется режим Вывод. Управляющий сигнал на глине 8 меняет свою полярность и к входным регистрам 18.J получают доступ выходные регистры 21.J того же яруса, а к входным регистрам 17.J выходные регистры 22.J+1 следующего яруса, кроме четвертого яруса, на входной регистр Т7.4 которого поступает вькод буферного регистра 23, В режиме Вывод меняется направление потока информации снизу вверх. Здес имеет место тот факт, что после ввода последней цифры на первом ярусе завершается процесс деления исходного числа на основание системы счисления, в которую переводится исходное число. На выходе регистра 22.1 появляется первая тетрада окончатель ного результата, тем самым освобожда ется первьй ярус и его можно использовать для завершения в следукнцем ша ге процесса деления частного, полученного от деления исходного числа, которое для этого проводилось на вто рой ярусе. Содержимое регистра 21.1, которое является последней цифрой частного, полуЧеьшого от деления исходного числа на основание системы счисления, через селектор 16.1 посту пает на регистр 18.1. На регистр 17. через селектор 15.1 с выхода регистра 22.2 второго яруса поступает оста ток, полученный в результате преобразования предпоследней тетрады первого частного, которьй до этого обра батывался на втором ярусе. Код, обра зованный содержимым регистров 17.1 и 18.1, обрабатывается в блоках памяти 19.1и 20.1 таким же образом, как и в режиме Ввод. Этим завершается процесс деления первого частного, и на регистре 22.1 получается вторая тетрада окончательного результата. . Такое перемещение освобождает второй ярус и получение третьего частного с третьего яруса переводится на второй ярус. С выхода регистра 22.2 через селектор 16.2 на регистр 18.2 поступает предпоследняя цифра второго частного, а на регистр 17.2 через селектор 15.2 с третьего яруса постуiiaeT остаток от обраббтки предпоследней цифры второго частного. В результате обработки кода, образованного содержимым регистров 17.2 и 18..2, в блоках памяти 19.2 и 20.2 на регистре 21.2получается предпоследняя цифра третьего частного, а на регистре 22.2 - остаток от обработки предпоследней цифры второго частного. В следующем шаге на первом ярусе завершается процесс деления второго частного и на регистре 22.1 получается третья тетрада окончательного результата. В этом же шаге на регистре 21.1 ползгчается последняя тетрада третьего частного, которая используется в следукидем шаге для получения последующей тетрады окончательного результата. Таким же образом информация перемещается с четвертого яруса на третий, далее - на второй и первый ярусы и получается очередная тетрада окончательного результата. Деления четвертого частного, старшая тетрада которого получена на буферном регистре 23, начинается на четвертом ярусе и, перемещаясь на каждом шаге, завершается на первом ярусе. В каждом шаге режима Вывод на первом ярусе завершается процесс деления очередного частного и на выходе регистра 22.1 появляется очередная тетрада окончательного результата. Эти тетрады передаются на выходной сдвигающий регистр 4 (см.фиг.1), где, сдвигаясь в каждом шаге, накапливаются, образуя конечный результат преобразования: исходного числа. В таблице на фйг.З приведены промежуточные результаты примера преобразования максимального 32-битного положительного числа 7FFFFFFF (представленного в прямом коде) в двоично-десятичньм. код 214783647.На фиг.3 по горизонтали показаны содержимые входных и выходных регистров каждого яруса, а также значение входного регистра 1 (см.фиг.1) и буферного регистра 23 (см.фиг.2). Слева от вертикальной сплошной линии приведены номера яруса буферного и входного ;регистров. Между штрихованными линиями на первых и вторых строках приведены значения входных и выходных регистров соответственно для каждого яруса в каждом шаге. Номера шагов I приведены в нижней части таблицы I под сплошной горизонтальной линией. I Над верхней штрихованной линией приI ведено значе:ние входного регистра 1, I а под нижней штрихованной линией I значение буферного регистра 23. Стрелками показано формирование очередного преобразуемого байта для дан ного яруса как в режиме Ввод, так ив реАоше Вывод, а в прямоугольни 1ках указаны значения тетрад результа .та. Шаги 1+8 выполняются в режиме Ввод, а шаги 9+17 - в режиме Вывод. Система счисления, в которую пере водится исходное число, определяется значением управляющего сигнала с расределителя импульсов 5, передаваемого по шине 10, который вызывает активизацию одной из областей адресного пространства элемента памяти, предназначенйого для преобразования байта данных из двоичной системы-в двоично-десятичньй и наоборот. Работа устройства преобразования синхронизирована управляющими синхросигналами через входы 10 и 11. Времяпреобразования разделено на такты. Каждому шагу преобразования соответствует один такт. В каждом такте работы устройства синхросигналом с шины 10 данные принимаются на входные регистры всех ярусов, а синхросигналом с входа 11 - на выходные регистры. Благодаря использованию изобретения значительно ускоряется выполнение команд преобразования чисел. Ускорение операционной части этих команд обеспечивается по сравнения с известными более, чем в Д,7 раза.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1986 |

|

SU1388995A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1662004A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ ЧИСЕЛ В ДВОИЧНО-ДЕСЯТИЧНЫЕ И ОБРАТНО, содержащее входной регистр, первый вход которого соединен с информационным входом устройства, а второй вход подклкссен к первому выходу распределителя импульсов, второй выход которого соединен с входом сдвига ВЫХОДНОГО сдвигового регистра, информационный вход которого подключен к выходу блока промежуточных преобразований, выход выходного СДВИГОВОГО регистра является выходом устройства, отличающееся тем, что, с целью его упрощения, оно дополнительно содержит селектор тетрад, информа ционные вход и выход которого подключены к выходу входного регистра и входу блока промежуточных преобразований соответственно, управляющие входы селектора тетрад соединены с первой Группой выходов распределителя импульсов, вторая группа выходов которох-о подключена к группе входов блока промежуточных преобразований, причем блок промежуточных преобразований содержит буферный регистр и П W/8 ярусов преобразований (где N - количество битов преобразуемого числа), каждый из которых содержит два входных, два выходных регистров, первьй и второй блоки памяти, первый и второй селекторы, выходы которых соединены с информационными входами соответствую щх входных регистров, выходы которых соединены с адресными входами соответственно первого и второгоблоков памяти, выходы которых подключены к информационным входам соответствующих выходных регистров, причем выход первого ВЫХОДНОГО регистра, кроме выходного регистра последнего яруса, соединен с информационными входами (Л вторых селекторов того же и следующего ярусов, выход первого выходного регистра последнего яруса соединен с входом буферного регистра, выходом подключенного к первому входу первого селектора последнего яруса, выход второго ВЫХОДНОГО регистра 4 каждого, кроме первого, яруса соедиISD нен с первым информационным входом первого селектора того же яруса и 00 первым информационным входом первого го селектора предьщущего яруса, выход Од второго ВЫХОДНОГО регистра первого яруса подключен к управляющему входу первого селектора и является выходом блока промежуточных преобразований, управляющие входы селекторов, входных и выходных регистров и блоков памяти подключены к соответствующим выходам первой группы распределителя импульсов.

I

Фиг.1

Фие. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ПРОГНОЗИРОВАНИЯ ДЛИТЕЛЬНОСТИ ТЕЧЕНИЯ ОСТРОЙ ПНЕВМОНИИ | 2007 |

|

RU2325102C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент Великобритании № 1544015, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1985-02-28—Публикация

1983-08-03—Подача