1

Изобретение относится к технике обработки импульсных сигналов в системах обмена информацией.

Известные накопители импульсных сигналов содержат регистры сдвига, число разрядов в каждом из которых равно числу позиций в одном цикле накопления, генератор тактовых импульсов, решающий блок и квантователь входного сигнала по амплитуде.

Цель изобретения - повышение помехоустойчивости устройства без существенного увеличения регистров сдвига.

Указанная цель достигается тем, что в накопитель введены дешифраторы максимального положительного и максимального отр1Г цательного числа, две схемы «Р1ЛИ, две схемы «И, инвертор, блок установки и /г-разрядный реверсивный счетчик, выходы которого соединены с соответствующими входами регистров сдвига и дешифраторами. Выходы дешифраторов подключены соответственно ко входам схем «ИЛИ, другие входы которых соединены с выходами схем «И. Одна из этих схем подключена к выходу квантователя непосредственно, а другая - через инвертор. Входы схем «И подключены к генератору тактовых импульсов. Выходы схем «ИЛИ подключены соответственно ко входам сложения и вычитания реверсивного счетчика, входы установки которого через блок установки

2

соединены с соответствующими выходами регистров сдвига.

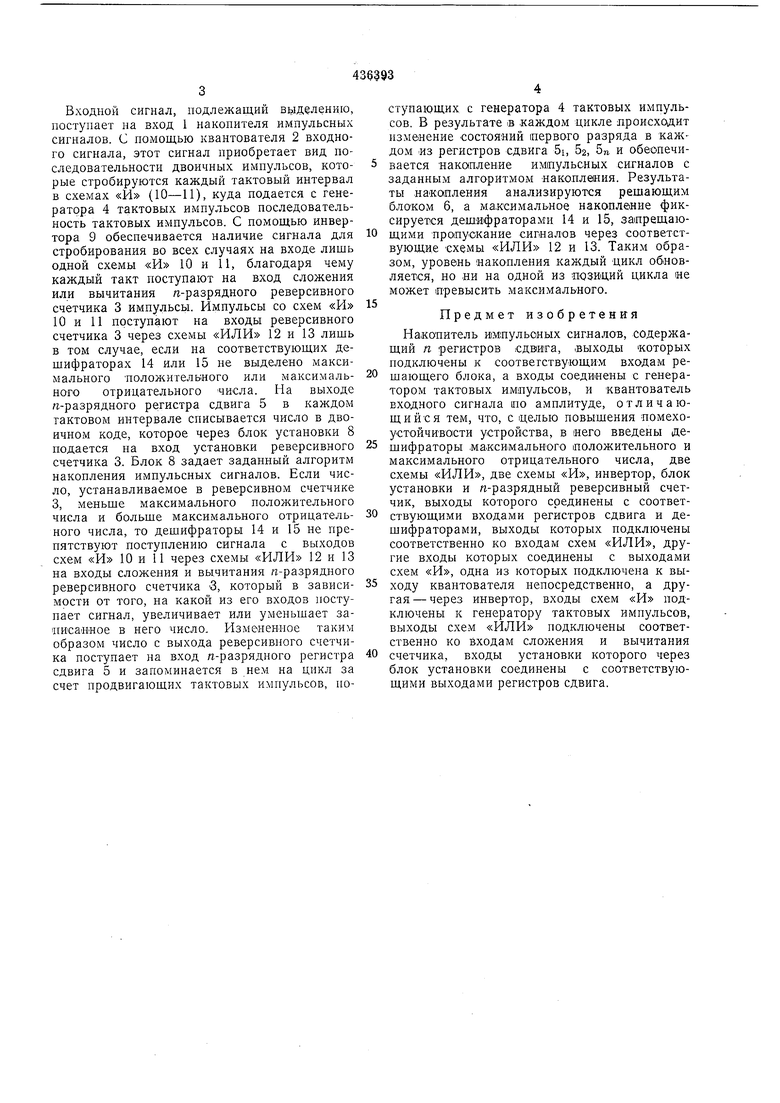

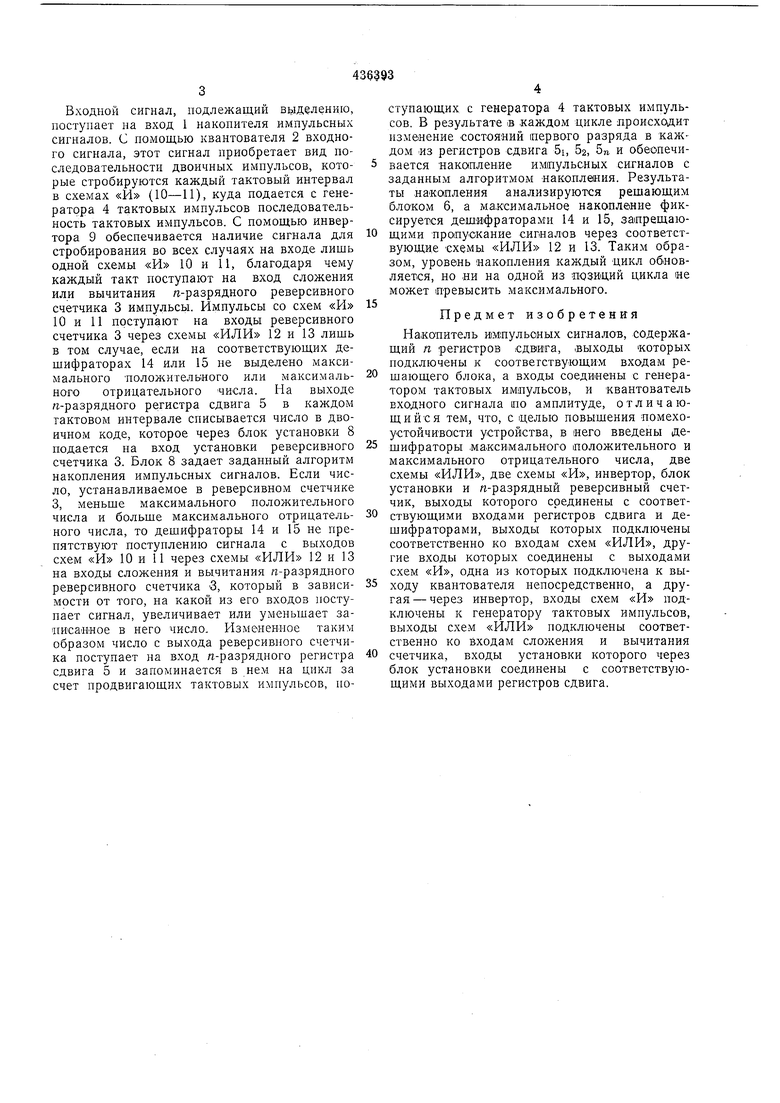

Блок-схема накопителя импульсных сигналов приведена на чертеже.

Накопитель содержит подключенный ко входу 1 квантователь 2 входного сигнала по амплитуде, который преобразует входной сигнал в вид, удобный для накопления; «-разрядный реверсивный счетчик 3, с помощью

которого производится установка уровня накопления по результатам анализа входного сигнала и данных запоминания; генератор 4 тактовых импульсов, управляющий работой накопителя; я регистров сдвига 5, которые

обеспечивают запоминание накопительного уровня сигнала на всех тактовых позициях цикла в виде п-разрядного кодового слова; решающий блок 6, подключенный к выходу 7 накопителя, блок установки 8, служащий для

передачи уровня сигнала в «-разрядном регистре сдвига 5 на «-разрядный реверсивный счетчик 3, схему-инвертор «ИЕ 9, схемы «И 10 и 11 и схемы «ИЛИ 12 и 13, с помощью которых данные об уровне входного сигнала

переносятся с квантователя 2 на реверсивный счетчик 3; дешифраторы 14 и 15 максимального и минимального числа, служащие для ограничения уровня накопления и защиты от перехода с одного крайнего накопленного

уровня накопления на другой.

Входной сигнал, подлежащий выделению, поступает на вход 1 накопителя импульсных сигналов. С помощью квантователя 2 входного сигнала, этот сигнал приобретает вид последовательности двоичных импульсов, которые стробируются каждый тактовый интервал в схемах «И (10-11), куда подается с генератора 4 тактовых импульсов последовательность тактовых импульсов. С помощью инвертора 9 обеспечивается наличие сигнала для стробирования во всех случаях на входе лишь одной схемы «И 10 и 11, благодаря чему каждый такт поступают на вход сложения или вычитания п-разрядного реверсивного счетчика 3 импульсы. Импульсы со схем «И 10 и И поступают на входы реверсивного счетчика 3 через схемы «ИЛИ 12 и 13 лишь в том случае, если на соответствующих дешифраторах 14 или 15 не выделено максимального положительного или максимального отрицательного числа. На выходе м-разрядного регистра сдвига 5 в каждом тактовом интервале списывается число в двоичном коде, которое через блок установки 8 подается на вход установки реверсивного счетчика 3. Блок 8 задает заданный алгоритм накопления импульсных сигналов. Если число, устанавливаемое в реверсивном счетчике 3, меньше максимального положительного числа и больше максимального отрицательного числа, то дешифраторы 14 и 15 не препятствуют поступлению сигнала с выходов схем «И 10 и 11 через схемы «ИЛИ 12 и 13 на входы сложения и вычитания «-разрядного реверсивного счетчика 3, который в зависимости от того, на какой из его входов поступает сигнал, увеличивает или уменьшает заиисаиное в него число. Измененное таким образом число с выхода реверсивного счетчика поступает на вход я-разрядного регистра сдвига 5 и запоминается в нем на цикл за счет продвигающих тактовых импульсов, поступающих с генератора 4 тактовых импульсов. В результате в каждом цикле происходит изменение состояний первого разряда в каждом из регистров сдвига 5i, 62, 5п и обеопечи5 вается накапление импульсных сигналов с заданным алгоритмом Накопления. Результаты накопления анализируются решающим блоком 6, а максимальное накопление фиксируется дешифраторами 14 и 15, залрещаю0 щими пропускание сигналов через соответствующие схемы «ИЛИ 12 и 13. Таким образом, уровень накопления каждый -цикл обновляется, но ни на одной из эдзИЦий цикла не может превысить максимального.

Предмет изобретения

Иакопитель импульсных сигналов, содержащий п регистров сдвига, выходы которых подключены к соотвегствующим входам решающего блока, а входы соединены с генератором тактовых импульсов, и квантователь входного сигнала по амплитуде, отличающийся тем, что, с целью повышения помехоустойчивости устройства, в него введены дешифраторы максимального положительного и максимального отрицательного числа, две схемы «ИЛИ, две схемы «И, инвертор, блок установки и п-разрядный реверсивный счетчик, выходы которого соединены с соответствующими входами регистров сдвига и дешифраторами, выходы которых подключены соответственно ко входам схем «ИЛИ, другие входы которых соединены с выходами схем «И, одна из которых подключена к выходу квантователя непосредственно, а другая - через инвертор, входы схем «И подключены к генератору тактовых импульсов, выходы схем «ИЛИ подключены соответственно ко входам сложения и вычитания

счетчика, входы установки которого через блок установки соединены с соответствующими выходами регистров сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудный временной квантователь с регулируемым порогом | 1982 |

|

SU1345150A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| СПОСОБ ОБНАРУЖЕНИЯ ЦЕЛЕЙ ИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ И РАДИОЛОКАЦИОННАЯ СТАНЦИЯ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2270461C2 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для синхронизации контрольного и эталонного цифровых измерительных сигналов | 1983 |

|

SU1167714A1 |

| Устройство для задержки импульсов | 1982 |

|

SU1077046A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

Авторы

Даты

1974-07-15—Публикация

1972-03-20—Подача