(54) ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

IEPIOB

ЛПЧП fp ФиПД OisUi

входом арифметического устройства, четвертым выходом подключенного к первому входу схемы готовности ариф Метического устройства, второй вход и выход которой соединены соответственно с четвертым выходом и пятым входом устройства управления.

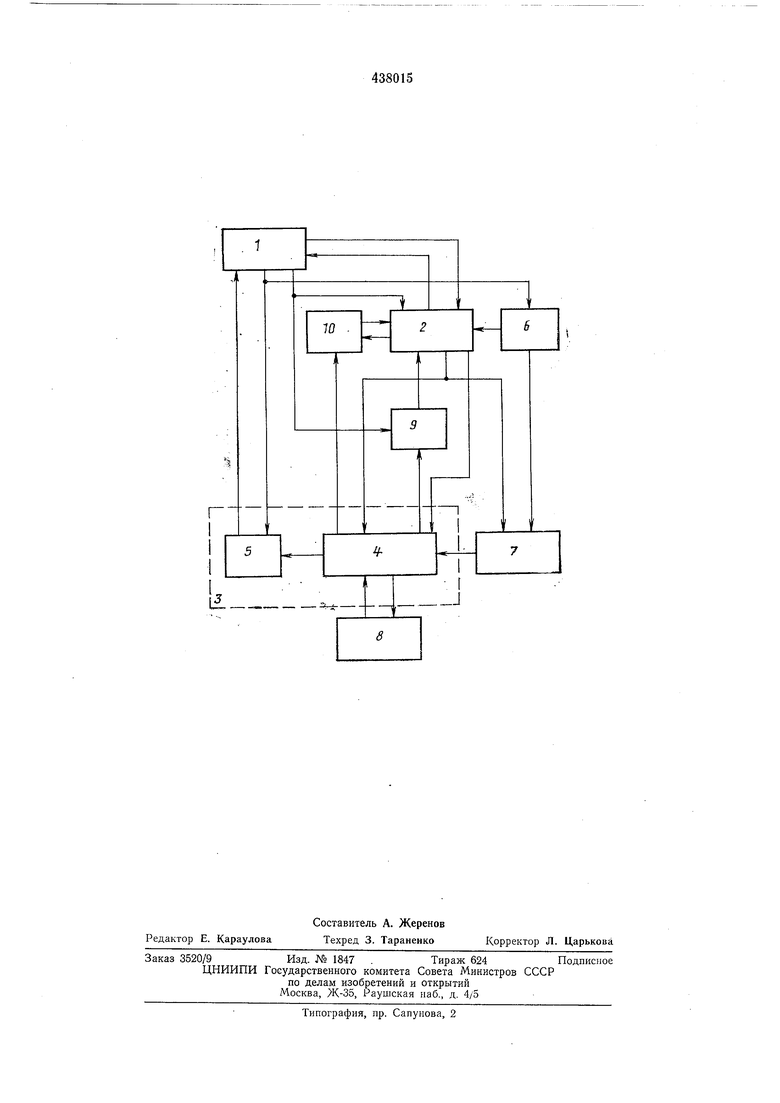

На чертеже представлена схема предлагаемого процесса.

Схема содержит запоминающее устройство 1; устройство 2 управления; арифметическое устройство 3, в состав которого входят блок 4 управления и блок 5 операций; регистр 6 команд; регистр 7 кодов арифметических операций, регистр 8 групп кодов; схему 9 разрешения запроса памяти; схему 10 готовности арифметического устройства.

Центральный процессор работает следующим образом.

Устройство 2 управления вырабатывает сигнал запроса очередной команды из запоминающего устройства 1 и ее адрес. Выбранная команда из запоминающего устройства 1 поступает в регистр 6 команд. Устройство управления производит расшифровку этой команды по следующим признакам:

требуется ли обращение к запоминающему устройству за числом или нет; содержит ли команда арифметические операции или нет; ждущая команда или нет.

Если требуется выборка из запоминающего устройства чисел, то устройство управления вырабатывают сигнал запроса запоминающего устройства по требуемому адресу. Если расшифрованная команда окажется неарифметической и неждущей, то она выполняется в устройстве управления. При этом запрос запоминающего устройства на выборку следующей команды формируется в устройстве управления по сигналу готовности памяти из запоминающего устройства, не ожидая окончания выполнения этой операции.

При арифметической операции параллельно с запросом чисел из запоминающего устройства производится перепись кода операции из регистра 6 команд в регистр 7 кодов арифметических операций по сигналу из устройства 2 управления при условии поступления разрещения в устройство 2 из схемы 10 готовности арифметического устройства.

По этому сигналу в блоке 4 управления арифметического устройства 3 формируется сигнал разрешения приема операндов из запоминающего устройства 1 в блок 5 операций арифметического устройства 3. Формирование запроса следующей команды при выполнении арифметических операций производится в устройстве управления по сигналу из схемы 9 разрешения запроса памяти, который формируется при наличии сигнала готовности памяти из запоминающего устройства 1 и сигнала из блока 4 арифметического устройства 3 (прие.ма операндов в блок 5 арифметического устройства 3), не дожидаясь выполнения этой операции. Из регистра 7 код операции поступает на дешифратор в блок 4 управления

арифметического устройства 3. С дешифратора расшифрованный код операции поступает на определенные схемы арифметического устройства 3 для выработки управляющих сигналов, которые необходимы при выполнении иервой половины арифметических операций. Одновременно он фиксируется в соответствующих триггерах регистра 8 грунп кодов. Сигналы с этих триггеров участвуют в формироваНИИ блоком 4 управления арифметического устройства 3 управляющих сигналов, необходимых при завершении арифметических операций. Наличие регистра 8 групп кодов позволяет,

не дожидаясь конца арифметической операции, начать выполнение следующей арифметической операции, так как к определенному моменту времени, которому соответствует выработка сигнала готовности арифметического

устройства, приемные регистры кода и операндов можно использовать для приема новой информации, не нарушая завершения выполнения предыдущей операции. Начало выполнения этой арифметической операции аналогично вышеприведенной. При этом запрос и выборка следующей команды производится аналогично предыдущей. Таким образом, при выполнении арифметической операции производится выборка следующей команды и ее операндов, и если она окажется арифметической, то в определенный момент выполнения предыдущей арифметической операции начинаегся ее выполнение в арифметическом устройсгве 3, и одновременно производится выборка.следующей команды из запоминающего устройства 1.

В отличие от частичного совмещения двух последовательно выполняемых арифметических операций, неждущие неарифметические

операции совмещаются полностью с выполнением длНННОЙ арифметической операции, так как те и другие выполняются в разных устройствах процессора независимо друг от друга. Это происходит следующим образом.

После приема кода арифметической операции в регистр 7 операндов в приемные регистры арифметического устройства 3 производится выборка следующей команды, сигнал запроса которой формируется в устройстве 2 унравления по сигналу со схемы 9 разрешения запроса памяти, и если она окажется неарифметической и неждушей, то ее выполнение нронзводится так, как было описано выше, а запросы последующих команд формируются устройством управления по сигналу готовности памяти.

Если какая-либо из команд неарифметической и ждущей конца арифметической операции, выполнение ее и запрос следующей начинается после поступления сигнала со схемы 10 готовности арифметического устройства.

При неарифметической операции из арифметического устройства 3 подается разрещающий

сигнал, и выходной сигнал определяется сигналом, поступающим из устройства 2 управления.

Если выполняется арифметическая операция, то после расшифровки кода операции схема 10 готовности арифметического устройства запирается сигналом из арифметического устройства 3. В момент времени, когда приемные регистры кода операции и операндов арифметического устройства 3 не требуются для дальнейшего выполнения арифметической операции, блок 4 управления арифметического устройства 3 вырабатывает разрешающий сигнал на входе схемы 10 готовности арифметического устройства.

Предмет изобретения

Центральный процессор, содержащий устройство управления, арифметическое устройство, запоминающее устройство, первый и второй входы которого соединены соответственно с первыми выходами устройства управления и арифметического устройства, первый выход запоминающего устройства подключен к первому входу устройства управления, второй выход - к первому входу арифметического устройства и входу регистра команд, нервый выход которого соединен с вторым входом устройства управлепия, второй выход - с первым входом регистра кодов арифметических операций, выход которого подключен к второму входу

арифметического устройства, третий вход которого соединеп с вторым В1 ходом устройства управления, отличающийся тем, что, с целью повышения быстродействия, в него введены регистр групп кодов, схема готовности арифметического устройства, схема разрешения запроса памяти, первый вход которой соединен с вторым выходом арифметического устройства, второй вход - с третьим выходом запоминающего устройства и с третьим входом устройства управления, четвертый вход которого подключен к выходу схемы разрешения запроса памяти, третий выход устройства управления соединен с вторым входом регистра кодов арифметических операций и с четвертым входом арифметического устройства, третий выход которого через регистр групн кодов соединен с пятым входом арифметического устройства, четвертым выходом подключенного к первому входу схемы готовности арифметического устройства, второй вход и выход которой соединен соответственно с четвертым выходом и пятым входом устройства управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Центральный процессор | 1975 |

|

SU608160A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Процессор цифровой вычислительной системы | 1971 |

|

SU475897A1 |

Авторы

Даты

1974-07-30—Публикация

1972-04-07—Подача